임베디드

저항 온도 감지기(RTD) 감지 시스템 최적화에 대한 두 번째 기사 , 우리는 RTD 시스템 최적화, 외부 구성 요소 선택 및 최종 RTD 시스템을 평가하는 방법을 탐구합니다.

RTD에 대한 3부작 시리즈의 첫 번째 기사에서는 온도 측정 문제, RTD 유형, 다양한 구성 및 RTD 구성 회로를 다뤘습니다. 두 번째 기사에서는 2선식, 3선식 및 4선식의 세 가지 RTD 구성에 대해 설명했습니다. 이 시리즈의 마지막 기사에서는 RTD 시스템 최적화, 외부 구성 요소 선택 및 최종 RTD 시스템을 평가하는 방법을 살펴보겠습니다.

RTD 시스템 최적화

시스템 설계자 문제를 살펴보면 RTD 애플리케이션 솔루션을 설계하고 최적화하는 것과 관련된 다양한 문제가 있습니다. 첫 번째 과제는 이전 섹션에서 논의한 센서 선택 및 연결 다이어그램입니다. 두 번째 과제는 ADC 구성, 여기 전류 설정, 이득 설정, 외부 구성 요소 선택을 포함하는 측정 구성이며 시스템 최적화를 보장하고 ADC 사양 내에서 작동합니다. 그리고 마지막으로 가장 중요한 문제는 목표 성능을 달성하는 방법과 전체 시스템 오류에 기여하는 오류 소스가 무엇인지입니다.

운 좋게도 개념에서 프로토타이핑에 이르기까지 RTD 측정 시스템을 설계하고 최적화하는 실습 솔루션을 제공하는 새로운 RTD_Configurator_and_Error_Budget_Calculator가 있습니다.

도구:

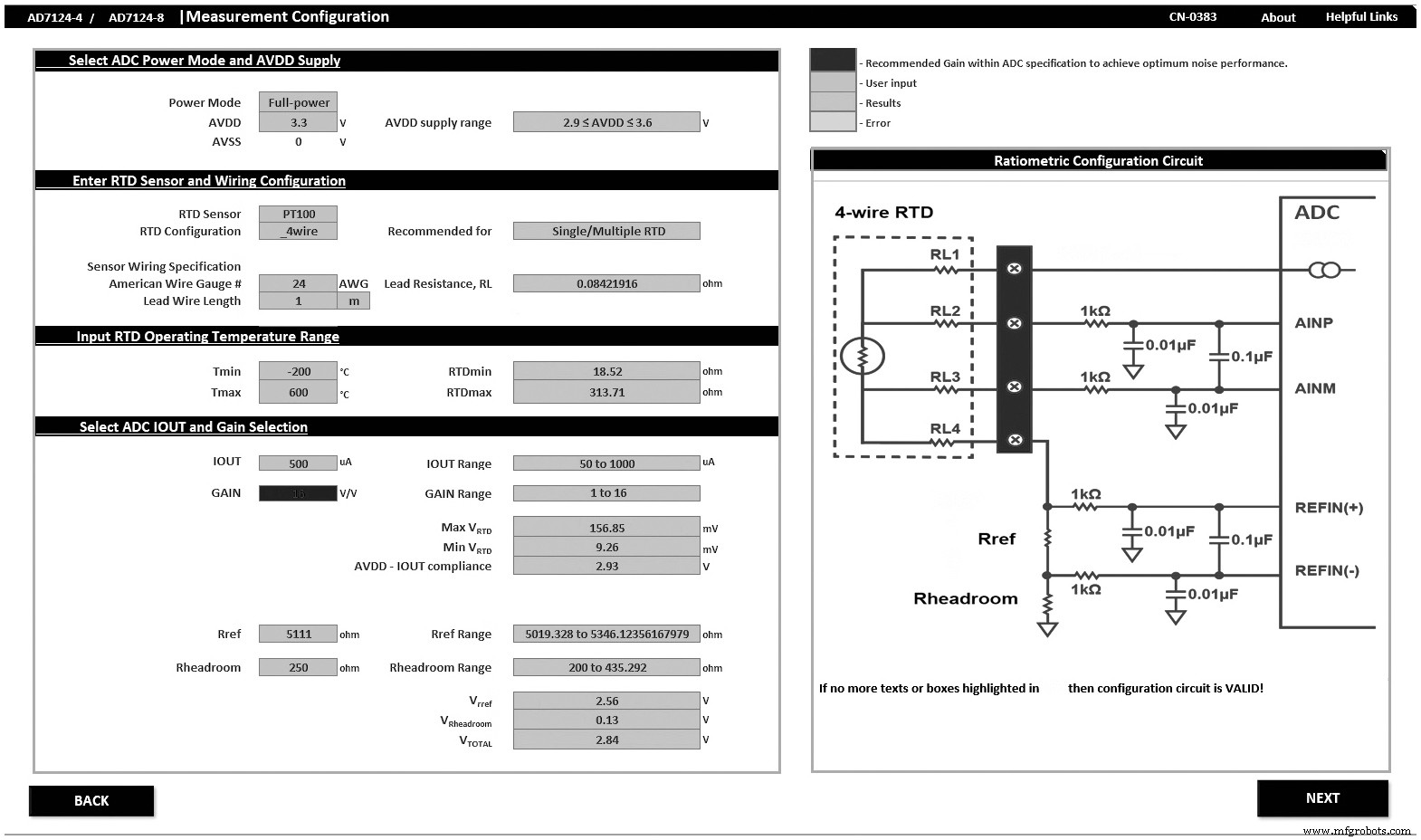

이 도구는 AD7124-4/AD7124-8을 중심으로 설계되었습니다. 이를 통해 고객은 여기 전류, 이득 및 외부 구성 요소와 같은 설정을 조정할 수 있습니다(그림 1). 최종 솔루션이 ADC 사양 내에 있는지 확인하기 위해 범위를 벗어난 조건을 나타냅니다.

전체 크기 이미지를 보려면 클릭하세요.

그림 1. RTD 구성기. (출처:Analog Devices)

여기 전류, 이득 및 외부 부품 선택

이상적으로는 훨씬 더 높은 출력 전압을 생성하고 ADC 입력 범위를 최대화하기 위해 더 높은 크기의 여기 전류를 선택하는 경향이 있습니다. 그러나 센서는 저항성이 있으므로 설계자는 큰 여기 전류 값의 전력 손실 또는 자체 발열 효과가 측정 결과에 영향을 미치지 않도록 해야 합니다. 시스템 설계자는 높은 여기 전류를 선택할 수 있습니다. 그러나 자체 발열을 최소화하려면 측정 사이에 여자 전류를 꺼야 합니다. 설계자는 시스템에 대한 타이밍 영향을 고려해야 합니다. 다른 접근 방식은 자체 발열을 최소화하는 더 낮은 여기 전류를 선택하는 것입니다. 이제 타이밍이 최소화되지만 설계자는 시스템 성능이 영향을 받는지 확인해야 합니다. 모든 시나리오는 RTD_Configurator_and_Error_Budget_Calculator를 통해 테스트할 수 있습니다. 이 도구를 사용하면 여기 전류, 이득 및 외부 구성 요소 선택의 균형을 맞춰 아날로그 입력 전압이 최적화되고 ADC 이득 및 속도를 조정하여 더 나은 분해능과 더 나은 시스템 성능을 제공할 수 있습니다. 낮은 오프셋 오류.

결과 필터 프로필을 이해하거나 전환 시기에 대해 더 깊이 이해하기 위해 VirtualEval 온라인 도구에서 이 세부 정보를 제공합니다.

시그마-델타 ADC의 ADC 입력 및 기준 입력은 모두 스위치드 커패시터 프론트 엔드에 의해 연속적으로 샘플링됩니다. 논의 중인 RTD 시스템의 경우 기준 입력도 외부 기준 저항에 의해 구동됩니다. 안티앨리어싱을 위해 시그마-델타 ADC의 아날로그 입력에 외부 RC 필터를 사용하는 것이 좋습니다. EMC 목적을 위해 시스템 설계자는 아날로그 입력과 기준 입력 모두에서 큰 R 및 C 값을 사용할 수 있습니다. RC 값이 크면 프런트 엔드 회로가 샘플링 순간 사이에 정착할 충분한 시간이 없기 때문에 측정 시 게인 오류가 발생할 수 있습니다. 아날로그 및 기준 입력을 버퍼링하면 이러한 이득 오류를 방지하고 무제한 R 및 C 값을 사용할 수 있습니다.

AD7124-4/AD7124-8의 경우 1보다 큰 내부 게인을 사용할 때 아날로그 입력 버퍼가 자동으로 활성화되고 PGA가 입력 버퍼 앞에 위치하므로 PGA가 레일 투 레일이므로 아날로그 입력이 또한 레일 투 레일입니다. 그러나 레퍼런스 버퍼의 경우 또는 아날로그 입력 버퍼가 활성화된 상태에서 1의 이득에서 ADC를 사용할 때 올바른 작동에 필요한 헤드룸이 충족되는지 확인해야 합니다.

Pt100의 신호는 낮은 수준입니다. 수백 mV 정도입니다. 최적의 성능을 위해 넓은 동적 범위의 ADC를 사용할 수 있습니다. 또는 이득 단계를 사용하여 ADC에 적용하기 전에 신호를 증폭할 수 있습니다. AD7124-4/AD7124-8은 1 ~ 128의 이득을 지원하므로 광범위한 여기 전류에 대해 최적화된 설계가 가능합니다. PGA 이득의 여러 허용 옵션을 통해 설계자는 여기 전류 값 대 이득, 외부 구성 요소 및 성능을 절충할 수 있습니다. RTD 구성 도구는 선택한 RTD 센서와 함께 새 여자 전류 값을 사용할 수 있는지 여부를 나타냅니다. 정밀 기준 저항과 기준 헤드룸 저항에 대한 적절한 값도 제안됩니다. 이 도구는 ADC가 사양 내에서 사용되도록 보장하므로 구성을 지원할 수 있는 이득이 표시됩니다. AD7124 여기 전류는 출력 규정을 준수합니다. 즉, 여기 전류를 제공하는 핀의 전압에는 AVDD의 헤드룸이 필요합니다. 이 도구는 또한 이 규정 준수 사양을 충족하는지 확인합니다.

RTD 도구를 사용하면 시스템 설계자가 ADC 및 RTD 센서의 작동 한계 내에서 시스템을 보장할 수 있습니다. 기준 저항과 같은 외부 구성 요소의 정확도와 시스템 오류에 대한 기여는 나중에 설명합니다.

필터링 옵션(아날로그 및 디지털 50Hz/60Hz 제거)

앞서 논의한 바와 같이 시그마-델타 변환기에는 앤티앨리어싱 필터를 사용하는 것이 좋습니다. 내장 필터가 디지털이므로 주파수 응답은 샘플링 주파수 주변에 반영됩니다. 변조기 주파수와 이 주파수의 배수에서 간섭을 적절히 감쇠하려면 앤티앨리어싱 필터링이 필요합니다. 시그마-델타 컨버터가 아날로그 입력을 오버샘플링하기 때문에 앤티앨리어싱 필터의 설계가 크게 단순화되고 간단한 단극 RC 필터만 있으면 됩니다.

최종 시스템이 현장에서 사용될 때 시스템이 작동하는 환경의 노이즈 또는 간섭을 처리하는 것은 특히 허용 가능한 산업 자동화, 계측, 프로세스 제어 또는 전력 제어와 같은 애플리케이션 공간에서 상당히 어려울 수 있습니다. 소음에 대한 동시에 이웃 구성 요소에 대한 소음이 발생하지 않아야 합니다. 노이즈, 과도 현상 또는 기타 간섭 소스는 시스템 정확도와 해상도에 영향을 줄 수 있습니다. 시스템이 주 전원에서 전원을 공급받는 경우에도 간섭이 발생할 수 있습니다. 주전원 주파수는 유럽에서는 50Hz 및 그 배수, 미국에서는 60Hz 및 그 배수에서 발생하므로 측온저항체 시스템을 설계할 때 50Hz/60Hz 제거 필터 회로를 고려해야 합니다. 많은 시스템 설계자는 50Hz와 60Hz를 동시에 거부하는 범용 시스템을 설계하기를 원합니다.

AD7124-4/AD7124-8을 포함한 대부분의 저대역폭 ADC는 50Hz/60Hz에서 노치를 설정하도록 프로그래밍할 수 있는 다양한 디지털 필터링 옵션을 제공합니다. 선택한 필터 옵션은 출력 데이터 속도, 안정화 시간, 50Hz 및 60Hz 제거에 영향을 줍니다. 여러 채널이 활성화된 경우 채널이 전환될 때마다 변환을 생성하는 데 안정화 시간이 필요합니다. 따라서 안정 시간이 더 긴 필터 유형(즉, sinc4 또는 sinc3)을 선택하면 전체 처리율이 낮아집니다. 이 경우 포스트 필터 또는 FIR 필터는 낮은 정착 시간에서 합리적인 동시 50Hz/60Hz 제거를 제공하여 처리율을 높이는 데 유용합니다.

전력 고려사항

시스템의 현재 소비 또는 전력 예산 할당은 최종 애플리케이션에 크게 의존합니다. AD7124-4/AD7124-8에는 성능, 속도 및 전력 간의 균형을 허용하는 세 가지 전력 모드가 포함되어 있습니다. 휴대용 또는 원격 애플리케이션의 경우 저전력 구성 요소 및 구성을 사용해야 하며 일부 산업 자동화 애플리케이션의 경우 전체 시스템에 4mA ~ 20mA 루프에서 전원이 공급되므로 최대 4mA의 전류 예산만 허용됩니다. 이러한 유형의 애플리케이션의 경우 장치를 중간 또는 저전력 모드로 프로그래밍할 수 있습니다. 속도는 훨씬 낮지만 ADC는 여전히 고성능을 제공합니다. 응용 프로그램이 주 전원에서 전원을 공급받는 프로세스 제어인 경우 훨씬 더 높은 전류 소비가 허용되므로 장치를 최대 전력 모드로 프로그래밍할 수 있으며 이 시스템은 훨씬 더 높은 출력 데이터 속도와 향상된 성능을 달성할 수 있습니다.

오류 소스 및 보정 옵션

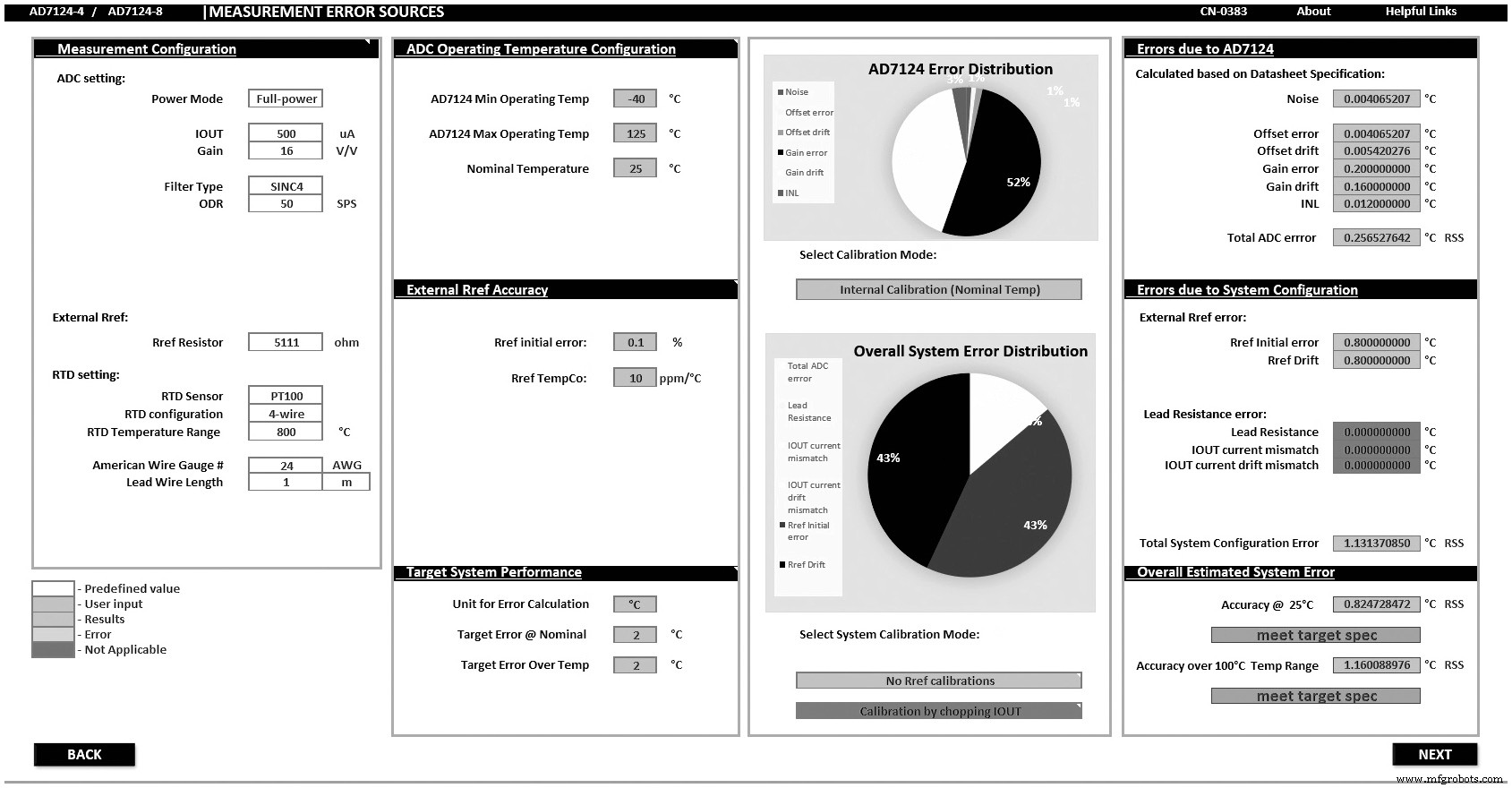

필요한 시스템 구성을 파악한 후 다음 단계는 ADC와 관련된 오류 및 시스템 오류를 추정하는 것입니다. 이는 시스템 설계자가 프런트 엔드 및 ADC 구성이 전체 목표 정확도와 성능을 충족하는지 이해하는 데 도움이 됩니다. RTD_Configurator_and_Error_Budget_Calculator를 사용하면 사용자가 최적의 성능을 위해 시스템 구성을 수정할 수 있습니다. 예를 들어, 그림 2는 모든 오류의 요약을 보여줍니다. 시스템 오류 원형 차트는 외부 기준 저항기의 초기 정확도와 온도 계수가 전체 시스템 오류의 주요 오류 원인임을 나타냅니다. 따라서 더 높은 정확도와 더 나은 온도 계수를 가진 외부 기준 저항을 사용하는 것을 고려하는 것이 중요합니다.

전체 크기 이미지를 보려면 클릭하세요.

그림 2. RTD 오류 소스 계산기. (출처:Analog Devices)

ADC로 인한 오류는 전체 시스템 오류의 가장 중요한 오류 원인이 아닙니다. 그러나 ADC의 오류 기여는 AD7124-4/AD7124-8의 내부 교정 모드를 사용하여 더 줄일 수 있습니다. ADC 이득 및 오프셋 오류를 제거하기 위해 전원 공급 또는 소프트웨어 초기화 시 내부 교정이 권장됩니다. 이러한 보정은 외부 회로에 의해 생성된 오류를 제거하지 않는다는 점에 유의하십시오. 그러나 ADC는 시스템 오프셋 및 이득 오류를 최소화할 수 있도록 시스템 교정도 지원할 수 있지만, 이는 추가 비용을 추가할 수 있고 대부분의 애플리케이션에 필요하지 않을 수 있습니다.

오류 감지

혹독한 환경이나 안전이 우선인 애플리케이션의 경우 진단이 산업 요구 사항의 일부가 되고 있습니다. AD7124-4/AD7124-8에 내장된 진단 기능은 진단을 구현하기 위한 외부 부품의 필요성을 줄여줌으로써 더 작고 간소화된 시간 및 비용 절감 솔루션을 제공합니다.

진단에는 다음이 포함됩니다.

이러한 진단은 보다 강력한 솔루션으로 이어집니다. 일반적인 3선식 RTD 애플리케이션의 FMEDA(고장 모드, 영향 및 진단 분석)는 IEC 61508에 따라 90%보다 큰 SFF(안전 고장률)를 보여줍니다.

RTD 시스템 평가

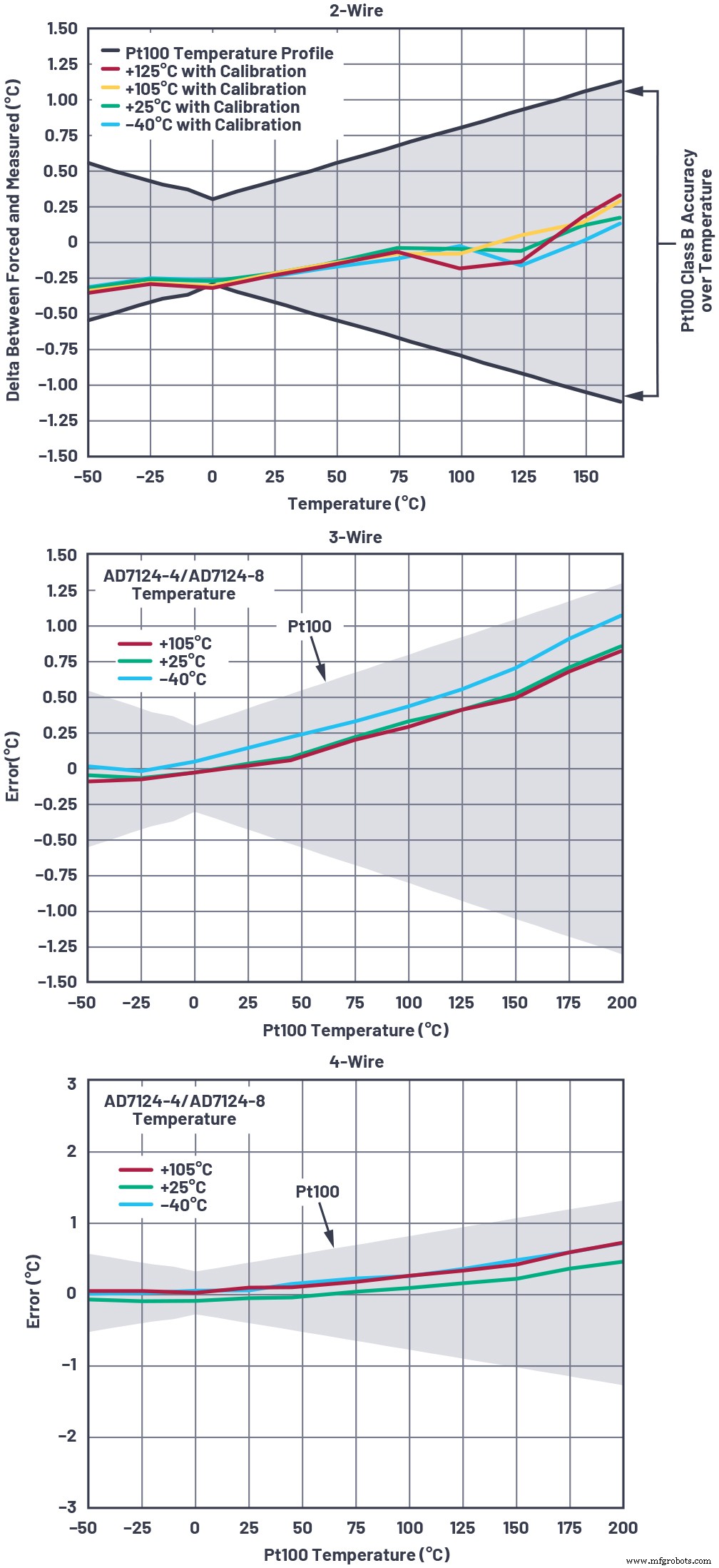

그림 3은 회로 노트 CN-0383의 일부 측정 데이터를 보여줍니다. 이 측정 데이터는 2선, 3선 및 4선 RTD에 대한 데모 모드가 포함된 AD7124-4/AD7124-8 평가 기판으로 캡처되었으며 해당 섭씨 온도 값을 계산했습니다. 결과에 따르면 2-와이어 RTD 구현은 오류 경계의 하한에 더 가까운 오류를 제공하는 반면 3-와이어 또는 4-와이어 RTD 구현은 허용된 한계 내에 있는 전체 오류를 가지고 있습니다. 2-와이어 측정에서 더 높은 오류는 앞서 설명한 리드 저항 오류로 인한 것입니다.

전체 크기 이미지를 보려면 클릭하세요.

그림 3. 25SPS의 저전력 모드에서 2/3/4와이어 RTD 온도 정확도 측정 포스트 필터. (출처:Analog Devices)

이러한 예에서 보여 주는 것은 위의 RTD 지침을 따르면 AD7124-4/AD7124-8과 같은 ADI의 저대역폭 시그마-델타 ADC와 함께 사용할 때 높은 정확도, 고성능 설계로 이어진다는 것입니다. 회로 노트(CN-0383)는 시스템 설계자가 프로토타이핑을 신속하게 수행하는 데 도움이 되는 참조 설계 역할도 합니다. 평가 보드를 통해 사용자는 각 샘플 구성 데모 모드를 사용할 수 있는 시스템 성능을 평가할 수 있습니다. 앞으로 AD7124-4/AD7124-8 제품 페이지에서 제공되는 ADI 생성 샘플 코드를 사용하여 다양한 RTD 구성을 위한 펌웨어를 쉽게 개발할 수 있습니다.

AD7124-4/AD7124-8과 같은 시그마-델타 아키텍처를 사용하는 ADC는 50Hz/60Hz 제거 및 넓은 공통 모드 범위와 같은 문제를 해결하기 때문에 RTD 측정 애플리케이션에 적합합니다. 아날로그 및 가능한 기준 입력. 또한 RTD 시스템 설계에 필요한 모든 기능을 포함하는 고도로 통합되어 있습니다. 또한 교정 기능 및 내장형 진단과 같은 향상된 기능을 제공합니다. 이 수준의 통합은 전체 시스템 자료 또는 생태계와 함께 개념에서 프로토타입에 이르기까지 전체 시스템 설계, 비용 및 설계 주기를 단순화합니다.

시스템 설계자의 여정을 용이하게 하기 위해 온라인 도구 VirtualEval, 평가 보드 하드웨어 및 소프트웨어, CN-0383과 함께 RTD_Configurator_and_Error_Budget_Calculator 도구를 사용하여 연결 문제 및 전체 오류 예산과 같은 다양한 문제를 해결할 수 있습니다. 사용자가 디자인의 다음 단계로 이동할 수 있습니다.

결론

이 기사에서는 RTD 온도 측정 시스템을 설계하는 것이 어려운 다단계 프로세스임을 보여주었습니다. 다양한 센서 구성, ADC 선택 및 최적화와 이러한 결정이 전체 시스템 성능에 미치는 영향에 대한 선택이 필요합니다. ADI RTD_Configurator_and_Error_Budget_Calculator 도구는 온라인 도구 VirtualEval, 평가 보드 하드웨어 및 소프트웨어, CN-0383과 함께 연결 및 전반적인 오류 예산 문제를 해결하여 프로세스를 간소화합니다.

젤리니 로드리게스 Precision Converter Technology Group 내 Analog Devices의 애플리케이션 엔지니어입니다. 그녀는 DC 측정을 위한 정밀 시그마-델타 ADC에 중점을 두고 있습니다. 2012년 ADI에 입사하여 2011년 San Sebastian College-Recoletos de Cavite에서 전자 공학 학사 학위를 취득했습니다. 이메일은 [email protected]입니다.

젤리니 로드리게스 Precision Converter Technology Group 내 Analog Devices의 애플리케이션 엔지니어입니다. 그녀는 DC 측정을 위한 정밀 시그마-델타 ADC에 중점을 두고 있습니다. 2012년 ADI에 입사하여 2011년 San Sebastian College-Recoletos de Cavite에서 전자 공학 학사 학위를 취득했습니다. 이메일은 [email protected]입니다.  메리 매카시 Analog Devices의 애플리케이션 엔지니어입니다. 그녀는 1991년 ADI에 입사하여 아일랜드 코크에 있는 Linear and Precision Technology Applications Group에서 정밀 시그마-델타 변환기에 중점을 두고 일하고 있습니다. Mary는 1991년 University College Cork에서 전자 및 전기 공학 학사 학위를 취득했습니다. 연락처는 [email protected]입니다.

메리 매카시 Analog Devices의 애플리케이션 엔지니어입니다. 그녀는 1991년 ADI에 입사하여 아일랜드 코크에 있는 Linear and Precision Technology Applications Group에서 정밀 시그마-델타 변환기에 중점을 두고 일하고 있습니다. Mary는 1991년 University College Cork에서 전자 및 전기 공학 학사 학위를 취득했습니다. 연락처는 [email protected]입니다. 관련 콘텐츠:

더 많은 Embedded를 보려면 Embedded의 주간 이메일 뉴스레터를 구독하세요.

임베디드

린(Lean) 제조는 적시에 제품을 효율적으로 생성하기 위해 프로세스를 조정하는 것을 포함합니다. 너무 많이 또는 너무 적게 생산하면 낭비가 발생하거나 고객이 불만을 갖게 됩니다. 린(lean) 생산 라인에 맞출 때 전지 설계는 이 목표를 달성하기 위한 중요한 단계입니다. 작업실을 디자인하거나 선택하기 전에 고려해야 할 사항은 다음과 같습니다. 작업 셀은 생산 라인의 어느 부분에 사용됩니까? 어떤 신청이 수행됩니까? 기계 또는 영역에서 부품을 어떻게 로드 및 언로드합니까? 어느 방향으로 움직일까요? 얼마나

여러 면에서 주어진 컨베이어 시스템의 품질을 결정하는 주요 요인은 컨베이어 자체가 아니지만 컨베이어는 컨베이어의 높이 및 정렬 제어를 지원합니다. 일부 프로젝트에는 간단한 바닥 지지대 배열만 필요할 수 있지만 다른 응용 프로그램에는 바닥 지지대, 행거 및 벽 브래킷의 조합이 필요할 수 있습니다. 작업에 맞게 사용자 지정 컨베이어 시스템에서 가능한 최고의 효율성을 얻으려면 당면한 작업에 가장 적합하도록 맞춤화된 컨베이어 지지대와 일치해야 합니다. 곡물 엘리베이터와 채석장에 대한 최상의 컨베이어 지원 설정은 동일하지 않을 수 있습니