산업기술

카운터와 같은 시프트 레지스터는 순차 논리의 한 형태입니다. .

순차 논리는 조합 논리와 달리 현재 입력뿐만 아니라 이전 이력의 영향도 받습니다.

즉, 순차 논리는 과거 이벤트를 기억합니다.

시프트 레지스터는 디지털 신호 또는 파형의 이산 지연을 생성합니다.

시계에 동기화된 파형 , 반복되는 구형파는 "n"만큼 지연됩니다. 개별 시계 시간, 여기서 "n" 시프트 레지스터 단계의 수입니다.

따라서 4단계 시프트 레지스터는 "데이터 입력"을 "데이터 출력"까지 4클럭 지연시킵니다.

시프트 레지스터의 단계는 지연 단계입니다. , 일반적으로 “D”를 입력합니다. 슬리퍼 또는 “JK” 입력 슬리퍼.

이전에는 매우 긴(수백 단계) 시프트 레지스터가 디지털 메모리 역할을 했습니다.

이 구식 응용 프로그램은 초기 컴퓨터 메모리로 사용된 음향 수은 지연 라인을 연상시킵니다.

미터에서 킬로미터의 거리에 걸친 직렬 데이터 전송은 시프트 레지스터를 사용하여 병렬 데이터를 직렬 형식으로 변환합니다.

직렬 데이터 통신은 많은 느린 병렬 데이터 와이어를 단일 직렬 고속 회로로 대체합니다.

수십 센티미터의 짧은 거리에 대한 직렬 데이터는 시프트 레지스터를 사용하여 마이크로프로세서 안팎으로 데이터를 가져옵니다.

아날로그-디지털 변환기, 디지털-아날로그 변환기, 디스플레이 드라이버 및 메모리를 포함한 수많은 주변 장치는 시프트 레지스터를 사용하여 회로 기판의 배선 양을 줄입니다.

일부 특수 카운터 회로는 실제로 시프트 레지스터를 사용하여 반복되는 파형을 생성합니다.

피드백의 도움으로 더 긴 시프트 레지스터는 패턴을 생성하여 무작위 노이즈, 의사 노이즈처럼 보이도록 합니다. .

기본 시프트 레지스터는 다음 유형에 따라 구조별로 분류됩니다.

<울>

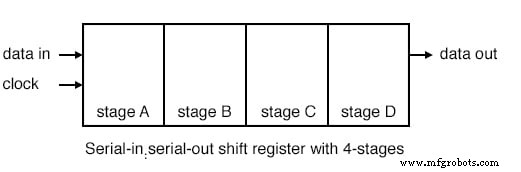

위에서 우리는 4단계 길이의 직렬 입력/직렬 출력 시프트 레지스터의 블록 다이어그램을 보여줍니다.

입력의 데이터는 입력에서 시프트 레지스터의 출력까지 4 클럭 주기만큼 지연됩니다.

위의 "data in"에 있는 데이터는 A 단계에 있습니다. 첫 번째 클럭 펄스 이후에 출력됩니다. 두 번째 펄스 단계 이후 A 데이터가 B 단계로 전송됩니다. 출력하고 "data in"은 A 단계로 전송됩니다. 산출. 세 번째 시계 후 C 단계 B 단계로 대체됨; 스테이지 B A 단계로 대체됨; 단계 A는 "데이터 입력"으로 대체됩니다.

네 번째 시계 이후에 "data in"에 원래 존재하는 데이터는 D 단계에 있습니다. , "출력".

"선입" 데이터는 "데이터 입력"에서 "데이터 출력"으로 이동하므로 "선입 선출"입니다.

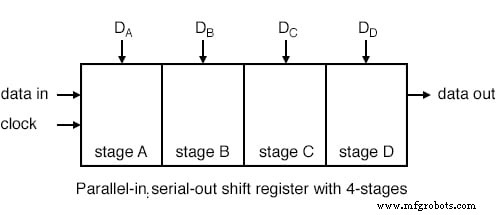

데이터는 병렬 입력/직렬 출력 시프트 레지스터의 모든 단계에 한 번에 로드됩니다.

그런 다음 데이터는 클록 펄스에 의해 "데이터 출력"을 통해 이동됩니다. 4단 시프트 레지스터가 위에 나와 있으므로 모든 데이터를 시프트하려면 4개의 클록 펄스가 필요합니다.

위의 다이어그램에서 D 단계 데이터는 첫 번째 클럭 펄스까지 "데이터 출력"에 존재합니다. 스테이지 C 데이터는 첫 번째 클럭과 두 번째 클럭 펄스 사이의 "데이터 출력"에 표시됩니다. 스테이지 B 데이터는 두 번째 클록과 세 번째 클록 사이에 존재합니다. 및 단계 A 데이터는 세 번째와 네 번째 시계 사이에 표시됩니다.

네 번째 클럭 펄스 이후에 "데이터 입력"의 연속 비트는 4개의 클럭 펄스가 지연된 후 시프트 레지스터의 "데이터 출력"에 나타나야 합니다.

4개의 스위치가 DA에 연결된 경우 DD를 통해 , 상태는 단 하나의 데이터 핀과 클록 핀을 사용하여 마이크로프로세서로 읽을 수 있습니다.

더 많은 스위치를 추가하면 추가 핀이 필요하지 않으므로 이 접근 방식은 많은 입력에 적합해 보입니다.

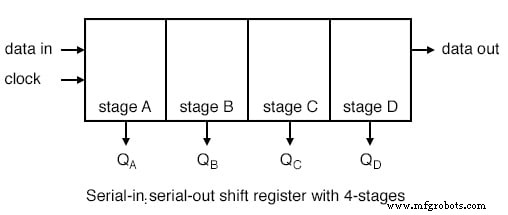

위에서 4개의 데이터 비트는 "데이터 입력"에서 4개의 클럭 펄스만큼 이동하고 QA에서 사용할 수 있습니다. QD를 통해 LED, 램프, 릴레이 드라이버 및 혼과 같은 외부 회로를 구동하는 데 사용됩니다. 첫 번째 시계 이후 "data in"의 데이터는 QA에 나타납니다. .

두 번째 시계 이후에는 이전 QA 데이터는 QB에 나타납니다.; QA "data in"에서 다음 데이터를 수신합니다. 세 번째 시계 이후에는 QB 데이터는 QC에 있습니다. .

네 번째 시계 이후에는 QC 데이터는 QD에 있습니다. . 이 단계는 "data in"에 처음 존재하는 데이터를 포함합니다. 시프트 레지스터는 이제 4개의 데이터 비트를 포함해야 합니다.

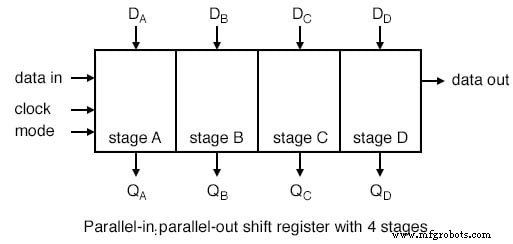

병렬 입력/병렬 출력 시프트 레지스터는 병렬 입력 직렬 출력 시프트 레지스터의 기능과 직렬 입력 병렬 출력 시프트 레지스터의 기능을 결합하여 범용 시프트 레지스터를 생성합니다.

"무엇이든 할 수 있는" 시프터에는 대가가 따릅니다. I/O(입력/출력) 핀 수가 증가하면 패키징할 수 있는 단계 수가 줄어들 수 있습니다.

DA에 제시된 데이터 DD를 통해 레지스터에 병렬로 로드됩니다.

이 데이터는 QA QD를 통해 클럭 입력에 제공된 펄스 수만큼 이동될 수 있습니다.

이동된 데이터는 QA에서 확인할 수 있습니다. QD를 통해 .

둘 이상의 입력일 수 있는 "모드" 입력은 DA에서 데이터의 병렬 로드를 제어합니다. DD를 통해 , 데이터 이동 및 이동 방향.

데이터를 왼쪽이나 오른쪽으로 이동시키는 시프트 레지스터가 있습니다.

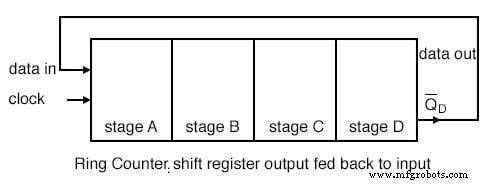

시프트 레지스터의 직렬 출력이 직렬 입력에 연결된 경우 클록 펄스가 존재하는 한 데이터는 링 주위에서 영구적으로 이동될 수 있습니다.

위와 같이 피드백되기 전에 출력이 반전되면 초기 데이터를 "링 카운터"에 로드하는 것에 대해 걱정할 필요가 없습니다.

관련 워크시트:

<울>산업기술

Li-Fi란 무엇입니까? Li-Fi(빛 충실도라고도 함)는 장치 간에 데이터를 무선으로 전송하는 기술입니다. Li-Fi는 빛을 데이터 전송 매체로 사용합니다. LED 램프는 바이너리 코드를 생성하기 위해 일정한 간격으로 조명을 켜고 끄는 방식으로 데이터를 인코딩하는 데 사용되는 소스입니다. 이것은 수신기가 결정하는 다른 쪽 끝으로 전송됩니다. Li-Fi는 간단한 LED 전구를 사용하여 데이터를 전송하기 때문에 데이터 전송에 엄청난 잠재력을 가지고 있습니다. Li-Fi 시스템의 구성요소: Li-Fi 시스템에는 두 가지 주요 구

소개 안녕하세요 여러분, 저는 Strton 런타임과 IEC61850 표준 주변의 프로그래밍 환경에 대해 이야기하겠습니다. 이 런타임은 에너지 분야에서 완전히 진화한 프로토콜인 표준 에디션 2를 따릅니다. 과거에 피닉스컨택트는 PCWORX용 IEC61850 스택과 이전 PLC 제품군(AXC1050)을 개발했지만 오늘날에는 매장에서 사용할 수 있는 이 애플리케이션 덕분에 PLCNextEngineer와 IEC61850 표준을 결합할 수 있습니다. 또한 이 런타임은 61850 클라이언트를 구성할 수 있는 큰 이점을 제공