산업기술

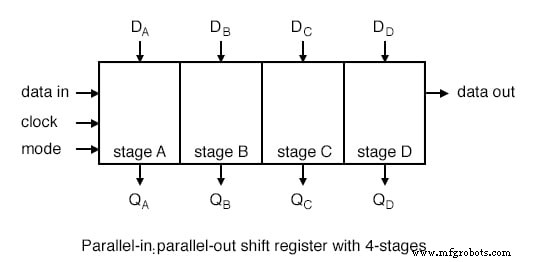

병렬 입력/병렬 출력 시프트 레지스터의 목적은 병렬 데이터를 가져와서 시프트한 다음 아래와 같이 출력하는 것입니다.

범용 시프트 레지스터는 병렬 입력/병렬 출력 기능 외에 모든 작업을 수행하는 장치입니다.

위에서 우리는 DA의 병렬 입력/병렬 출력 시프트 레지스터에 4비트의 데이터를 적용합니다. DB DC DD . 다중 입력일 수 있는 모드 제어는 병렬 로딩과 이동을 제어합니다.

모드 제어는 일부 실제 장치에서 이동 방향을 제어할 수도 있습니다. 데이터는 각 클록 펄스에 대해 한 비트 위치로 이동합니다.

이동된 데이터는 출력 QA에서 사용할 수 있습니다. QB QC QD . "데이터 입력" 및 "데이터 출력"은 여러 단계의 계단식으로 제공됩니다.

그러나 위에서는 오른쪽 시프팅에 대해서만 데이터를 계단식으로 배열할 수 있습니다. 위의 "data in" 및 "data out"이라는 한 쌍의 왼쪽 포인팅 신호를 추가하여 왼쪽 시프트 데이터의 계단식 배열을 수용할 수 있습니다.

오른쪽 시프팅 병렬 입력/병렬 출력 시프트 레지스터의 내부 세부 정보는 아래와 같습니다.

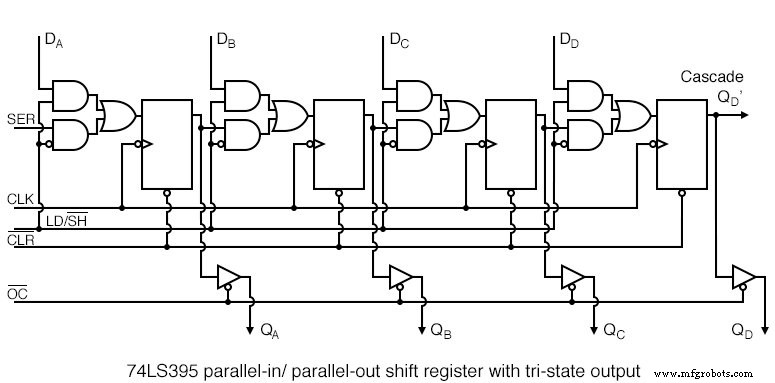

3상태 버퍼는 병렬 입력/병렬 출력 시프트 레지스터에 꼭 필요한 것은 아니지만 아래 표시된 실제 장치의 일부입니다.

74LS395는 가상의 오른쪽 시프팅 병렬 입력/병렬 출력 시프트 레지스터의 개념과 매우 밀접하게 일치하므로 위의 데이터 시트 세부 정보의 지나치게 단순화된 버전을 사용합니다.

자세한 내용은 이 장의 뒷부분에 나오는 전체 데이터 시트에 대한 링크를 참조하십시오.

LD/SH' FF에 대한 데이터 입력에서 AND-OR 멀티플렉서를 제어합니다. LD/SH'=1인 경우 , 상위 4개의 AND 게이트가 활성화되어 병렬 입력 DA를 적용할 수 있습니다. DB DC DD 4개의 FF 데이터 입력으로.

4개의 FF의 클록 입력에서 인버터 버블을 확인하십시오. 이것은 74LS395가 음으로 가는 클럭에서 데이터를 기록한다는 것을 나타냅니다. 이는 하이에서 로우로의 전환입니다.

4비트의 데이터는 DA에서 병렬로 클럭됩니다. DB DC DD QA로 QB QC QD 다음 음수 시계에. 이 "실제 부분"에서 OC' 내부 FF에서만이 아니라 실제 출력 핀에서 데이터를 사용할 수 있어야 하는 경우 낮아야 합니다.

LD/SH'=0인 경우 이전에 로드된 데이터가 1비트 위치로 오른쪽으로 이동될 수 있습니다. 이어지는 음의 시계 가장자리에 대해.

4개의 클럭은 4비트 시프트 레지스터에서 데이터를 완전히 시프트합니다. 기기가 QD에서 계단식으로 연결되지 않으면 데이터가 손실됩니다. ' SER으로 다른 장치의.

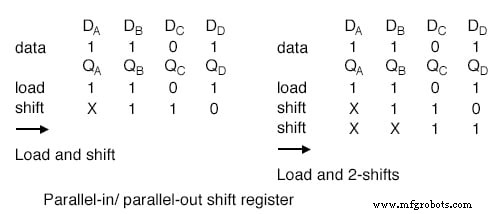

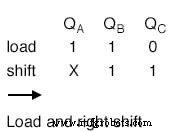

위의 데이터 패턴은 DA 입력에 표시됩니다. DB DC DD . 패턴이 QA에 로드됩니다. QB QC QD . 그런 다음 오른쪽으로 한 비트 이동합니다.

수신 데이터는 X로 표시됩니다. , 그것은 우리가 그것이 무엇인지 모른다는 것을 의미합니다. 입력(SER ) 예를 들어 어떤 데이터(0 )이(가) 이동되었습니다.

또한 두 위치만큼 오른쪽으로 이동하므로 두 개의 시계가 필요합니다.

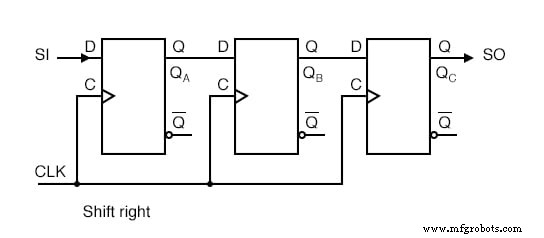

위의 그림은 데이터의 오른쪽 이동과 관련된 하드웨어에 대한 참조 역할을 합니다.

따라야 할 더 복잡한 수치와 비교하는 것을 제외하고는 이 수치로 귀찮게 하기에는 너무 간단합니다.

데이터의 오른쪽 이동은 이전 오른쪽 시프터를 참조하기 위해 위에 제공됩니다.

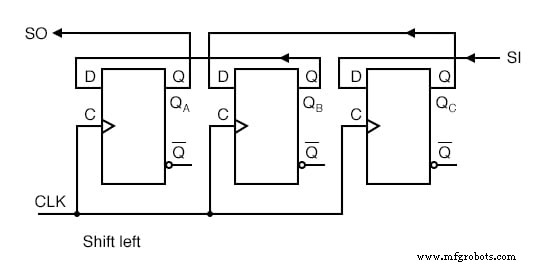

왼쪽으로 이동해야 하는 경우 FF를 다시 배선해야 합니다. 이전 오른쪽 쉬프터와 비교하십시오. 또한 SI 그리고 SO 되돌려졌습니다. SI QC로 이동 . QC QB로 이동 . QB QA로 이동 . 질문A SO에 나뭇잎 다른 시프터 SI로 캐스케이드될 수 있는 연결 . 이 왼쪽 시프트 시퀀스는 오른쪽 시프트 시퀀스에서 거꾸로입니다.

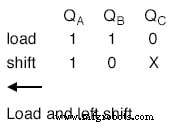

위에서 동일한 데이터 패턴을 왼쪽으로 1비트 이동합니다.

위의 "왼쪽으로 이동" 그림에는 한 가지 문제가 있습니다. 이를 위한 시장은 없습니다. 아무도 왼쪽 시프트 부품을 제조하지 않습니다.

한 방향으로 이동하는 "실제 장치"는 다른 방향으로 이동하기 위해 외부적으로 배선될 수 있습니다. 또는 한 방향으로만 이동하는 장치의 맥락에서 좌우가 없다고 해야 할까요?

그러나 제어 라인의 명령에 따라 왼쪽 또는 오른쪽으로 이동하는 장치에 대한 시장이 있습니다. 물론 왼쪽과 오른쪽이 그 맥락에서 유효합니다.

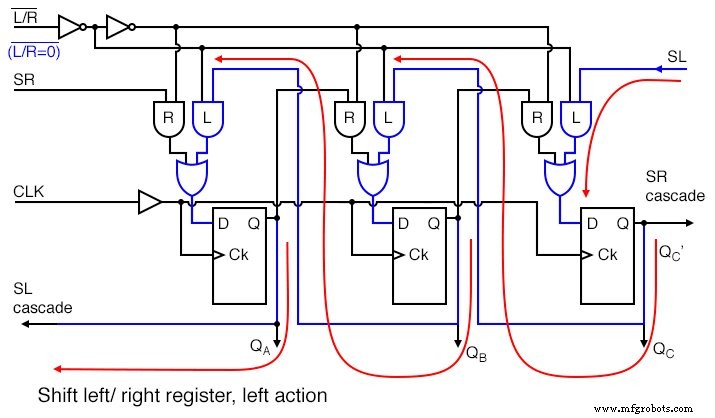

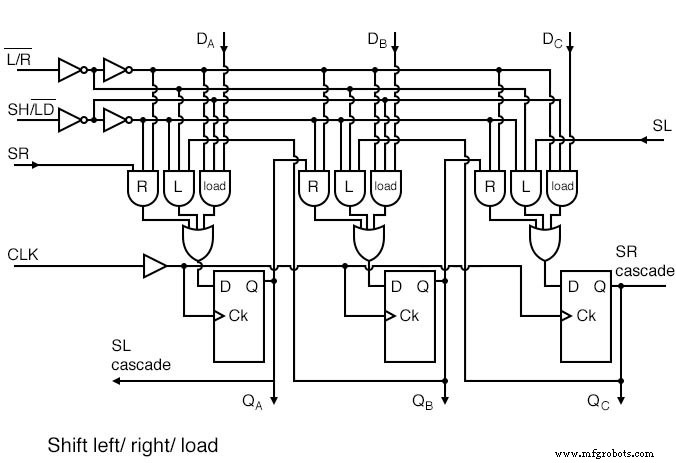

위에 있는 것은 L'/R의 제어 하에 어느 방향으로든 이동할 수 있는 가상의 시프트 레지스터입니다. .

L'/R=1로 설정됩니다. 법선 방향을 오른쪽으로 이동합니다. L'/R=1 R 라벨이 붙은 멀티플렉서 AND 게이트 활성화 .

이렇게 하면 시계가 적용될 때 데이터가 화살표로 표시된 경로를 따라갈 수 있습니다. 연결 경로는 위의 "너무 단순함" "오른쪽으로 이동" 그림과 같습니다.

SR에서 데이터 이동 , QA로 , QB로 , QC로 , 여기서 SR 캐스케이드에서 출발합니다. . 이 핀은 SR을 구동할 수 있습니다. 다른 기기의 오른쪽에 있습니다.

L'/R을 변경하면 어떻게 될까요? L'/R=0으로 ?

L'/R=0 , 멀티플렉서 AND 게이트 L 위의 "왼쪽으로 이동" 그림과 동일한 화살표로 표시된 경로를 생성합니다.

SL에서 데이터 이동 , QC로 , QB로 , QA로 , 여기서 SL 캐스케이드에서 출발합니다. . 이 핀은 SL을 구동할 수 있습니다. 다른 장치의 왼쪽에 있습니다.

"좌/우 시프트 레지스터"를 설명하는 위의 두 그림의 주요 장점은 단순성입니다.

왼쪽 오른쪽 컨트롤의 조작 L'/R=0 따라하기 쉽습니다. 상업적인 부분은 섹션 제목이 암시하는 병렬 데이터 로딩이 필요합니다. 이것은 아래 그림과 같습니다.

이제 L'/R을 통해 왼쪽과 오른쪽으로 이동할 수 있습니다. , SH/LD'를 추가하겠습니다. , shift/load 및 입력 DA에서 데이터의 병렬 로드를 제공하기 위해 "load"라는 레이블이 붙은 AND 게이트 DB DC .

SH/LD'=0일 때 , AND 게이트 R 및 L 비활성화되고 AND 게이트 "로드"가 데이터 DA를 전달하도록 활성화됨 DB DC FF 데이터 입력에. 다음 시계 CLK 데이터를 QA로 클럭합니다. QB QC .

동일한 데이터가 존재하는 한 다음 클럭에 다시 로드됩니다. 그러나 하나의 클럭에 대해서만 존재하는 데이터는 데이터 입력에 더 이상 존재하지 않을 때 출력에서 손실됩니다.

한 가지 솔루션은 하나의 클럭에 데이터를 로드한 다음 다음 4개 클럭으로 이동하는 것입니다. 이 문제는 멀티플렉서에 다른 AND 게이트를 추가하여 74ALS299에서 해결됩니다.

SH/LD'인 경우 SH/LD'=1로 변경됨 , "로드"라고 표시된 AND 게이트가 비활성화되어 왼쪽/오른쪽 제어 L'/R을 허용합니다. L의 이동 방향을 설정하려면 또는 R 그리고 게이트. 이동은 앞의 그림과 같습니다.

실행 가능한 통합 장치를 생산하는 데 필요한 유일한 것은 74ALS299에 대해 언급된 대로 멀티플렉서에 네 번째 AND 게이트를 추가하는 것입니다.

이것은 해당 부분에 대한 다음 섹션에 표시됩니다.

Texas Instruments에서 제공하는 집적 회로로 제공되는 직렬 입력/병렬 출력 시프트 레지스터를 자세히 살펴보겠습니다.

전체 장치 데이터 시트를 보려면 링크를 따르십시오.

<울> <리>SN74LS395A 병렬 입력/병렬 출력 4비트 시프트 레지스터

<리>SN74ALS299 병렬 입력/병렬 출력 8비트 범용 시프트 레지스터

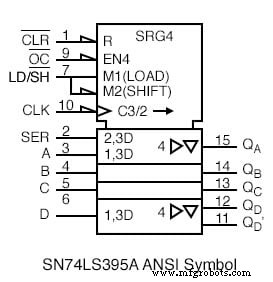

우리는 이미 SN74LS395A의 내부 세부 사항을 살펴보았습니다. 위의 그림, 3상태 출력이 있는 74LS395 병렬 입력/병렬 출력 시프트 레지스터를 참조하십시오.

바로 위에는 74LS395의 ANSI 기호가 있습니다.

SRG4로 표시된 대로 4비트만 사용하는 이유 위에? 제어 및 전원 핀 외에 병렬 입력과 병렬 출력이 모두 있으면 16핀 DIP(듀얼 인라인 패키지)에서 더 이상 I/O(입력/출력) 비트를 허용하지 않습니다.

R 시프트 레지스터 단계가 입력 CLR'에 의해 재설정되었음을 나타냅니다. (입력 시 활성 낮은 반전 반 화살표) 기호 상단에 있는 제어 섹션. OC' , 낮으면 (화살표 다시 반전) 활성화됩니다(EN4 ) 4개의 3상태 출력 버퍼(QA QB QC QD ) 데이터 섹션에서.

로드/시프트'(LD/SH' ) 핀(7)의 내부 M1에 해당 (로드) 및 M2 (옮기다). 1의 접두어 찾기 및 2 기호의 나머지 부분에서 이것들에 의해 제어되는 것을 확인하십시오.

네거티브 에지 감지 시계(핀 10에서 반전 화살표로 표시) C3/2 두 가지 기능이 있습니다.

먼저 3 C3/2의 접두어가 3인 모든 입력에 영향을 줍니다. , 2,3D라고 말합니다. 또는 1,3D 데이터 섹션에서.

이것은 A, B, C, D에서 병렬 부하가 됩니다. M1에 귀속됨 및 C3 1,3D용 . 두 번째, 2 C3/2의 -오른쪽 화살표는 2 위치에서 데이터 클럭을 나타냅니다. 접두사(2,3D 핀 2에서).

따라서 우리는 SER에서 데이터 클럭을 가지고 있습니다. QA로 2 모드 사용 . C3/2 뒤의 오른쪽 화살표 내부 시프트 레지스터 단계에서 변속을 설명합니다. QA QB QC QD .

오른쪽을 가리키는 삼각형은 버퍼링을 나타냅니다. 역삼각형은 EN4에 의해 제어되는 3상 상태를 나타냅니다. .

모든 4 EN과 연결된 기호의 s 자주 생략됩니다. QB 단계 QC QD와 동일한 속성을 갖는 것으로 이해됩니다. . QD ' 다음 패키지의 SER으로 캐스케이드 오른쪽으로.

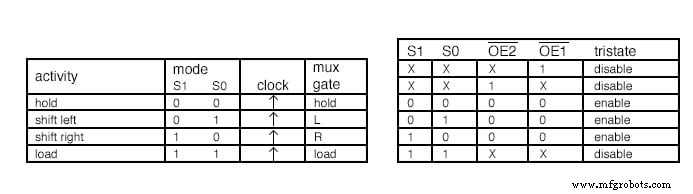

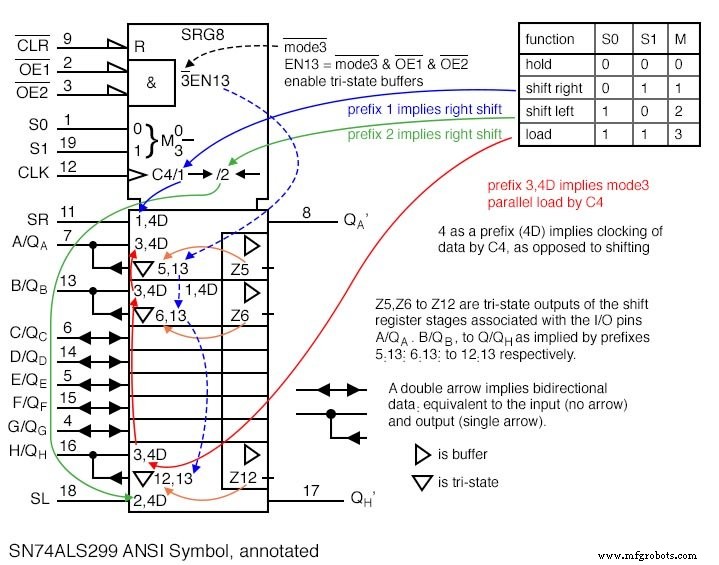

데이터 '299 데이터 시트에서 요약된 위의 표는 74ALS299 범용 시프트/저장 레지스터의 작동을 요약한 것입니다.

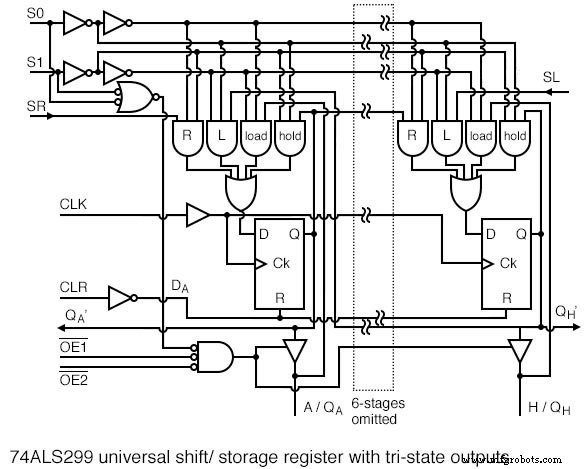

자세한 내용은 위의 '299 링크를 따르십시오. 멀티플렉서 게이트 R , L , 로드 이전 "좌/우 시프트 레지스터" 그림과 같이 작동합니다.

차이점은 모드 입력 S1 및 S0 왼쪽으로 이동, 오른쪽으로 이동 및 모드를 S1 S0 =로 설정하여 로드를 선택합니다. 01로 , 10 , 및 11 각각 표에 표시된 대로 멀티플렉서 게이트 L을 활성화합니다. , R , 및 로드 각각.

표를 참조하십시오. 사소한 차이점은 3상 출력의 병렬 부하 경로입니다. 실제로 tri-state 버퍼는 S1 S0 =11에 의해 비활성화됩니다(반드시 비활성화되어야 함). I/O 버스 부동 입력으로 사용합니다.

버스는 유사한 신호의 모음입니다. 입력은 A에 적용됩니다. , 나 H를 통해 (QA와 동일한 핀 , QB , QH를 통해 ) 및 로드로 라우팅됨 멀티플렉서의 게이트 및 D FF의 입력. 데이터는 클럭 펄스에 대한 병렬 로드입니다.

새로운 멀티플렉서 게이트는 hold라고 표시된 AND 게이트입니다. , S1 S0 =00에 의해 활성화됨 . 길게 gate는 Q에서 경로를 활성화합니다. FF의 출력을 다시 홀드로 게이트, 동일한 FF의 D 입력. 결과는 S1 S0 =00 모드에서 , 출력은 각각의 새로운 클록 펄스로 계속 다시 로드됩니다. 따라서 데이터가 유지됩니다. 이것은 표에 요약되어 있습니다.

출력 QA에서 데이터를 읽으려면 , QB , QH를 통해 , 삼중 상태 버퍼는 OE2', OE1' =00에 의해 활성화되어야 합니다. 및 모드 =S1 S0 =00, 01 또는 10 .

즉, 모드는 로드를 제외한 모든 것입니다. . 두 번째 표를 참조하십시오.

패키지에서 왼쪽으로 데이터를 오른쪽으로 이동하고 SR에서 이동합니다. 입력. QH 단계에서 오른쪽으로 이동한 모든 데이터 QH를 통해 오른쪽으로 계단식 '.

이 출력은 tri-state 버퍼의 영향을 받지 않습니다. S1 S0 =10에 대한 오른쪽 시프트 시퀀스 입니다:

SR> QA> QB> 질문C> QD> QE> QF> QG> QH (QH ')

SL에서 패키지에서 오른쪽으로 데이터를 왼쪽으로 이동합니다. 입력. QA 단계에서 왼쪽으로 이동한 모든 데이터 QA를 통해 왼쪽으로 계단식 ', 또한 tri-state 버퍼의 영향을 받지 않습니다. S1 S0 =01에 대한 왼쪽 시프트 시퀀스 입니다:

(QA ') QA

OE2' 중 하나에 의해 비활성화된 3상태 버퍼로 이동이 발생할 수 있습니다. 또는 OE1' =1 . 그러나 레지스터 내용 출력에는 액세스할 수 없습니다. 표를 참조하십시오.

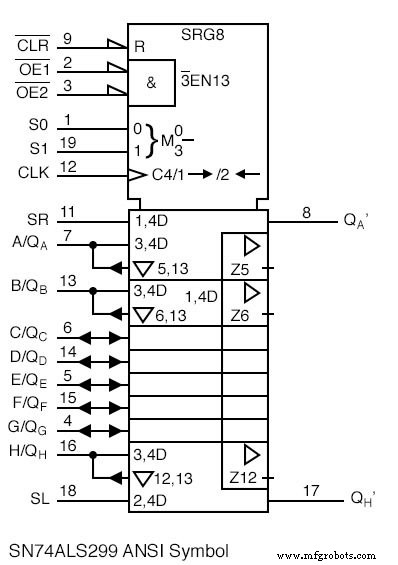

SN74ALS299 병렬 입력/병렬 출력 8비트 범용 시프트 레지스터에 대한 "깨끗한" ANSI 기호는 위에 참조용으로 표시되어 있습니다.

ANSI 기호의 주석 버전은 그 안에 포함된 용어를 명확히 하기 위해 표시됩니다.

ANSI 모드(S0 S1)는 이전 표에서 사용된 순서(S1 S0)와 반대입니다.

10진수 모드 숫자(1 &2)를 반대로 합니다. 어쨌든 우리는 이 불일치를 복사하여 공식 데이터 시트에 완전히 동의합니다.

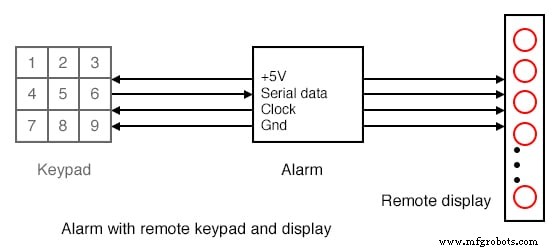

원격 키패드가 있는 알람 블록 다이어그램은 아래에서 반복됩니다. 이전에는 키패드 판독기와 원격 디스플레이를 별도의 장치로 구축했습니다.

이제 범용 시프트 레지스터를 사용하여 키패드와 디스플레이를 하나의 장치로 결합합니다.

다이어그램에서는 분리되어 있지만 키패드와 디스플레이는 모두 동일한 원격 인클로저에 포함되어 있습니다.

단일 클럭 펄스에서 키보드 데이터를 시프트 레지스터에 병렬 로드한 다음 메인 알람 상자로 시프트합니다.

동시에 LED 데이터를 메인 알람에서 원격 시프트 레지스터로 이동하여 LED를 켭니다.

동시에 키보드 데이터를 밖으로 이동하고 LED 데이터를 시프트 레지스터로 이동합니다.

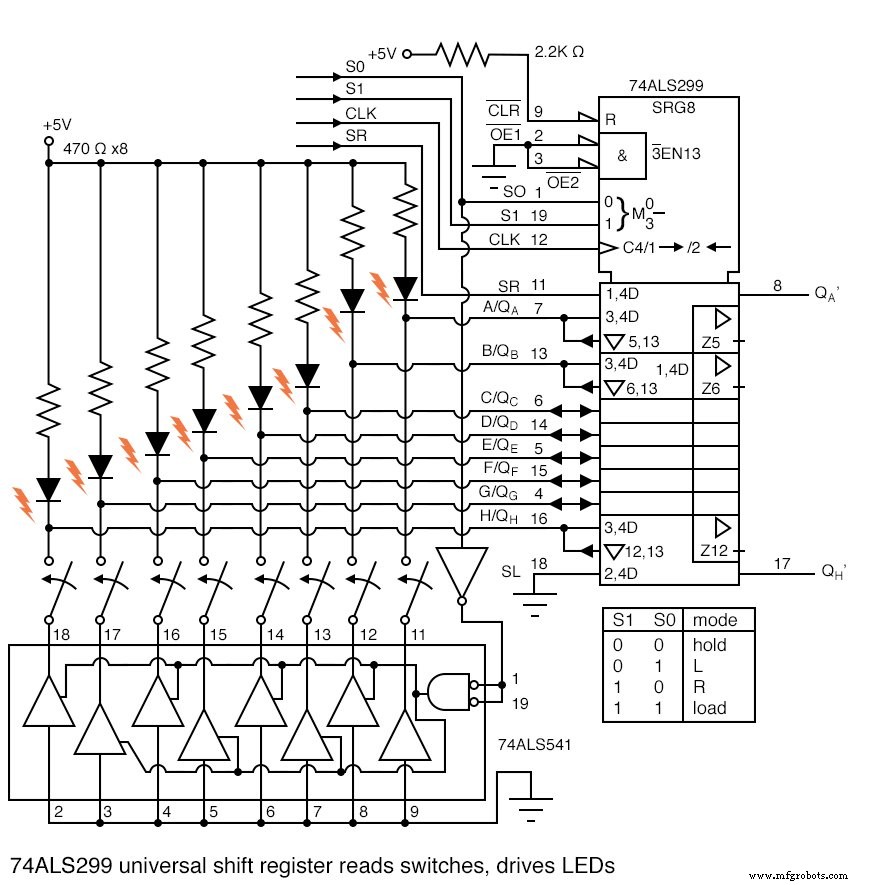

8개의 LED와 전류 제한 저항이 74ALS299 범용 시프트 레지스터의 8개 I/O 핀에 연결됩니다.

LED는 S1=0 S0=0이 있는 모드 3에서만 구동할 수 있습니다. . OE1' 및 OE2' tristate 활성화는 0, 1, 2 모드 동안 tristate 출력을 영구적으로 활성화하기 위해 접지됩니다. .

그러면 변속 중에 LED가 켜집니다(깜박임). 이것이 문제라면 EN1 ' 및 EN2' 접지되지 않고 S1과 병렬일 수 있습니다. 및 S0 각각 3상태 버퍼만 활성화하고 홀드, 모드 3 동안 LED를 켭니다. . 이 예에서는 간단하게 유지하겠습니다.

병렬 로드 중 S0=1 0으로 반전되면 8진 3상태 버퍼가 스위치 와이퍼를 접지할 수 있습니다.

상부 개방 스위치 접점은 8개 입력에서 저항-LED 조합에 의해 로직 하이로 풀업됩니다.

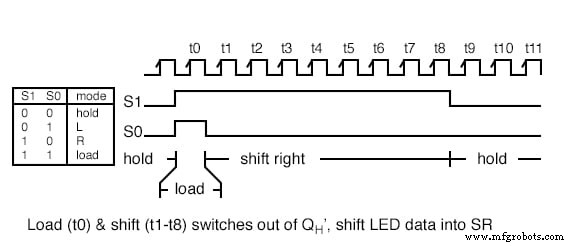

모든 스위치 폐쇄는 입력을 로우로 단락시킵니다. 스위치 데이터를 '299에 병렬로 로드합니다. 시계 t0에 둘 다 S0일 때 및 S1 높다. 아래 파형을 참조하십시오.

S0 한 번 낮음, 8개 시계(t0 t8까지 ) 스위치 폐쇄 데이터를 '299 밖으로 시프트 Qh를 통해 ' 핀.

동시에 새로운 LED 데이터가 SR로 이동합니다. 299 중 같은 8개의 시계로. LED 데이터는 변속이 진행됨에 따라 스위치 폐쇄 데이터를 대체합니다.

8교대 시계 이후 t8 , S1 항복 보류 모드로 낮아짐(S1 S0 =00 ). 더 많은 클록이 있어도 시프트 레지스터의 데이터는 동일하게 유지됩니다(예:T9). , t10 등

파형은 어디에서 오는가? 클럭 속도가 100kHz를 넘지 않으면 마이크로프로세서에 의해 생성될 수 있으며, 이 경우 t8 이후에 생성하는 클럭이 불편합니다. .

시계가 메가헤르츠 범위에 있으면 시계가 계속 작동합니다. 시계, S1 및 S0 여기에 표시되지 않은 디지털 논리에 의해 생성됩니다.

관련 워크시트:

<울>산업기술

Arduino 직렬:Arduino를 통한 직렬 통신 직렬 통신의 배경: 마이크로 컨트롤러 또는 마이크로 프로세서가 외부 세계와 통신해야 할 때 데이터를 8비트 패킷 형태로 제공하므로 한 시스템이 다른 시스템과 통신해야 하는 경우 총 8선 케이블이 사용되며 항상 그런 것은 아닙니다. 장거리 여행 시 신호가 왜곡되기 때문에 실용적인 솔루션입니다. 그것은 또한 8선 묶음의 높은 비용 때문에 비싸다 이 프로토콜은 새로운 프로토콜의 필요성이 각성된 이후에 병렬 통신으로 명명되었으며 설계자는 직렬 프로토콜로 명명된 새로운 프로토콜을 도입하여

easymon은 스마트폰 세계의 사용 편의성을 머신 컨트롤러 영역으로 가져오는 원격 모니터링 솔루션입니다. PLCnext 스토어에서 PLCnext 기능 확장을 설치하고 iOS 또는 Google Play 스토어에서 해당 스마트폰 앱을 설치하기만 하면 됩니다. 빠르고 쉬운 구성 후에 선택한 데이터 포인트 업데이트가 페어링된 스마트폰 앱 인스턴스에 전파됩니다. 현재 실행 중인 PLCnext 프로그램의 각 변수는 모니터링되는 데이터 포인트로 구성할 수 있습니다. 1. 디자인에 의한 개인정보 보호 사용 편의성 외에도 easymon을 개발하