산업기술

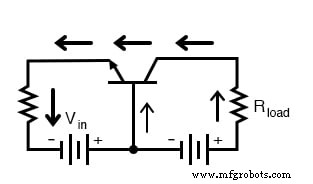

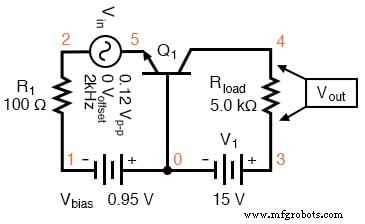

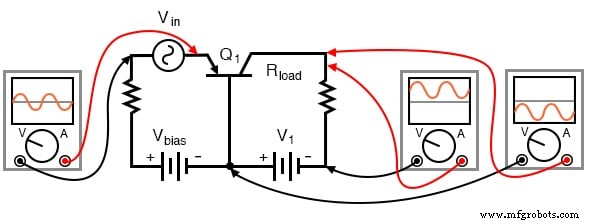

우리가 연구해야 하는 최종 트랜지스터 증폭기 구성(아래 그림)은 공통 기반 증폭기입니다. . 이 구성은 다른 두 구성보다 더 복잡하고 이상한 작동 특성으로 인해 덜 일반적입니다.

공통 베이스 증폭기

이를 공통 기반이라고 합니다. (DC 전원은 제쳐두고), 신호 소스와 부하는 아래 그림과 같이 공통 연결 지점으로 트랜지스터의 베이스를 공유하기 때문에 구성합니다.

공통 베이스 증폭기:이미터와 베이스 사이의 입력, 컬렉터와 베이스 사이의 출력.

아마도 이 구성의 가장 두드러진 특징은 첫 번째 그림에서 굵은 화살표로 표시된 것처럼 입력 신호 소스가 트랜지스터의 전체 에미터 전류를 전달해야 한다는 것입니다. 알다시피 이미 터 전류는 트랜지스터의 다른 전류보다 크며 베이스 전류와 컬렉터 전류의 합입니다. 마지막 두 증폭기 구성에서 신호 소스는 트랜지스터의 베이스 리드에 연결되어 최소 현재 가능합니다.

입력 전류가 출력 전류를 포함하여 회로의 다른 모든 전류를 초과하기 때문에 이 증폭기의 전류 이득은 1보다 작습니다. (Rload가 컬렉터에 어떻게 연결되어 신호 소스보다 약간 적은 전류를 전달하는지 주목하십시오). 즉, 감쇠 증폭이 아닌 현재 그것. 공통 이미 터 및 공통 수집기 증폭기 구성에서 이득과 가장 밀접하게 관련된 트랜지스터 매개 변수는 β입니다. 공통 베이스 회로에서 우리는 또 다른 기본 트랜지스터 매개변수를 따릅니다. 컬렉터 전류와 에미터 전류 사이의 비율은 항상 1보다 작은 비율입니다. 모든 트랜지스터에 대한 이 소수 값을 알파라고 합니다. 비율 또는 α 비율.

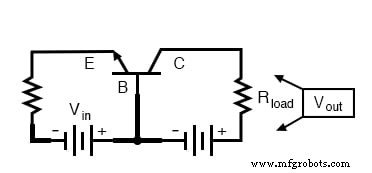

분명히 신호 전류를 높일 수 없기 때문에 신호 전압을 높일 것으로 예상하는 것이 합리적입니다. 아래 그림의 회로에 대한 SPICE 시뮬레이션은 이러한 가정을 입증할 것입니다.

DC SPICE 분석을 위한 공통 베이스 회로.

공통 베이스 증폭기 vin 0 1 r1 1 2 100 q1 4 0 2 mod1 v1 3 0 dc 15 rload 3 4 5k .model mod1 npn .dc vin 0.6 1.2 .02 .plot dc v(3,4).

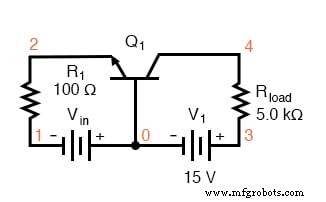

공통 기반 증폭기 DC 전송 기능 n.

위의 그림에서 출력 전압은 0.6볼트에서 1.2볼트 범위에 걸쳐 스위프되는 입력 전압과 함께 거의 아무것도(차단)에서 15.75볼트(포화)로 이동합니다. 출력 전압 플롯은 입력에서 약 0.7V까지 상승을 나타내지 않고 약 1.12V 입력에서 차단(평탄화)합니다. 이것은 출력 전압 범위가 15.75볼트이고 입력 전압 범위가 0.42볼트에 불과한 다소 큰 전압 이득을 나타냅니다. 이득 비율은 37.5 또는 31.48dB입니다. 또한 입력 전압 소스의 직렬 지원 효과로 인해 출력 전압(Rload에서 측정)이 포화 상태에서 전원 공급 장치(15V)를 초과하는 방식에 주목하십시오.

AC 신호 소스(및 DC 바이어스 전압)를 사용한 SPICE 분석의 두 번째 세트는 동일한 내용을 나타냅니다. 높은 전압 이득

예제 회로

SPICE AC 분석을 위한 공통 베이스 회로.

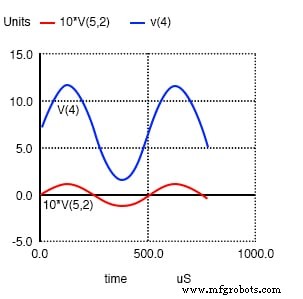

보시다시피, 아래 그림의 입력 및 출력 파형은 서로 위상이 같습니다. 이것은 공통 베이스 증폭기가 반전되지 않음을 알려줍니다.

공통 베이스 증폭기 vin 5 2 sin (0 0.12 2000 0 0) vbias 0 1 dc 0.95 r1 2 1 100 q1 4 0 5 mod1 v1 3 0 dc 15 rload 3 4 5k .model.mod1 n0 m .plot tran v(5,2) v(4) .end

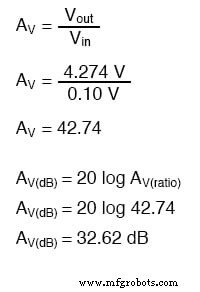

2kHz의 단일 주파수에서 아래 표의 AC SPICE 분석은 이득 계산을 위한 입력 및 출력 전압을 제공합니다.

2kHz에서 공통 기반 AC 분석 – 넷리스트에 이어 출력.

공통 베이스 증폭기 vin 5 2 ac 0.1 sin vbias 0 1 dc 0.95 r1 2 1 100 q1 4 0 5 mod1 v1 3 0 dc 15 rload 3 4 5k .model mod1 npn .ac .dec 1 2000 (5,2) vm(4,3) .end 주파수 mag(v(5,2)) mag(v(4,3))—————————————————— ————0.000000e+00 1.000000e-01 4.273864e+00

두 번째 분석(위 표)의 전압 수치는 42.74(4.274V/0.1V) 또는 32.617dB의 전압 이득을 보여줍니다.

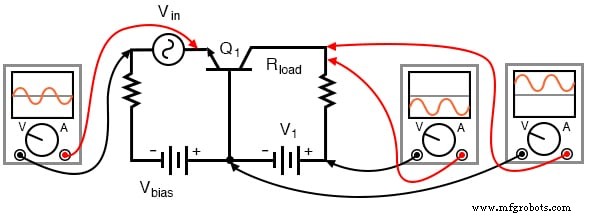

다음은 방금 시뮬레이션한 회로에서 다양한 신호의 위상 관계와 DC 오프셋을 요약한 아래 그림의 회로에 대한 또 다른 보기입니다.

NPN 공통 베이스 증폭기의 위상 관계 및 오프셋.

. . . PNP 트랜지스터의 경우:아래 그림.

PNP 공통 베이스 증폭기의 위상 관계 및 오프셋.

공통 베이스 증폭기 구성에 대한 전압 이득을 예측하는 것은 매우 어렵고 직접 측정하기 어려운 트랜지스터 동작의 근사치를 포함합니다. 전압 이득이 두 저항의 비율에 의해 설정되거나(공통-이미터) 변경되지 않는 값으로 고정된(공통-수집기) 다른 증폭기 구성과 달리 공통 베이스 증폭기의 전압 이득은 입력 신호의 DC 바이어스. 알다시피 에미터와 베이스 사이의 내부 트랜지스터 저항은 전압 이득을 결정하는 데 중요한 역할을 하며 이 저항은 에미터를 통과하는 다양한 전류 레벨에 따라 변합니다.

이 현상은 설명하기 어렵지만 컴퓨터 시뮬레이션을 사용하여 설명하는 것은 쉽습니다. 공통 베이스 증폭기 회로(이전 그림)에 대한 SPICE 시뮬레이션은 AC 신호 진폭과 기타 모든 회로 매개변수를 일정하게 유지하면서 DC 바이어스 전압을 약간 변경(아래 그림의 vbias)합니다. 한 시뮬레이션에서 다른 시뮬레이션으로 전압 이득이 변경됨에 따라 다른 출력 전압 진폭이 표시됩니다.

이러한 분석은 모두 "전달 함수" 모드에서 수행되지만 각각은 과도 분석 모드(시간 경과에 따른 전압 플롯)에서 먼저 "검증"되어 전체 파형이 부적절하게 "클리핑"되지 않고 충실하게 재생되었음을 보장합니다. 편향. "주석 처리된" 과도 분석 설명인 아래 그림의 "*.tran 0.02m 0.78m"을 참조하십시오. 이득 계산은 왜곡된 파형을 기반으로 할 수 없습니다. SPICE는 ".tf v(4) vin" 문으로 소신호 DC 이득을 계산할 수 있습니다. 출력은 v(4)입니다. vin으로 입력 .

커먼 베이스 앰프 vbias=0.85V vin 5 2 sin (0 0.12 2000 0 0) vbias 0 1 dc 0.85 r1 2 1 100 q1 4 0 5 mod1 v1 3 0 dc 15 rload 3 4 mod1 .tran 0.02m 0.78m .tf v(4) vin .end

공통 베이스 앰프 전류 이득 Iin 55 5 0A vin 55 2 sin (0 0.12 2000 0 0) vbias 0 1 dc 0.8753 r1 2 1 100 q1 4 0 5 mod1 v1 3 0 dc 3 14 mod15k npn *.tran 0.02m 0.78m .tf I(v1) Iin .end 전달 함수 정보:전달 함수 =9.900990e-01 iin 입력 임피던스 =9.900923e+11 v1 출력 임피던스 =1.000000e+20

SPICE 순 목록:다양한 DC 바이어스 전압에 대한 공통 베이스, 전달 함수(전압 이득). SPICE 순 목록:공통 베이스 앰프 전류 이득; 참고 .tf v(4) vin 문. DC 전류 이득 I(vin)/Iin에 대한 전달 함수; 참고 .tf I(vin) Iin 문.

명령줄에서 spice -b filename.cir .tf로 인해 인쇄된 출력물을 생성합니다. 문:transfer_function, output_impedance 및 input_impedance. 축약된 출력 목록은 vbias가 있는 실행에서 가져온 것입니다. 아래 표에 기록된 대로 0.85, 0.90, 0.95, 1.00V에서.

SPICE 출력:공통 베이스 전달 함수.

회로:common-base amp vbias=0.85V transfer_function =3.756565e+01 output_impedance_at_v(4) =5.000000e+03 vin#input_impedance =1.317825e+02 회로:common-base amp =vbias=0 전달 함수 정보:transfer_function =3.942567e+01 output_impedance_at_v(4) =5.000000e+03 vin#input_impedance =1.255653e+02 회로:common-base amp vbias=0.9V transfer_function =4.07954 output +03 vin#input_impedance =1.213493e+02 회로:공통 베이스 amp vbias=0.95V transfer_function =4.273864e+01 output_impedance_at_v(4) =5.000000e+03 vin#input.1582 회로:18 =1.00V 전송 기능 =4.401137e+01 output_impedance_at_v(4) =5.000000e+03 vin#input_impedance =1.124822e+02

위의 표에서 추세가 분명해야 합니다. DC 바이어스 전압이 증가하면 전압 이득(transfer_function)도 증가합니다. 각 후속 시뮬레이션(vbias=0.85, 0.8753, 0.90, 0.95, 1.00V)이 각각 더 큰 이득(transfer_function=37.6, 39.4 40.8, 42.7, 44.0)을 생성하기 때문에 전압 이득이 증가하고 있음을 알 수 있습니다. 이러한 변화는 주로 바이어스 전압의 미세한 변화로 인한 것입니다.

위 표의 마지막 세 줄(오른쪽)은 I(v1)/Iin을 보여줍니다. 0.99의 현재 이득. (마지막 두 줄은 유효하지 않은 것처럼 보입니다.) 이것은 β=100에 대해 의미가 있습니다. α=β/(β+1), α=0.99=100/(100-1). 낮은 전류 이득(항상 1보다 작음)과 다소 예측할 수 없는 전압 이득의 조합은 공통 기반 설계에 반대하여 이를 몇 가지 실용적인 응용 프로그램으로 분류합니다.

이러한 몇 가지 응용 프로그램에는 무선 주파수 증폭기가 포함됩니다. 접지된 베이스는 이미터의 입력을 컬렉터 출력으로부터 보호하여 RF 증폭기의 불안정성을 방지합니다. 공통 베이스 구성은 공통 이미터 또는 공통 컬렉터보다 높은 주파수에서 사용할 수 있습니다. "클래스 C 공통 베이스 750mW RF 전력 증폭기" 9장을 참조하십시오. 보다 정교한 회로는 "클래스 A 공통 베이스 소신호 고이득 증폭기" 9장을 참조하십시오.

검토:

<울>관련 워크시트:

<울>산업기술

제조 리쇼어링에 대한 주제는 엔지니어링 생산이 역외 회사에 하도급된 이후로 영국 산업 전반에 걸쳐 논쟁의 대상이었습니다. 지금까지 제조업 부문은 이러한 상황을 견뎌왔으며 영국은 지구상에서 9번째로 큰 제조업 국가입니다. 그러나 COVID-19 바이러스의 출현으로 우리가 비즈니스를 수행하는 방식의 많은 측면이 변경되었습니다. 오늘날 많은 영국 기업들은 필수 제품의 생산을 영국으로 되돌리기 위한 전국적인 리쇼어링 노력을 촉구하고 있습니다. 주요 전염병에도 불구하고 영국 기업들이 생산을 본국으로 다시 가져갈 계획인 데에는 충분한 이유

새롭고 향상된 집적 회로 연산 증폭기 741은 기술 분야에서 빠르게 발전하고 있습니다. 아날로그 회로에서 회로 유연성을 제공하는 것 외에도 아날로그 컴퓨터에서 응용 프로그램에서 먼 길을 왔습니다. 여러 핀(총 8개)이 있는 IC Op-Amp 741은 조절을 위해 외부 피드백에 의존하면서 효과적으로 기능을 수행합니다. 또한 전자 회로 및 장치에 적용되어 적합하고 안전합니다. 작동 메커니즘, 사양 및 응용 분야에서 이 앰프의 중요성에 대해 자세히 알아보려면 계속 읽으십시오. 1. 연산 증폭기 741이란 무엇입니까? 일반적으로 O