산업기술

실제 연산 증폭기는 "이상적인" 모델에 비해 약간의 불완전성이 있습니다. 실제 장치는 완벽한 차동 증폭기에서 벗어납니다. 1 빼기 1은 0이 아닐 수 있습니다. 제로화되지 않은 아날로그 미터와 같은 오프셋이 있을 수 있습니다. 입력은 전류를 끌어올 수 있습니다. 특성은 나이와 온도에 따라 변할 수 있습니다. 게인은 고주파수에서 감소할 수 있으며 위상은 입력에서 출력으로 이동할 수 있습니다. 이러한 불완전성으로 인해 일부 응용 프로그램에서는 눈에 띄는 오류가 발생하지 않고 다른 응용 프로그램에서는 허용되지 않는 오류가 발생할 수 있습니다. 경우에 따라 이러한 오류가 보상될 수 있습니다. 때로는 더 높은 품질과 더 높은 비용의 장치가 필요합니다.

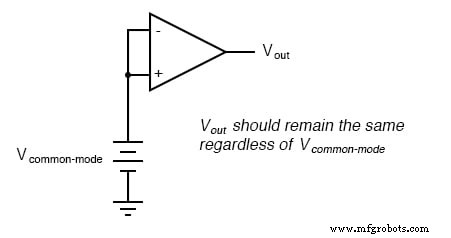

앞서 언급했듯이 이상적인 차동 증폭기는 전압 차이만 증폭합니다. 두 입력 사이. 차동 증폭기의 두 입력이 함께 단락되어야 하는 경우(따라서 두 입력 간의 전위차가 0이 보장됨) 단락된 두 입력과 접지 사이에 적용되는 전압의 양에 대해 출력 전압에 변화가 없어야 합니다.

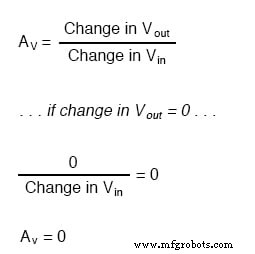

"Vcommon-mode로 입력과 접지 사이에 공통된 전압 "는 이 경우 공통 모드 전압이라고 합니다. . 이 공통 전압을 변경할 때 완전 차동 증폭기의 출력 전압은 절대적으로 일정하게 유지되어야 합니다(공통 모드 입력의 임의 변경에 대한 출력 변경 없음). 이는 공통 모드 전압 이득으로 변환됩니다. 0의.

높은 차동 이득을 가진 차동 증폭기인 연산 증폭기는 이상적으로는 공통 모드 이득도 0입니다. 그러나 실생활에서 이것은 쉽게 달성되지 않습니다. 따라서 공통 모드 전압은 항상 연산 증폭기의 출력 전압에 어느 정도 영향을 미칩니다.

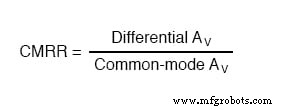

이와 관련하여 실제 연산 증폭기의 성능은 차동 전압 이득(두 입력 전압 간의 차이를 증폭하는 정도) 대 공통 모드 전압 이득(공통 모드를 증폭하는 정도)로 가장 일반적으로 측정됩니다. 전압). 전자와 후자의 비율을 공통 모드 거부 비율이라고 합니다. , CMRR로 약칭:

공통 모드 이득이 0인 이상적인 연산 증폭기는 무한 CMRR을 갖습니다. 실제 연산 증폭기는 CMRR이 높으며 유비쿼터스 741은 약 70dB이며 비율로 따지면 3,000이 약간 넘습니다.

일반적인 연산 증폭기의 공통 모드 제거 비율이 너무 높기 때문에 공통 모드 이득은 일반적으로 연산 증폭기가 네거티브 피드백과 함께 사용되는 회로에서 큰 문제가 되지 않습니다. 증폭기 회로의 공통 모드 입력 전압이 갑자기 변경되어 공통 모드 이득으로 인해 출력에 상응하는 변화가 발생하는 경우 출력의 변화는 네거티브 피드백 및 차동 이득으로 신속하게 수정됩니다( 많이 공통 모드 이득보다 큼) 시스템을 평형 상태로 되돌리기 위해 작동했습니다. 물론 출력에서 변경 사항이 보일 수 있지만 예상보다 훨씬 작습니다.

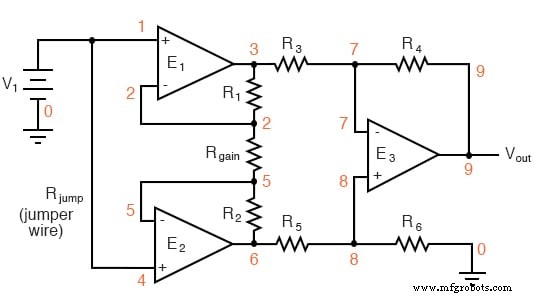

그러나 명심해야 할 사항은 계측 증폭기와 같은 차동 연산 증폭기 회로의 공통 모드 이득입니다. 연산 증폭기의 밀봉 패키지와 극도로 높은 차동 이득 외에도 저항 값의 불균형으로 인해 공통 모드 이득이 발생할 수 있습니다. 이를 시연하기 위해 입력이 함께 단락된(차동 전압 없음) 계측 증폭기에서 SPICE 분석을 실행하여 무슨 일이 일어나는지 확인하기 위해 공통 모드 전압을 부과합니다. 먼저 완벽하게 균형 잡힌 회로의 출력 전압을 보여주는 분석을 실행합니다. 공통 모드 전압이 변경될 때 출력 전압이 변경되지 않을 것으로 예상해야 합니다.

계측 증폭기 v1 1 0 rin1 1 0 9e12 rjump 1 4 1e-12 rin2 4 0 9e12 e1 3 0 1 2 999k e2 6 0 4 5 999k e3 9 0 8 7 999k 1099k 5 10k r2 5 6 10k r3 3 7 10k r4 7 9 10k r5 6 8 10k r6 8 0 10k .dc v1 0 10 1 .print dc v(9) .end

v1 v(9) 0.000E+00 0.000E+00 1.000E+00 1.355E-16 2.000E+00 2.710E-16 3.000E+00 0.000E+00 보시는 바와 같이 출력전압 v( 9) 4.000E+00 5.421E-16은 0 6.000E+00 0.000E+00에서 10볼트로 스윕하는 공통 모드 5.000E+00 0.000E+00 입력 전압(v1)에 대해 거의 변경되지 않습니다. 7.000E+00 0.000E+00 8.000E+00 1.084E-15 9.000E+00 -1.084E-15 1.000E+01 0.000E+00

매우 작은 편차(실제로는 회로의 실제 동작이 아니라 SPICE의 기이함)를 제외하고는 입력 전압 차이가 0인 0볼트에서 출력이 안정적이어야 합니다. 그러나 회로에 저항 불균형을 도입하여 R5 값을 증가시키자 10,000Ω에서 10,500Ω으로 변경하고 어떤 일이 발생하는지 확인합니다(netlist는 간결함을 위해 생략되었습니다. 변경된 유일한 것은 R5의 값입니다. ):

v1 v(9) 0.000E+00 0.000E+00 1.000E+00 -2.439E-02 2.000E+00 -4.878E-02 3.000E+00 -7.317E-02 이번에는 상당한 변화가 보입니다. 4.000E+00 -9.756E-02(0 ~ 0.2439볼트) 출력 전압 5.000E+00 -1.220E-01 공통 모드 입력 전압 스윕 6.000E+00 -1.463E-01 0 ~ 10볼트 전에 그랬던 것처럼. 7.000E+00 -1.707E-01 8.000E+00 -1.951E-01 9.000E+00 -2.195E-01 1.000E+01 -2.439E-01

입력 전압 차는 여전히 0볼트이지만 공통 모드 전압이 변경됨에 따라 출력 전압이 크게 변경됩니다. 이것은 우리가 피하려고 하는 공통 모드 이득을 나타냅니다. 그 이상으로, 연산 증폭기 자체의 결함과는 아무 관련이 없는 우리 자신의 공통 모드 이득입니다. 상당히 강화된 차동 이득(이 특정 회로에서 실제로 3과 동일)과 회로 외부에 음의 피드백이 없는 경우 이 공통 모드 이득은 계측기 신호 응용 프로그램에서 확인되지 않습니다.

이 공통 모드 이득을 수정하는 유일한 방법은 모든 저항 값의 균형을 맞추는 것입니다. 개별 부품으로 계측 증폭기를 설계할 때(통합 패키지로 구매하는 것보다), " 그러한 공통 모드 이득을 제거하십시오. 저항 네트워크를 "트림"하는 수단을 제공하면 추가 이점도 있습니다. 모든 저항 값이 정확해야 하지만 연산 증폭기 중 하나의 불완전성으로 인해 공통 모드 이득이 존재한다고 가정합니다. 조정 조항을 사용하면 이 원치 않는 이득을 보상하기 위해 저항을 트리밍할 수 있습니다.

일부 연산 증폭기 모델의 단점 중 하나는 출력 래치업입니다. , 일반적으로 허용 한계를 초과하는 공통 모드 입력 전압으로 인해 발생합니다. 공통 모드 전압이 제조업체에서 지정한 한계를 벗어나면 출력이 갑자기 하이 모드에서 "래치"될 수 있습니다(최대 출력 전압에서 포화됨). JFET 입력 연산 증폭기에서 공통 모드 입력 전압이 음의 전원 공급 장치 레일 전압에 너무 근접하면 래치업이 발생할 수 있습니다. 예를 들어 TL082 연산 증폭기에서 이는 공통 모드 입력 전압이 음의 전원 공급 장치 레일 전압의 약 0.7볼트 이내일 때 발생합니다. 이러한 상황은 음의 전원 공급 장치 레일이 접지되고(0볼트) 입력 신호가 0볼트로 자유롭게 스윙하는 단일 공급 회로에서 쉽게 발생할 수 있습니다.

래치업은 공통 모드 입력 전압 초과에 의해 트리거될 수도 있습니다. 전원 공급 장치 레일 전압, 음 또는 양. 일반적으로 문제의 연산 증폭기가 래치업으로부터 보호되더라도(741에서와 같이) 입력 전압이 양의 전원 공급 장치 레일 전압 이상으로 상승하거나 음의 전원 공급 장치 레일 전압 아래로 가라앉는 것을 허용해서는 안 됩니다. 및 1458 연산 증폭기 모델). 최소한 연산 증폭기의 동작은 예측할 수 없게 될 수 있습니다. 최악의 경우 전원 전압을 초과하는 입력 전압에 의해 트리거되는 일종의 래치업이 연산 증폭기에 파괴적일 수 있습니다.

이 문제는 피하는 것이 쉬워 보일 수 있지만 생각보다 가능성이 높습니다. 전원을 켤 때 연산 증폭기 회로의 경우를 고려하십시오. 회로가 전에 전체 입력 신호 전압을 수신하는 경우 자체 전원 공급 장치가 필터 커패시터를 충전하기에 충분한 시간을 갖고 있으면 공통 모드 입력 전압이 짧은 시간 동안 전원 공급 장치 레일 전압을 쉽게 초과할 수 있습니다. 연산 증폭기가 다른 전원에서 공급되는 회로에서 신호 전압을 수신하고 자체 전원에 장애가 발생하면 신호 전압이 무기한 시간 동안 전원 공급 장치 레일 전압을 초과할 수 있습니다!

연산 증폭기 성능에 대한 또 다른 실질적인 문제는 전압 오프셋입니다. . 즉, 두 개의 입력 단자가 함께 단락될 때 출력 전압이 0볼트가 아닌 다른 값을 갖는 효과입니다. 연산 증폭기는 무엇보다도 차동 증폭기라는 것을 기억하십시오. 두 입력 연결 사이의 전압 차이를 증폭해야 하며 그 이상은 아닙니다. 입력 전압 차이가 정확히 0볼트일 때 (이상적으로는) 출력에 정확히 0볼트가 있을 것으로 예상합니다. 그러나 현실 세계에서는 이런 일이 거의 발생하지 않습니다. 문제의 연산 증폭기에 0 공통 모드 이득(무한 CMRR)이 있더라도 두 입력이 함께 단락되면 출력 전압이 0이 아닐 수 있습니다. 0과의 이 편차를 오프셋이라고 합니다. .

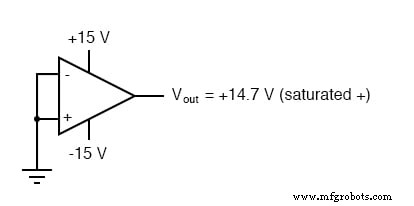

완벽한 연산 증폭기는 입력이 함께 단락되고 접지된 상태에서 정확히 0볼트를 출력합니다. 그러나 선반에 있는 대부분의 연산 증폭기는 출력을 음 또는 양의 포화 레벨로 구동합니다. 위에 표시된 예에서 출력 전압은 이 특정 연산 증폭기의 양의 포화 한계로 인해 +V(+15V)보다 약간 작은 양의 14.7V 값에서 포화됩니다. 이 연산 증폭기의 오프셋은 출력을 완전히 포화된 지점으로 구동하기 때문에 출력에 얼마나 많은 전압 오프셋이 존재하는지 알 수 있는 방법이 없습니다. +V/-V 분할 전원 공급 장치의 전압이 충분히 높으면 오프셋 효과로 인해 출력이 한 방향 또는 다른 방향으로 수백 볼트가 될 수 있습니다.

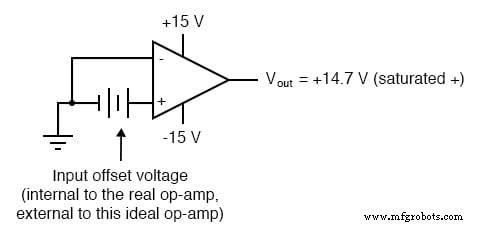

이러한 이유로 오프셋 전압은 일반적으로 입력의 등가량으로 표현됩니다. 이 효과를 생성하는 전압 차. 다시 말해, 연산 증폭기가 완벽하고(오프셋이 전혀 없음) 작은 전압이 입력 중 하나와 직렬로 적용되어 출력 전압이 0에서 멀어지게 한다고 상상합니다. 연산 증폭기 차동 이득이 너무 높기 때문에 "입력 오프셋 전압"에 대한 수치는 단락된 입력에서 볼 수 있는 것을 설명할 필요가 없습니다.

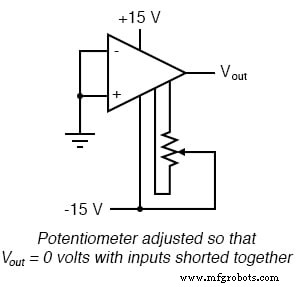

오프셋 전압은 모든 연산 증폭기 회로에서 약간의 오류를 유발하는 경향이 있습니다. 그래서 우리는 그것을 어떻게 보상합니까? 공통 모드 이득과 달리 일반적으로 제조업체에서 패키지된 연산 증폭기의 오프셋을 트리밍하기 위한 규정이 있습니다. 일반적으로 연산 증폭기 패키지의 두 개의 추가 단자는 외부 "트림" 전위차계를 연결하기 위해 예약되어 있습니다. 이러한 연결 지점에는 오프셋 null이라는 레이블이 지정됩니다. 다음과 같은 일반적인 방식으로 사용됩니다.

741 및 3130과 같은 단일 연산 증폭기에서 오프셋 널 연결 지점은 8핀 DIP 패키지의 핀 1 및 5입니다. 연산 증폭기의 다른 모델은 오프셋 널 연결이 다른 핀에 있을 수 있고/또는 트림 전위차계 연결의 약간 다른 구성이 필요할 수 있습니다. 일부 연산 증폭기는 오프셋 널 핀을 전혀 제공하지 않습니다! 자세한 내용은 제조업체의 사양을 참조하세요.

연산 증폭기의 입력은 입력 임피던스가 매우 높습니다. 즉, 연산 증폭기의 두 입력 신호 연결에 들어오거나 나가는 입력 전류는 매우 작습니다. 대부분의 연산 증폭기 회로 분석 목적을 위해 우리는 그것들을 전혀 존재하지 않는 것처럼 취급합니다. 입력 연결에 들어오거나 나가는 전류가 절대적으로 0인 것처럼 회로를 분석합니다. 그러나 이 목가적인 그림은 완전히 사실이 아닙니다. 연산 증폭기, 특히 바이폴라 트랜지스터 입력이 있는 연산 증폭기는 내부 회로가 적절하게 바이어스되도록 입력 연결을 통해 일정량의 전류가 있어야 합니다. 논리적으로 이러한 전류를 바이어스 전류라고 합니다. . 특정 조건에서 연산 증폭기 바이어스 전류가 문제가 될 수 있습니다. 다음 회로는 이러한 문제 조건 중 하나를 보여줍니다.

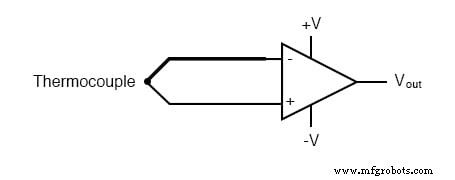

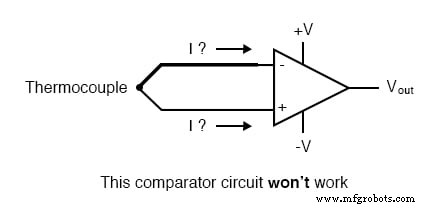

언뜻보기에는이 회로에 명백한 문제가 없습니다. 온도에 비례하는 작은 전압을 생성하는 열전대(실제로는 차이에 비례하는 전압 합금 열전쌍 와이어가 연산 증폭기로 이어지는 구리 와이어와 연결될 때 형성되는 "기준" 접합과 측정 접합 사이의 온도에서 연산 증폭기를 양극 또는 음극으로 구동합니다. 즉, 이것은 끝단 열전대 접합과 기준 접합(연산 증폭기 근처) 사이의 온도를 비교하는 일종의 비교기 회로입니다. 문제는 다음과 같습니다. 열전쌍에 의해 형성된 와이어 루프는 두 입력 바이어스 전류 모두에 대한 경로를 제공하지 않습니다. 두 바이어스 전류가 같은 방향으로(연산 증폭기로 들어가거나 밖으로) 이동하려고 하기 때문입니다.

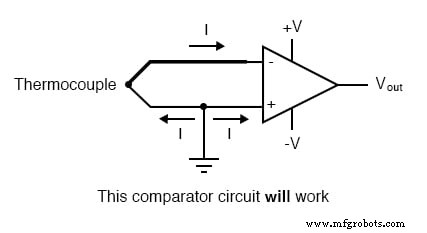

이 회로가 제대로 작동하려면 입력 와이어 중 하나를 접지해야 하므로 두 전류 모두에 대해 접지로(또는 접지에서) 경로를 제공해야 합니다.

반드시 명백한 문제는 아니지만 매우 실제적인 문제입니다!

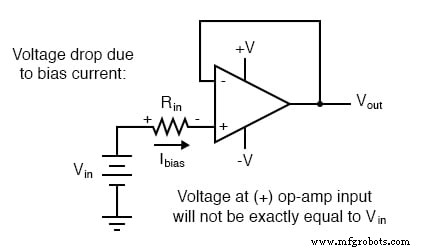

입력 바이어스 전류가 문제를 일으킬 수 있는 또 다른 방법은 회로 저항에 원치 않는 전압을 떨어뜨리는 것입니다. 이 회로를 예로 들어 보겠습니다.

위와 같은 전압 팔로워 회로가 입력 전압을 출력에서 정확하게 재생하기를 기대합니다. 그러나 입력 전압 소스와 직렬로 연결된 저항은 어떻습니까? 비반전(+) 입력을 통해 바이어스 전류가 전혀 없으면 Rin 양단에 약간의 전압이 떨어집니다. , 따라서 비반전 입력의 전압을 실제 Vin과 동일하지 않게 만듭니다. 값. 바이어스 전류는 일반적으로 마이크로암페어 범위에 있으므로 Rin 양단의 전압 강하는 Rin을 제외하고는 그다지 많지 않을 것입니다. 매우 큽니다. 입력 저항(Rin ) 할 하나의 전극에 이온 투과성 유리 장벽(수백만 Ω의 저항이 있는 매우 열악한 전도체)이 포함된 pH 프로브 전극의 경우 매우 클 수 있습니다.

실제로 pH 전극 전압 측정을 위한 연산 증폭기 회로를 구축하는 경우 바이폴라 트랜지스터로 구축된 것 대신 FET 또는 MOSFET(IGFET) 입력 연산 증폭기를 사용하고 싶을 것입니다(입력 바이어스 전류 감소용). 하지만 그럼에도 불구하고 약간의 바이어스 전류가 남아 있으면 측정 오류가 발생할 수 있으므로 좋은 설계를 통해 이를 완화할 수 있는 방법을 찾아야 합니다.

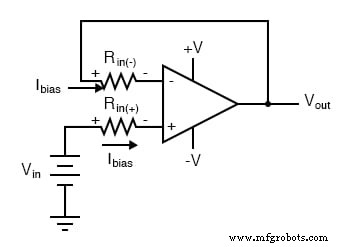

그렇게 하는 한 가지 방법은 두 개의 입력 바이어스 전류가 동일할 것이라는 가정을 기반으로 합니다. 실제로는 거의 동일한 경우가 많으며 그 차이를 입력 오프셋 전류라고 합니다. . 동일하다면 다음과 같이 동일한 양의 저항을 다른 입력과 직렬로 삽입하여 입력 저항 전압 강하의 영향을 상쇄할 수 있어야 합니다.

회로에 추가 저항이 추가되면 출력 전압은 Vin에 더 가까워집니다. 두 입력 전류 사이에 약간의 오프셋이 있더라도 이전보다.

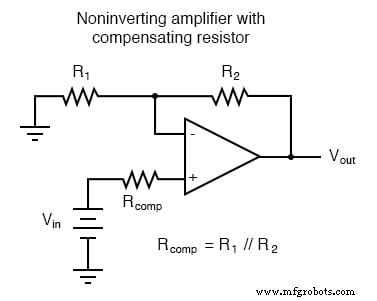

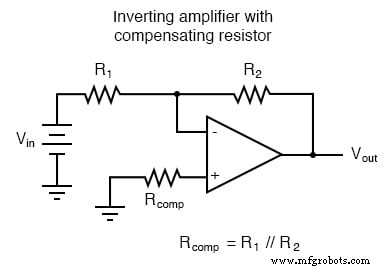

반전 및 비반전 증폭기 회로 모두에 대해 바이어스 전류 보상 저항은 비반전(+) 입력과 직렬로 배치되어 분배기 네트워크의 바이어스 전류 전압 강하를 보상합니다.

어느 경우든 보상 저항 값은 R1의 병렬 저항 값을 계산하여 결정됩니다. 및 R2 . 값이 병렬과 같은 이유 R1과 동일 및 R2 ? 중첩 정리를 사용하여 반전(-) 입력의 바이어스 전류에 의해 생성되는 전압 강하의 양을 계산할 때 바이어스 전류를 연산 증폭기 내부의 전류 소스에서 오는 것처럼 취급하고 모든 전압 소스를 단락시킵니다. (Vin 및 V아웃 ). 이것은 바이어스 전류에 대한 두 개의 병렬 경로를 제공합니다(R1를 통해 그리고 R2를 통해 , 둘 다 접지). 비반전(+) 입력에 대한 바이어스 전류의 영향을 복제하기를 원하므로 해당 입력과 직렬로 삽입하기로 선택한 저항 값은 R1과 같아야 합니다. R2와 병렬로 .

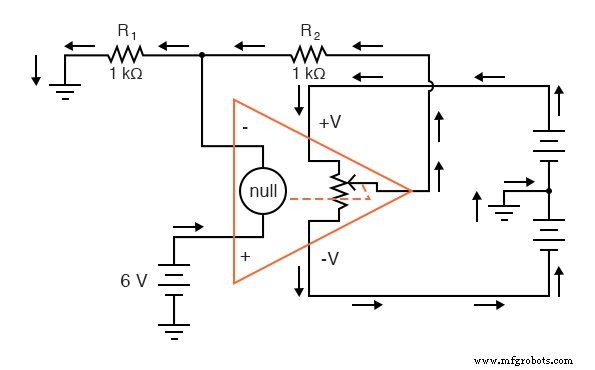

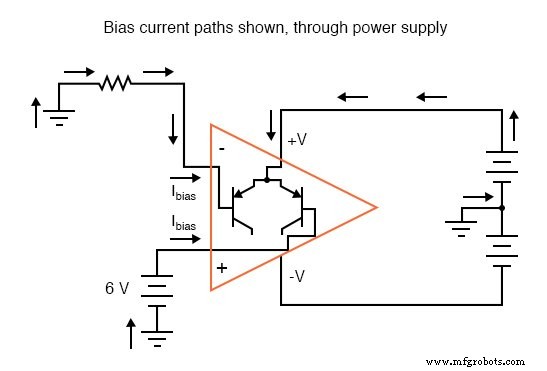

연산 증폭기 회로를 구축하는 방법을 막 배우는 학생들이 가끔 경험하는 관련 문제는 전원 공급 장치에 대한 공통 접지 연결 부족으로 인해 발생합니다. 필수적입니다. DC 전원 공급 장치의 일부 단자가 입력 신호의 "접지" 연결에 공통인 적절한 연산 증폭기 기능. 이것은 바이어스 전류, 피드백 전류 및 부하(출력) 전류에 대한 완전한 경로를 제공합니다. 예를 들어 적절하게 접지된 전원 공급 장치를 보여주는 다음 회로 그림을 참조하십시오.

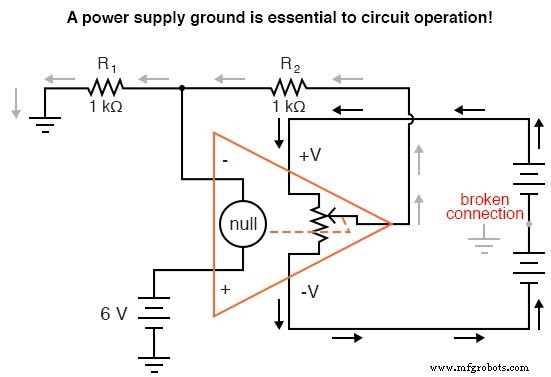

여기서 화살표는 연산 증폭기의 내부 회로(출력 전압을 제어하는 내부의 "전위차계")에 전력을 공급하고 저항 R의 피드백 루프에 전력을 공급하기 위해 전원 공급 장치 배터리를 통한 전자 흐름의 경로를 나타냅니다. 1 및 R2 . 그러나 이 "분할" DC 전원 공급 장치의 접지 연결을 제거해야 한다고 가정합니다. 이렇게 하면 엄청난 효과를 볼 수 있습니다.

전원 공급 장치로의 경로가 "막다른 골목"이기 때문에 연산 증폭기의 출력 단자 안팎으로 전자가 흐르지 않을 수 있습니다. 따라서 R1 왼쪽의 접지 연결을 통해 전자가 흐르지 않습니다. , 피드백 루프를 통해서도 아닙니다. 이것은 효과적으로 연산 증폭기를 무용지물로 만듭니다. 전원 공급 장치의 어떤 지점에서도 접지로 연결되어 있지 않기 때문에 피드백 루프나 접지된 부하를 통해 전류를 유지할 수 없습니다.

바이어스 전류는 전원 공급 장치와 접지를 통한 입력 소스로의 경로에 의존하기 때문에 중지됩니다. 다음 다이어그램은 바이어스 전류가 연산 증폭기의 입력 단자를 통과하고 입력 트랜지스터의 베이스 단자를 통과하고 결국 전원 공급 단자를 통과하여 접지로 돌아갈 때(만)를 보여줍니다.

전원 공급 장치에 접지 기준이 없으면 바이어스 전류는 회로에 대한 완전한 경로를 갖지 않으며 중단됩니다. 바이폴라 접합 트랜지스터는 전류 제어 장치이기 때문에 연산 증폭기의 입력 단계도 무용지물이 됩니다. 두 입력 트랜지스터 모두 베이스 전류가 완전히 부족하여 강제로 차단되기 때문입니다.

검토:

<울>반도체 장치이기 때문에 연산 증폭기는 작동 온도의 변화에 따라 동작이 약간 변경될 수 있습니다. 온도에 따른 연산 증폭기 성능의 모든 변화는 연산 증폭기 드리프트 범주에 속합니다. . 바이어스 전류, 오프셋 전압 등에 대해 드리프트 매개변수를 지정할 수 있습니다. 특정 연산 증폭기에 대한 자세한 내용은 제조업체의 데이터 시트를 참조하십시오.

연산 증폭기 드리프트를 최소화하기 위해 최소 드리프트를 갖도록 만든 연산 증폭기를 선택하거나 작동 온도를 가능한 한 안정적으로 유지하기 위해 최선을 다할 수 있습니다. 후자의 작업은 연산 증폭기를 수용하는 장비 내부에 대한 온도 제어의 일부 형태를 제공하는 것을 포함할 수 있습니다. 이것은 처음 보이는 것처럼 이상하지 않습니다. 예를 들어 실험실 표준 정밀 전압 기준 생성기는 민감한 구성 요소(예:제너 다이오드)를 일정한 온도로 유지하기 위해 "오븐"을 사용하는 것으로 알려져 있습니다. 비용과 유연성이라는 일반적인 요소보다 매우 높은 정확도가 필요한 경우 고려할 가치가 있는 옵션일 수 있습니다.

검토:

<울>엄청나게 높은 차동 전압 이득을 가진 연산 증폭기는 피드백 발진으로 알려진 현상의 주요 후보입니다. . You’ve probably heard the equivalent audio effect when the volume (gain) on a public-address or other microphone amplifier system is turned too high:that high pitched squeal resulting from the sound waveform “feeding back” through the microphone to be amplified again. An op-amp circuit can manifest this same effect, with the feedback happening electrically rather than audibly.

A case example of this is seen in the 3130 op-amp, if it is connected as a voltage follower with the bare minimum of wiring connections (the two inputs, output, and the power supply connections). The output of this op-amp will self-oscillate due to its high gain, no matter what the input voltage. To combat this, a small compensation capacitor must be connected to two specially-provided terminals on the op-amp. The capacitor provides a high-impedance path for negative feedback to occur within the op-amp’s circuitry, thus decreasing the AC gain and inhibiting unwanted oscillations. If the op-amp is being used to amplify high-frequency signals, this compensation capacitor may not be needed, but it is absolutely essential for DC or low-frequency AC signal operation.

Some op-amps, such as the model 741, have a compensation capacitor built in to minimize the need for external components. This improved simplicity is not without a cost:due to that capacitor’s presence inside the op-amp, the negative feedback tends to get stronger as the operating frequency increases (that capacitor’s reactance decreases with higher frequencies). As a result, the op-amp’s differential voltage gain decreases as frequency goes up:it becomes a less effective amplifier at higher frequencies.

Op-amp manufacturers will publish the frequency response curves for their products. Since a sufficiently high differential gain is absolutely essential to good feedback operation in op-amp circuits, the gain/frequency response of an op-amp effectively limits its “bandwidth” of operation. The circuit designer must take this into account if good performance is to be maintained over the required range of signal frequencies.

검토:

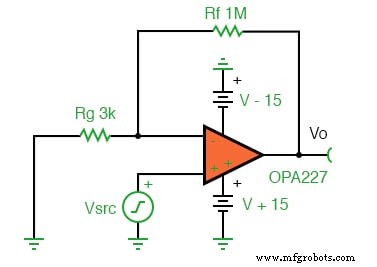

<울>In order to illustrate the phase shift from input to output of an operational amplifier (op-amp), the OPA227 was tested in our lab. The OPA227 was constructed in a typical non-inverting configuration (Figure below).

OPA227 Non-inverting stage

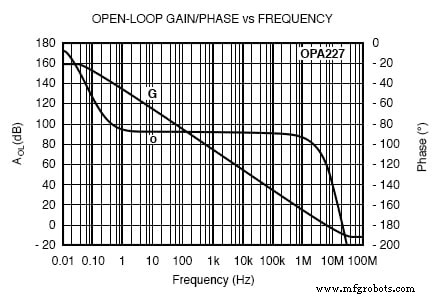

The circuit configuration calls for a signal gain of ≅34 V/V or ≅50 dB. The input excitation at Vsrc was set to 10 mVp, and three frequencies of interest:2.2 kHz, 22 kHz, and 220 MHz. The OPA227’s open loop gain and phase curve vs. frequency is shown in Figure below.

AV and Φ vs. Frequency plot

To help predict the closed loop phase shift from input to output, we can use the open loop gain and phase curve. Since the circuit configuration calls for a closed loop gain, or 1/β, of ≅50 dB, the closed loop gain curve intersects the open loop gain curve at approximately 22 kHz. After this intersection, the closed loop gain curve rolls off at the typical 20 dB/decade for voltage feedback amplifiers, and follows the open loop gain curve.

What is actually at work here is the negative feedback from the closed loop modifies the open loop response. Closing the loop with negative feedback establishes a closed loop pole at 22 kHz. Much like the dominant pole in the open loop phase curve, we will expect phase shift in the closed loop response. How much phase shift will we see?

Since the new pole is now at 22 kHz, this is also the -3 dB point as the pole starts to roll off the closed loop again at 20 dB per decade as stated earlier. As with any pole in basic control theory, phase shift starts to occur one decade in frequency before the pole, and ends at 90 o of phase shift one decade in frequency after the pole. So what does this predict for the closed loop response in our circuit?

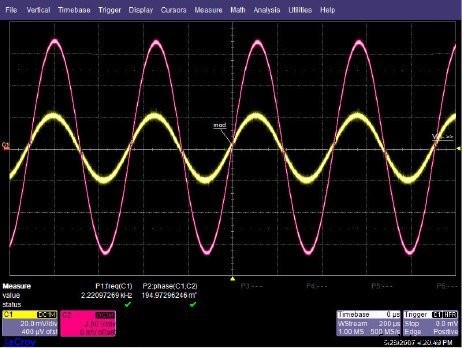

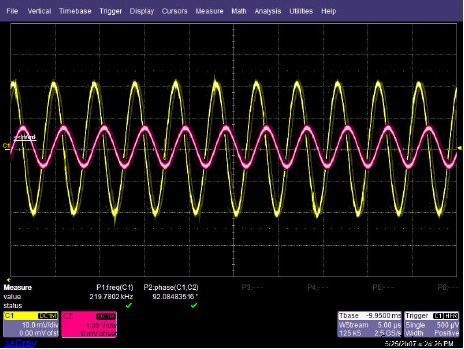

This will predict phase shift starting at 2.2 kHz, with 45 o of phase shift at the -3 dB point of 22 kHz, and finally ending with 90 o of phase shift at 220 kHz. The three Figures shown below are oscilloscope captures at the frequencies of interest for our OPA227 circuit. Figure below is set for 2.2 kHz, and no noticeable phase shift is present. Figure below is set for 220 kHz, and ≅45 o of phase shift is recorded. Finally, Figure below is set for 220 MHz, and the expected ≅90 o of phase shift is recorded. The scope plots were captured using a LeCroy 44x Wavesurfer. The final scope plot used a x1 probe with the trigger set to HF reject.

OPA227 Av=50dB @ 2.2 kHz

OPA227 Av=50dB @ 22 kHz

OPA227 Av=50dB @ 220 kHz

관련 워크시트:

<울>Inverting and Noninverting OpAmp Voltage Amplifier Circuits Worksheet

산업기술

전력 용량 이미 관찰한 바와 같이 변압기는 수용 가능한 전력 결합, 엄격한 전압 조정 및 낮은 여자 전류 왜곡을 달성하기 위해 잘 설계되어야 합니다. 또한 변압기는 1차 및 2차 권선 전류의 예상 값을 문제 없이 전달할 수 있도록 설계해야 합니다. 이는 권선 도체가 가열 문제를 방지하기 위해 적절한 게이지 와이어로 만들어져야 함을 의미합니다. 이상적인 변압기 이상적인 변압기는 완벽한 커플링(누설 인덕턴스 없음), 완벽한 전압 조정, 완벽한 사인파 여자 전류, 히스테리시스 또는 와전류 손실이 없고 모든 양의 전류를 처리할 수 있

저잡음 증폭기 설계의 주요 기능은 작은 전력 신호를 증폭하는 것입니다. 전자 마이크에서 메시지는 전압 또는 전류, 가변 w.r.t일 수 있습니다. 시간. 모든 증폭기와 마찬가지로 저잡음 증폭기도 2포트 회로입니다. 입력 신호의 진폭을 향상시키기 위해 전력을 소비합니다. 그 결과 비례 출력 신호가 높아집니다. 이 문서에서는 LNA 설계에 대해 염두에 두어야 할 10가지 실용적인 고려 사항에 대해 설명합니다. 저잡음 증폭기 설계 – 저잡음 수치는 더 나은 LNA 성능을 제공합니다. 저잡음 증폭기는 여러 장치에서 중요한 구성 요소입니