산업기술

스위칭 전원 공급 장치 기술은 최근 몇 년 동안 고집적 칩의 개발과 함께 소형, 고주파 및 고효율로의 발전을 목격했습니다. 고집적 제어 칩은 설계 소프트웨어에 따라 스위치 전원 공급 장치를 설계하기가 비교적 쉽기 때문에 필요한 주변 부품을 단순화합니다. 그러나 고집적화의 문제는 낮은 설계 자유도, 낮은 칩 가용성 및 낮은 가격으로 이어집니다. 각 제조업체에서 개발한 설계 소프트웨어는 일부 유형의 고유한 칩을 시뮬레이션할 수 있습니다. 실제 적용에서는 우수한 작동 조건과 함께 제품 요구 사항과 호환되는 스위치 전원 공급 장치를 설계하는 것이 중요합니다. RFID용 전원 모듈의 요구 사항에 따라 스위치 전원은 220VAC ~ 0.5VDC의 전압과 88mm x 70mm 크기로 설계되었습니다. 태그를 읽는 과정에서 동작 전류는 1.5A에 가깝기 때문에 설계된 스위치 전원의 최대 출력 전류는 3A로 설정됩니다.

Erickson RW 이론에 따르면 상대적으로 출력 전력이 낮은 소형 설계에서 플라이백 스위치 전력의 전력 스위치 가용성 0.385는 일반 쇼크, 풀 브리지 및 하프 브리지 유형을 사용하는 0.353 이상입니다. 따라서 플라이백 변환기 구조가 선택됩니다. 피드백 설계 및 전류 모드 컨트롤러의 장점을 고려하여 전류 모드 PWM 제어 칩 UC3842가 선택되었습니다.

칩 UC3842를 적용한 스위치 전원에서 주변 회로 설계는 비교적 쉽습니다. 전류 모드 PWM 제어 칩 구조는 피드백 루프의 설계를 효과적으로 단순화하기 위해 루프에서 인덕턴스로 인한 이중 극을 제거합니다. 스태빌로볼트관 TL431과 옵토커플러로 구성된 출력단자 피드백 스타일이 적용되었습니다. UC3842 기반 설계에서 설계자는 플라이백 구조에서 각 모듈을 독립적으로 설계하는 경향이 있으며 인접 회로 및 피드백 회로 설계를 강조하고 다른 회로 설계는 무시합니다. 예를 들어, Middlebrook 박사의 추가 요소 정리에 따르면 입력 필터의 입력 임피던스는 컨버터의 입력 임피던스보다 훨씬 작아야 합니다. 그렇지 않으면 회로에 변동이 발생할 수 있습니다. 이 설계에서는 입력 필터의 회로 설계, 기울기 보상 및 접지 회로 설계와 같은 인접 회로 설계를 주의 깊게 논의합니다. 설계 방식은 Saber 시뮬레이션을 통해 결정되며 RFID를 통한 디버깅을 통해 요구 사항과의 호환성 및 안정성을 제공합니다.

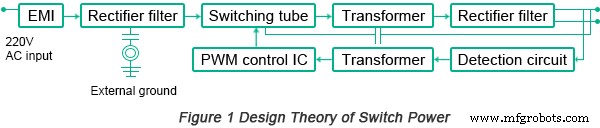

스위치 전원의 기본 설계 이론은 VAC를 VDC로 변환하여 IC 칩에 공급되는 전원을 DC에서 HFAC로 변환한 다음 DC 출력으로 변경하는 것입니다. 피드백은 출력 DC 샘플과 입력 IC 제어 스위치의 출력 전압을 안정화합니다. 스위치 전력 이론은 그림 1에 나와 있습니다.

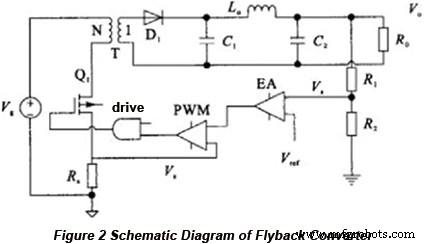

전류 모드 이중 폐쇄 루프 구조는 플라이백 스위치 전원의 제어 변환기에 적용됩니다. 플라이백 컨버터의 특징은 개폐관이 닫힌 상태에서는 변압기 한쪽 코일 내부의 인덕턴스 에너지가 정류 다이오드를 통해 캐리어에 전력을 공급하고 개폐관이 열린 상태에서는 내부에 에너지가 저장된다는 점에 있습니다. 변압기 코일과 출력은 출력 커패시터 내부에 저장된 에너지에 의해 제공됩니다. 플라이백 컨버터의 개략도는 그림 2에 나와 있습니다.

출력 검출 저항 R1에 의해 검출된 전압일 때 및 R2 기준 전압 Vref보다 작습니다. , 스위칭 튜브 Q1가 있는 오류 증폭기를 통해 오류가 증가합니다. 열려 있는. 변압기의 1차 인덕턴스와 전류는 (Vg의 기울기만큼 상승합니다. - Von )/ Lm . 샘플링 저항 Rs 1차 인덕턴스와 전류를 샘플링 전압으로 변경합니다. 샘플링 저항 Rs의 샘플링 전압 비교 기준 및 오류 전압, 샘플링 저항 Rs의 전압 에러 전압보다 높은 값으로 상승하면 Low 레벨이 출력되고 스위칭 튜브는 다음 클럭이 올 때까지 닫힙니다. 플라이백 스위칭 전원은 출력 전원 인덕터가 필요하지 않으며, 간단한 토폴로지 구조를 특징으로 하는 전원에 변압기의 인덕터를 직접 적용할 수 있습니다. 제어 회로는 주로 현재 모드 PWM 칩 UC3842 및 주변 회로에 따라 달라집니다.

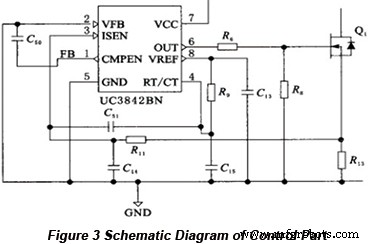

이 설계에 적용된 제어 CPU는 고정 주파수 및 전류 모드의 PWM 칩 UC3842이며 발진기, 오류 증폭기, PWM 비교기 및 SR 트리거와 같은 중요한 제어 구성 요소를 통합합니다. 이 칩은 토템 폴의 출력 모드, 500kHz의 작동 주파수, 1mA 미만의 시작 전류 및 1A의 최대 출력 전류로 저전압 및 과전류 보호 기능을 제공합니다.

핀의 기능은 서로 다릅니다. 핀 7은 전원 공급용입니다. 전압이 16V의 느린 시작 임계값 이상일 때 슈미트 트리거는 높은 레벨을 출력합니다. 전압 조정기는 5V의 기준 전압을 핀 8에 공급하고 전압이 10V보다 낮으면 Schmitt 트리거는 저전압이 잠긴 상태에서 로우 레벨을 출력합니다. 내부 stabilivolt 튜브는 최대 입력 전압을 36V 이내로 제한합니다. Ct에 전원 공급 외부 RC 회로를 통한 핀 4 및 저항 Rt를 통한 핀 8 및 Ct 전기를 생성하는 내부 전류원을 통해 발진기의 주파수를 결정합니다. 핀 2는 오차 증폭기의 반전 입력이고 핀 1은 보상을 제공하기 위한 오차 증폭기의 출력입니다. 핀 3은 전류 감지 핀으로 오차 증폭기의 출력을 통해 듀티 사이클을 결정하고 핀 3의 전압이 1V 이상이면 전류 흐름이 닫힙니다. 핀 6은 최대 작동 전류 1A로 토템 폴 모드 출력을 공급하여 스위칭 튜브의 폐쇄를 가속화합니다.

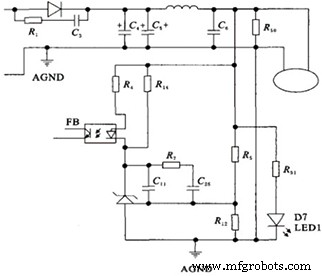

제어부의 개략도는 아래 그림 3과 같습니다. 플라이백 컨버터의 제어 부분은 대부분 UC3842 칩 내부에 통합되어 있으며 필요한 제어 기능을 구현할 수 있는 외부 부품은 몇 개뿐입니다. 주요 제어 기능 모듈에는 시동 회로, 주파수 설계, 보호 회로, 구동 회로 및 기울기 보상이 포함됩니다.

• 시작 회로 및 주파수 설계

시동 회로는 16V 이상의 핀 7 시동 전압을 공급합니다. 시스템이 시작되면 보조 권선에 의해 핀 7에 전원이 공급됩니다. 이 시스템의 작동 주파수는 타이밍 커패시터와 핀 8과 핀 4 사이의 저항에 의해 결정됩니다. 핀 8의 5V 기준 전압은 커패시터 C15에 전원을 제공합니다. 저항 R9를 통해 . 커패시터 C15 그런 다음 PWM을 출력하는 칩의 데드 타임을 결정하는 시간 범위의 전기를 생성하는 내부 전류 소스를 통해 톱니파를 생성합니다. 성능을 보장하기 위해서는 데드 타임이 발진 주기보다 5% 이상 작아야 합니다. 타이밍 시퀀스 다이어그램을 기반으로 C15 3.3nF이고 작동 주파수는 47kHz입니다. fosc 공식에 따라 =1.7/( R참조 x C15 ), R9의 값 11kHz입니다.

• 현재 폴드백 회로

칩의 전류 폴드백 회로는 1차 에지의 인덕터 전류를 과전류 감지 저항을 통해 PWM 비교기로 구현된 전압 및 오차 증폭기의 출력 전압으로 변환합니다. 핀 3의 전압이 1V 이상이면 출력이 끊어집니다. 피크 인덕터 전류는 1A로 가정하고 전류 감지 저항 R13의 값 1Ω이라고 가정합니다. 변압기 1차 에지의 인덕터 전류 피크로 인한 오류 차단을 방지하기 위해 R11 및 C14 피크를 필터링하기 위해 액세스되며 피크 전류는 약 수백 나노초입니다. R11이 1k이고 C14가 500pF인 조건에서 시정수 τ =RC =500ns입니다.

• MOS 튜브의 구동회로

MOS 튜브의 구동 회로는 PWM의 우수한 파형, 특히 폴 에지를 담당합니다. 출력 핀 6과 그리드 직렬 저항 R6 사이의 직렬 연결 MOS 튜브 입력 커패시턴스와 회로의 직렬 리드 인덕턴스로 인한 고주파수 기생 변동을 감소시킵니다. MOS 튜브 스위치 PWM 파형을 보장하기 위해 R6의 값 는 항상 수십 옴에서 20옴 범위에서 작습니다. R8의 값 MOS 튜브 그리드 블리더 저항으로 15kΩ이 되어야 합니다.

• 기울기 보상

피크 전류 모드 제어에서 인덕터 전류의 피크 값은 일정하게 설정되지만 인덕터 전류의 평균 값은 설정되지 않습니다. 듀티 사이클의 변화는 평균 전류를 변화시키고 피크 전류 제어의 내부 링은 인덕터 전류의 피크 값을 보장하지만 출력 전압과 호환되는 올바른 인덕터 전류 평균 값을 제어하지 못하여 출력 전압의 지속적인 변화를 초래합니다. 듀티 사이클이 50% 이상이면 인덕터 전류 변동으로 인해 발진이 발생합니다. 이 설계에서는 기울기 보상이 필요합니다. 상부 기울기 보상의 적용은 현재 샘플 신호에 대한 양의 기울기 전압 스택을 나타냅니다. C51을 사용하여 이 설계에 정전 용량 보상이 적용됩니다. 핀 3과 핀 4 사이에 추가된 100pF의 전압과 발진기의 발진 신호는 C51에 전원을 공급합니다. 커패시터를 통한 핀 3. 이러한 유형의 기울기 보상을 사용하면 오실레이터의 전류를 끌어들이고 핀 3에서 너무 큰 음의 전압을 생성하는 것을 방지하기 위해 커패시턴스가 pF 등급으로 상대적으로 작습니다.

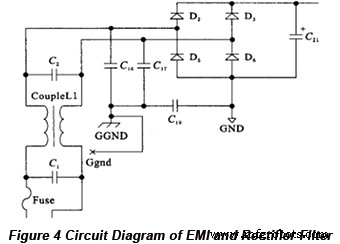

• EMI 및 정류기 필터용 회로 설계

고주파 전력망이 장치에 간섭하고 고주파 스위치가 전력망에 미치는 영향을 필터링하려면 EMI 필터 회로에 입력 랭크로 액세스해야 합니다. 공통 EMI 필터파의 회로도는 그림 4와 같습니다.

C1 C2 동안 전력망의 입력 포트에 연결됩니다 차동 모드 간섭을 제거하기 위해 장치의 입력 포트가 있습니다. L은 공통 모드 초크와 동일한 방향을 공유하여 공통 모드 간섭을 필터링하는 반면 C16 및 C17 공통 모드 간섭을 필터링하기 위해 접지에 연결됩니다.

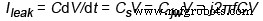

C16의 누설 전류 및 C17 다음 공식에 따라 계산됩니다.  . 두 개의 동일한 커패시터의 경우 누설 전류의 진폭은 다음 공식을 따라야 합니다.

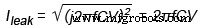

. 두 개의 동일한 커패시터의 경우 누설 전류의 진폭은 다음 공식을 따라야 합니다.  , 여기서 f는 50Hz의 값을 갖는 전력망의 주파수를 나타내고, C는 전체 커패시턴스를 나타냅니다. 4400pF의 접지 전압, V는 110V의 접지 전압을 나타냅니다. 따라서 Ileak의 값은 0.15mA로 보안규격에 부합하는 EMI 후 유효한 값인 220VAC의 교류전류와 호환됩니다. 진폭은

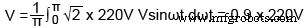

, 여기서 f는 50Hz의 값을 갖는 전력망의 주파수를 나타내고, C는 전체 커패시턴스를 나타냅니다. 4400pF의 접지 전압, V는 110V의 접지 전압을 나타냅니다. 따라서 Ileak의 값은 0.15mA로 보안규격에 부합하는 EMI 후 유효한 값인 220VAC의 교류전류와 호환됩니다. 진폭은  출력 DCV가

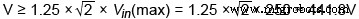

출력 DCV가  . 다이오드의 역방향 항복 전압은 다음 요구 사항을 충족해야 합니다.

. 다이오드의 역방향 항복 전압은 다음 요구 사항을 충족해야 합니다.  . C는 필터 커패시턴스를 나타내고 RL 부하를 나타냅니다. 시정수 RL이 클수록 C 이고 캐패시턴스가 매끄러울수록 필터 효과가 더 좋습니다. 내전압이 높은 다이오드 ln4007을 픽업합니다.

. C는 필터 커패시턴스를 나타내고 RL 부하를 나타냅니다. 시정수 RL이 클수록 C 이고 캐패시턴스가 매끄러울수록 필터 효과가 더 좋습니다. 내전압이 높은 다이오드 ln4007을 픽업합니다.

• 필터 출력 임피던스와 컨버터 입력 임피던스로 인한 진동

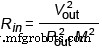

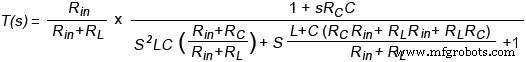

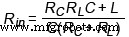

변환기의 입력 임피던스와 필터의 출력 임피던스 사이의 비호환성 역시 발진을 유발할 수 있습니다. 루프 시스템의 변환기의 입력 임피던스는 음의 저항으로 간주될 수 있습니다(  ). Filter는 LC filter이며 전달함수는 인덕턴스와 커패시턴스의 ESR로 구할 수 있다.

). Filter는 LC filter이며 전달함수는 인덕턴스와 커패시턴스의 ESR로 구할 수 있다.

시스템 일정 진동 변환기의 입력 임피던스는 다음 공식을 따라야 합니다.  .

.

따라서 루프 컨버터의 입력 임피던스가 계산된 필터 발진 출력 임피던스보다 작은 경우에만 전달 함수의 감쇠 계수가 양의 값이 되어 발진을 줄이기 위해 안정됩니다. 그렇지 않으면 회로가 변동합니다.

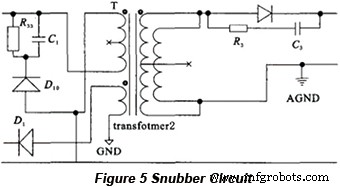

• 스너버 회로 설계

차단 과전압으로 인해 주파수 튜브가 파손되는 것을 방지하려면 1차측 RCD 스너버 회로를 변압기에 조립해야 합니다. 출력 포트는 출력 다이오드를 분해하여 출력 스너버 회로를 추가하여 하드 브레이크다운을 방지합니다(그림 5 참조).

MOS 튜브의 파괴 과정에서 1차 에지 id의 전류 변압기 1차 에지 누설 소스를 통해 기생 누설 소스 커패시턴스에 전원을 공급합니다. 이 고주파수 전압으로 인해 스위치 튜브의 전압이 내전압을 초과하고 스위치 튜브가 파손되어 RCD 스너버 회로가 추가되어 전압 탭핑 경로를 제공할 수 있습니다. 고내압, RCD 저항 5kΩ, 커패시턴스 3300pF의 고속 회복 다이오드 FR107을 선택했습니다.

MOS 튜브가 열린 상태에서 입력이 열리면 출력 쇼트키 다이오드에 전압이 추가됩니다(  ) MOS 튜브의 하드 고장은 다이오드의 고장으로 이어집니다. RC 스너버 회로가 추가되면 쇼트키 다이오드 VD의 전압 =VO + 나O x R3 . MOS 튜브의 2SK792의 개방 시간은 55ns, 쇼트키 다이오드 SB540의 역 내전압은 60V, 출력 VO 최대 전류는 5V이고 최대 전류는 3A입니다. 따라서 최대 스너버 회로의 등가 저항은 18.33Ω이고 (

) MOS 튜브의 하드 고장은 다이오드의 고장으로 이어집니다. RC 스너버 회로가 추가되면 쇼트키 다이오드 VD의 전압 =VO + 나O x R3 . MOS 튜브의 2SK792의 개방 시간은 55ns, 쇼트키 다이오드 SB540의 역 내전압은 60V, 출력 VO 최대 전류는 5V이고 최대 전류는 3A입니다. 따라서 최대 스너버 회로의 등가 저항은 18.33Ω이고 (  ). R이 18Ω이고 C가 560pF일 때 등가 직렬 저항은 18.06Ω입니다.

). R이 18Ω이고 C가 560pF일 때 등가 직렬 저항은 18.06Ω입니다.

• 출력 회로 설계

정류는 쇼트키 다이오드를 통해 출력 부분에서 구현되고 필터링은 그림 6과 같이 등가 커패시터 ESR 감소 출력과 함께 낮은 ESR의 커패시터를 적용합니다.

출력 샘플링 회로는 R5를 통해 얻습니다. 및 R12 차동 전압 및 R12 값 1.5μA인 TL431 출력 단자 전류를 기준으로 결정됩니다. 전류에 영향을 미치는 차동 전압 비율 및 잡음을 피하기 위해 저항 R12을 통과하는 전류 TL431 입력 전류의 100배 이상이어야 합니다. 낮은 <2.5/150μA=16.6kΩ. TL431의 작동 전류는 1mA ~ 100mA 범위이므로 R5의 전류가 가 거의 0이면 1mA의 전류가 R14에 의해 TL431에 제공됩니다. (R14

PC817B의 3극관 특성 곡선을 기준으로 트랜지스터의 순방향 전류가 약 7mA일 때 IC의 값 또한 7mA이고 이미 터 전압은 uc3842comp linear와 함께 비교적 넓은 범주 내에서 선형입니다. PC817B의 CTR은 1.3에서 2.6 사이입니다. IC의 값이 7mA이며 최악의 상황을 고려하면 CTR 값은 1.3입니다. LED를 통해 흐르는 최대 전류는 If이어야 합니다. =나C /1.3 =5.38mA, R4 <(5 - U카 - Uf )/5.38mA =(5 - 1.15 - 2.5)/5.38mA =250Ω. TL431이 견딜 수 있는 최대 전류는 150mA이고 PC817이 견딜 수 있는 최대 전류는 50mA입니다. 따라서 최대 전류 R4 R4에서 50mA 제공>(5 - 1.15 - 2.5)/50mA =27Ω. 따라서 R4의 범위는 150Ω의 값이 선택된 상태에서 27Ω과 250Ω 사이입니다.

• 접지 회로 설계

변압기는 스위치 전원의 저온 접지와 고온 접지 사이의 접지 절연체에 적용됩니다. 변압기의 1차 가장자리에 있는 뜨거운 접지는 전기 그리드를 통해 루프로 형성될 수 있으며 2차 변압기는 차가운 접지와 접지에 의해 형성된 루프를 나타냅니다. 안전 커패시터 Y는 C16에 의해 선택됩니다. 및 C17 제로 라인과 발사 라인을 프레임 접지에 연결하여 공통 모드 간섭을 필터링합니다. 커패시터 C18 고온 접지와 저온 접지 사이는 변압기 2차측의 노이즈를 1차 단락으로 변환하여 방사 전자파를 줄입니다.

유용한 리소스

• RFID 기반 IoT 종합 소개

• 고온 환경에서 고전력 PCB 설계

• PCB 설계에서 절연 감소를 기반으로 제어 전원 공급 장치 접지 결함을 해결하는 방법

• PCB의 전자기 호환성에서 전력 및 접지에 대한 논의

• 고속 PCB 전력의 임피던스를 분석하고 금지하는 방법

• 알루미늄 지지 PCB:고전력 및 엄격한 허용 오차 애플리케이션에 대한 솔루션

• PCBCart의 전체 기능 PCB 제조 서비스 - 다양한 부가 가치 옵션

• PCBCart의 고급 PCB 조립 서비스 - 1개부터 시작

산업기술

압전 구동 회로 정보 ,종종 온도, 음압 및 기계적 응력과 같은 물리량을 측정해야 합니다. 변환기는 그러한 양을 측정하는 데 사용할 수 있는 모든 장치입니다. 일반적으로 변환기가 하는 일은 기계적 신호를 전기적 신호로 변환하는 것입니다. 많은 종류의 변환기가 존재하며 압전 변환기가 그 중 하나입니다. 이 변환기를 사용하는 모든 장치는 물리량을 전기 신호로 변환할 수 있습니다. 그럼에도 불구하고 백만 달러짜리 질문은 압전 변환기가 어떻게 작동합니까? 이 피에조 드라이브 회로 가이드는 이 시스템의 회로와 공통 설계 기술에 대해

최근 몇 년 동안 전자 제품의 소형화, 무결성 및 모듈화가 목격되어 전자 부품의 조립 밀도 측면에서 확대되고 효과적인 방열 면적 측면에서 감소로 이어집니다. 따라서 고전력 전자 부품의 열 설계 및 보드 수준의 열 발산 문제가 전자 엔지니어들 사이에서 널리 퍼져 있습니다. FPGA(Field Programmable Gate Array) 시스템의 경우 열 방출은 칩이 정상적으로 작동할 수 있는지 여부를 결정하는 핵심 기술 중 하나입니다. PCB 열 설계의 목적은 적절한 온도에서 시스템이 작동하도록 적절한 조치와 방법을 통해 부품과 보드