임베디드

ADC(아날로그-디지털 변환기)의 샘플링 현상은 앨리어싱 및 용량성 반동 문제를 유발하며 이러한 문제를 해결하기 위해 설계자는 필터와 구동 증폭기를 사용하여 고유한 과제를 제시합니다. 이로 인해 중간 대역폭 애플리케이션 영역에서 정밀한 dc 및 ac 성능을 달성하는 것이 어려워지고 설계자는 이를 위해 시스템 목표를 절충하게 됩니다.

이 기사에서는 신호 체인을 단순화하여 샘플링 문제를 근본적으로 극적으로 해결하는 연속 시간 시그마-델타(∑-Δ) ADC에 대해 설명합니다. 안티앨리어싱 필터와 버퍼의 필요성을 제거하고 추가 구성요소와 관련된 신호 체인 오프셋 오류 및 드리프트 문제를 해결합니다. 이러한 이점은 솔루션 크기를 줄이고 솔루션 설계를 용이하게 하며 시스템의 위상 일치 및 전체 대기 시간을 개선합니다. 이 기사에서는 또한 이산 시간 변환기와 비교하고 시스템 이점과 연속 시간 시그마-델타 ADC 사용의 제약 사항을 강조합니다.

샘플링 기초

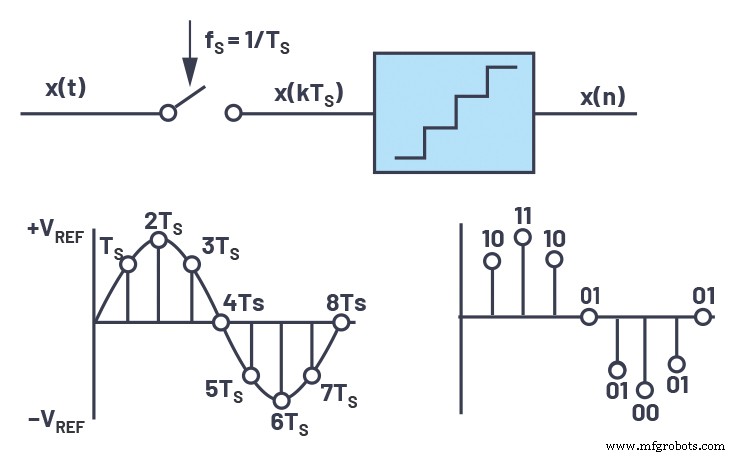

데이터의 디지털화에는 그림 1과 같이 샘플링과 양자화의 두 가지 기본 프로세스가 포함됩니다. 샘플링은 샘플링을 사용하여 연속 시간 변화 아날로그 신호 x(t)를 이산 시간 신호 x(n)로 변환하는 첫 번째 단계입니다. 주파수 fS. 결과는 1/TS(fS =1/TS)의 기간으로 균등하게 구분됩니다.

더 큰 이미지를 보려면 클릭하세요.

그림 1. 데이터 샘플링. (출처:Analog Devices)

두 번째 단계는 이러한 이산 시간 샘플의 값을 유한한 가능한 값 중 하나로 근사화하고 그림 1과 같이 디지털 코드로 표시하는 양자화입니다. 유한한 값 집합에 대한 이러한 양자화는 양자화 노이즈.

샘플링 프로세스는 또한 입력 신호에서 폴드백과 샘플 및 홀드 클럭 주파수 주변의 고조파를 보는 앨리어싱을 발생시킵니다. 나이퀴스트 기준은 샘플링 주파수가 신호에 포함된 가장 높은 주파수의 최소 두 배 이상이어야 합니다. 샘플링 주파수가 최대 아날로그 신호 주파수의 2배 미만이면 앨리어싱(aliasing)이라는 현상이 발생합니다.

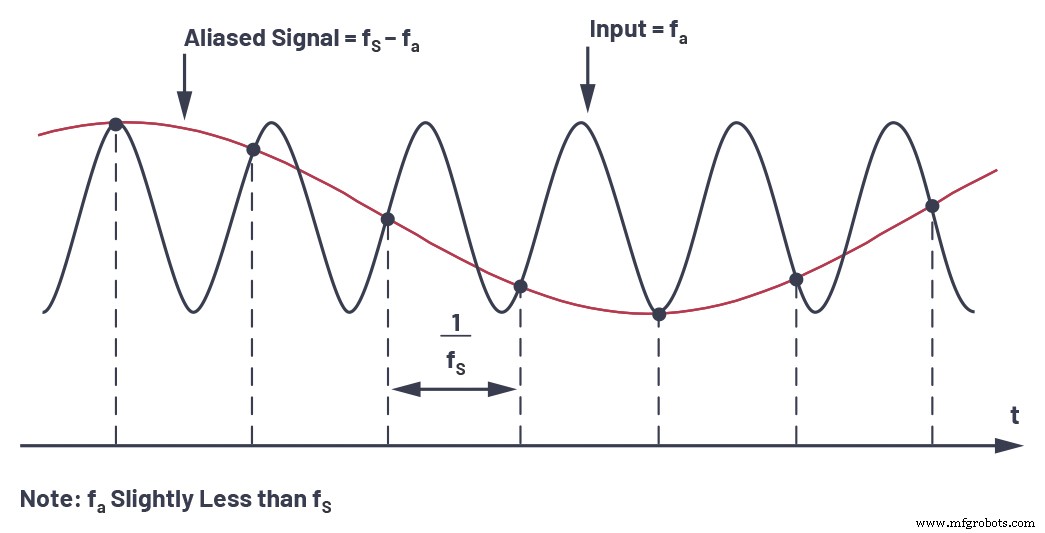

시간 영역과 주파수 영역 모두에서 앨리어싱의 의미를 이해하려면 먼저 그림 2와 같이 샘플링된 단일 톤 사인파의 시간 영역 표현의 경우를 고려하십시오. 이 예에서 샘플링 주파수 fS는 최소 2fa이지만 아날로그 입력 주파수 fa보다 약간 높으므로 Nyquist 기준을 충족하지 못합니다. 실제 샘플의 패턴은 fS – fa와 같은 더 낮은 주파수에서 앨리어싱된 사인파를 생성합니다.

더 큰 이미지를 보려면 클릭하세요.

그림 2. 앨리어싱:시간 영역에서의 표현. (출처:Analog Devices)

더 큰 이미지를 보려면 클릭하세요.

그림 3. 앨리어싱:주파수 영역에서의 표현. (출처:Analog Devices)

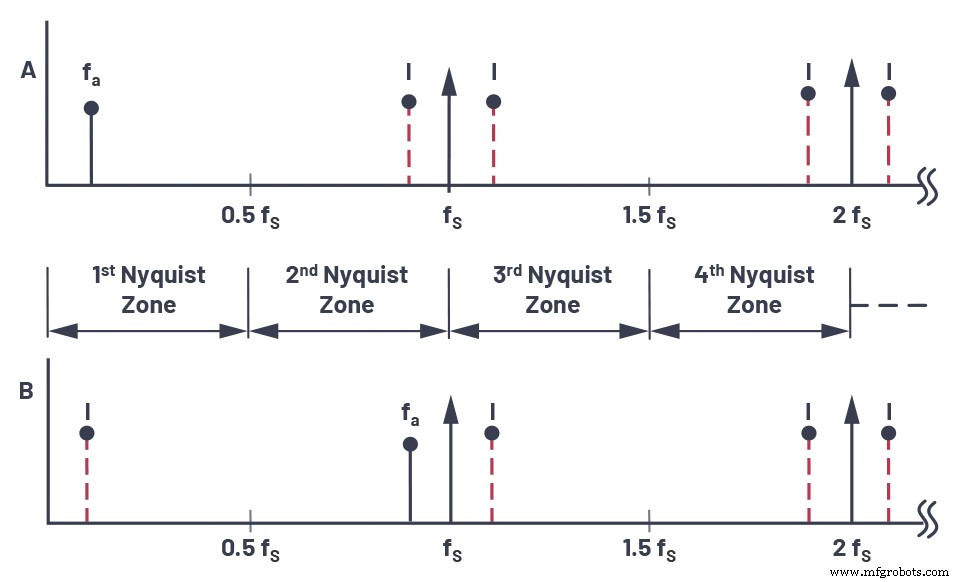

이 시나리오의 해당 주파수 영역 표현은 그림 3에 나와 있습니다.

나이퀴스트 대역폭은 dc에서 fS/2까지의 주파수 스펙트럼으로 정의됩니다. 주파수 스펙트럼은 각각 0.5fS와 같은 너비를 갖는 무한한 수의 Nyquist 영역으로 나뉩니다. 실제로 이상적인 샘플러는 ADC와 FFT 프로세서로 대체됩니다. FFT 프로세서는 dc에서 fS/2로의 출력만 제공합니다. 즉, 첫 번째 나이퀴스트 영역에 나타나는 신호 또는 별칭입니다.

이상적인 임펄스 샘플러에 의해 주파수 fS에서 샘플링된 주파수 fa의 단일 주파수 사인파의 경우를 고려하십시오(그림 1 참조). 또한 fS> 2fa라고 가정합니다. 샘플러의 주파수 도메인 출력은 fS의 모든 배수 주위에 원래 신호의 앨리어스 또는 이미지를 보여줍니다. 즉, | ± KfS ± fa|, K =1, 2, 3, 4 등.

이제 그림 3의 첫 번째 나이퀴스트 영역 외부에 있는 신호의 경우를 생각해 보십시오. 신호 주파수는 그림 2의 시간 도메인 표현에 표시된 조건에 해당하는 샘플링 주파수보다 약간 작습니다. 신호가 첫 번째 나이퀴스트 영역 외부에 있으면 해당 이미지(또는 별칭) fS – fa가 내부에 포함됩니다. 그림 3으로 돌아가서 원치 않는 신호가 fa의 이미지 주파수 중 하나에서 나타나면 fa에서도 발생하여 첫 번째 Nyquist 영역에서 스퓨리어스 주파수 성분을 생성한다는 것이 분명합니다.

정밀 성능을 위한 도전 과제

고성능 애플리케이션의 경우 시스템 설계자는 샘플링 프로세스로 인한 양자화 노이즈, 앨리어싱 및 스위치드 커패시터 입력 샘플링 문제를 해결해야 합니다. 두 가지 유형의 정밀 ADC, 즉 업계에서 사용 가능한 연속 근사 레지스터(SAR)와 시그마-델타 ADC는 스위치드 커패시터 기반 샘플링 기술을 사용하여 설계되었습니다.

양자화 노이즈

이상적인 Nyquist ADC에서 ADC의 LSB 크기는 아날로그-디지털 변환을 수행하는 동안 입력에 추가되는 양자화 노이즈를 결정합니다. 이 양자화 잡음은 fS/2의 대역폭에 걸쳐 퍼집니다. 양자화 노이즈를 방지하기 위한 첫 번째 기술은 Nyquist 주파수보다 훨씬 높은 속도로 입력 신호를 샘플링하여 신호 대 잡음비(SNR)와 분해능(ENOB)을 높이는 오버샘플링입니다. 오버샘플링에서 샘플링 주파수는 N배 Nyquist 주파수(2 × fIN)로 선택되며 결과적으로 동일한 양자화 노이즈가 N배 Nyquist 주파수로 확산되어야 합니다. 이것은 또한 앤티앨리어싱 필터에 대한 요구 사항을 완화합니다. 오버샘플링 비율(OSR)은 fS/2fIN으로 정의되며, 여기서 fIN은 관심 있는 신호 BW입니다. 일반적으로 ADC를 4배로 오버샘플링하면 분해능이 1비트 추가되거나 동적 범위가 6dB 증가합니다. 오버샘플링 비율을 높이면 전체적으로 노이즈가 감소하고 오버샘플링으로 인한 동적 범위(DR) 개선은 dB에서 ΔDR =10log10 OSR입니다.

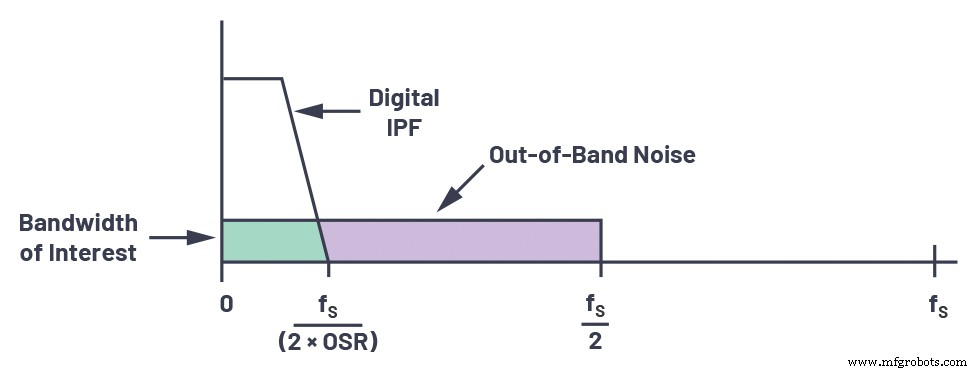

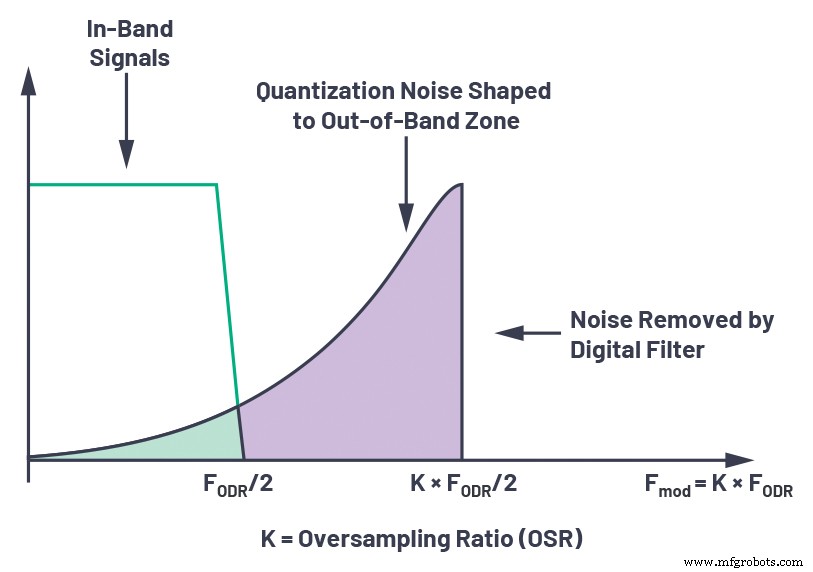

오버샘플링은 본질적으로 통합 디지털 필터 및 데시메이션 기능과 함께 사용 및 구현됩니다. 시그마-델타 ADC의 기본 오버샘플링 변조기는 양자화 잡음을 형성하여 대부분이 해당 대역폭 외부에서 발생하므로 그림 4와 같이 저주파에서 전체 동적 범위가 증가합니다. 디지털 저역 통과 필터(LPF) ) 그런 다음 관심 대역폭 외부의 양자화 노이즈를 제거하고 데시메이터는 출력 데이터 속도를 다시 나이퀴스트 속도로 감소시킵니다.

더 큰 이미지를 보려면 클릭하세요.

그림 4. 오버샘플링의 예. (출처:Analog Devices)

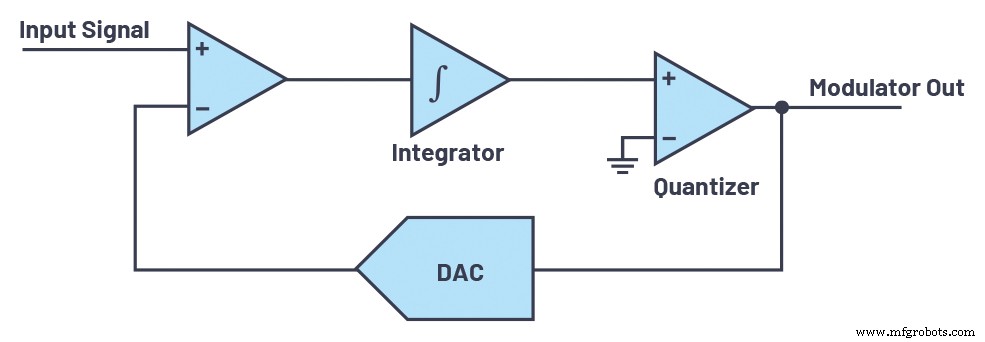

노이즈 쉐이핑은 양자화 노이즈를 줄이는 또 다른 기술입니다. 시그마-델타 ADC에서는 루프 필터 다음 루프 내부에서 저해상도 양자화기(1비트에서 5비트)가 사용됩니다. DAC는 그림 5와 같이 입력에서 양자화된 신호를 빼기 위한 피드백으로 사용됩니다.

더 큰 이미지를 보려면 클릭하세요.

그림 5. 노이즈 쉐이핑. (출처:Analog Devices)

적분기는 양자화 오류를 계속 합산하여 양자화 노이즈를 더 높은 주파수로 형성한 다음 디지털 필터를 사용하여 필터링할 수 있습니다. 그림 6은 일반적인 시그마-델타 ADC의 출력 x[n]의 전력 스펙트럼 밀도(PSD)를 보여줍니다. 잡음 형성 기울기는 루프 필터 H(z)의 차수에 따라 달라지며(그림 11 참조) (20 × n) dB/decade입니다. 여기서 n은 루프 필터 차수입니다. 시그마-델타 ADC는 잡음 형성과 오버샘플링을 결합하여 대역 내 고해상도를 달성합니다. 대역 내 대역폭은 fODR/2와 같습니다(ODR은 출력 데이터 속도를 나타냄). 루프 필터의 차수를 높이거나 오버샘플링 비율을 높이면 더 높은 해상도를 얻을 수 있습니다.

더 큰 이미지를 보려면 클릭하세요.

그림 6. 오버샘플링 및 노이즈 셰이핑 플롯. (출처:Analog Devices)

앨리어싱

고성능 애플리케이션에서 앨리어싱을 방지하기 위해 더 높은 차수의 앤티앨리어싱 필터를 사용하여 폴드백을 방지합니다. 앤티앨리어싱 필터는 입력 신호를 대역으로 제한하고 폴드백할 수 있는 관심 대역폭을 초과하는 신호의 주파수 성분이 없도록 하는 저역 통과 필터입니다. 필터 성능은 대역 외 신호가 fS/2에 얼마나 가까운지와 필요한 감쇠량에 따라 달라집니다.

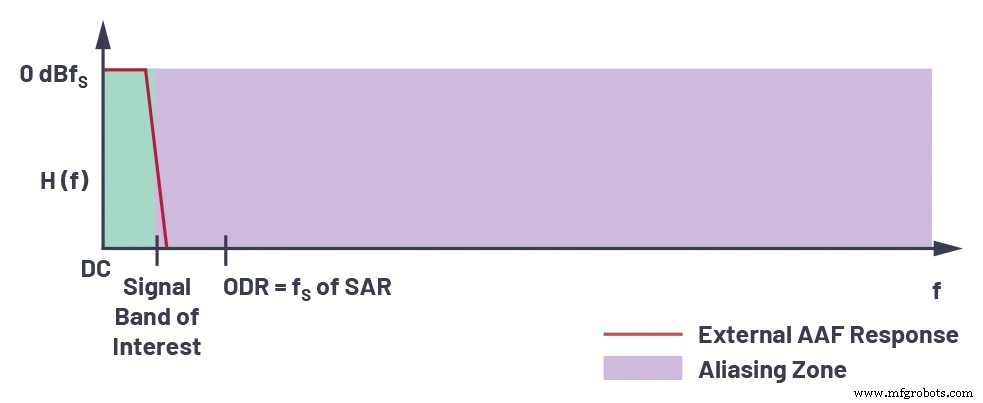

SAR ADC의 경우 입력 신호 BW와 샘플링 주파수 사이의 간격이 크지 않기 때문에 더 많은 전력과 왜곡이 있는 복잡하고 고차 필터 설계를 요구하는 고차 필터가 필요합니다. 예를 들어, 200kSPS 샘플링 속도 SAR의 입력 BW가 100kHz인 경우 앤티앨리어싱 필터는 앨리어싱이 없는지 확인하기 위해>100kHz의 입력 신호를 거부해야 합니다. 이것은 매우 높은 차수의 필터를 필요로 합니다. 그림 7은 급곡선 수요를 보여줍니다.

더 큰 이미지를 보려면 클릭하세요.

그림 7. 별칭 요구 사항. (출처:Analog Devices)

필터 차수를 완화하기 위해 400kSPS의 샘플링 속도를 선택한 경우>300kHz 입력 주파수에 대해 제거가 필요합니다. 샘플링 속도를 높이면 전력이 증가하고 2배 속도의 경우 전력도 2배가 됩니다. 샘플링 주파수가 입력 BW보다 훨씬 높기 때문에 전력을 희생하면서 더 많은 오버샘플링을 수행하면 앤티앨리어싱 필터 요구사항이 더욱 완화됩니다.

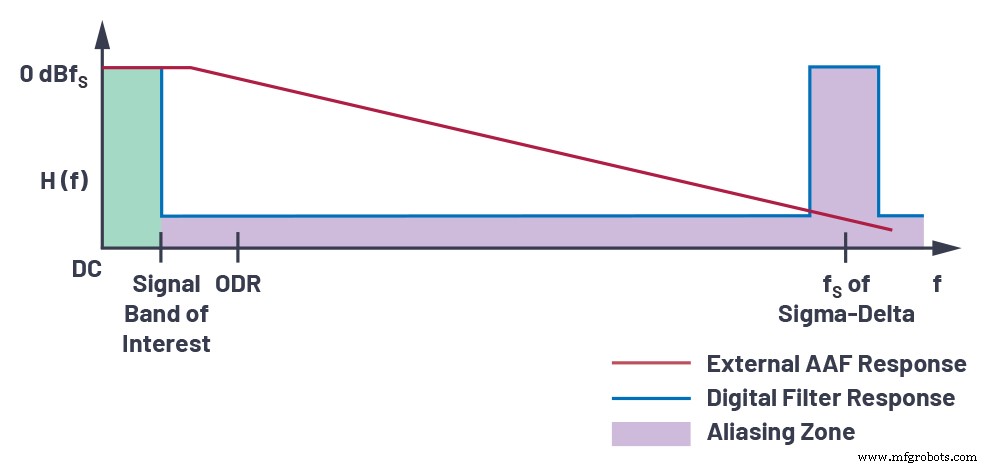

시그마-델타 ADC에서 입력은 훨씬 더 높은 OSR에서 오버샘플링되므로 그림 8과 같이 샘플링 주파수가 입력 BW보다 훨씬 높기 때문에 앤티앨리어싱 필터 요구사항이 완화됩니다.

더 큰 이미지를 보려면 클릭하세요.

그림 8. 시그마-델타에서 앤티앨리어싱 필터 요구 사항. (출처:Analog Devices)

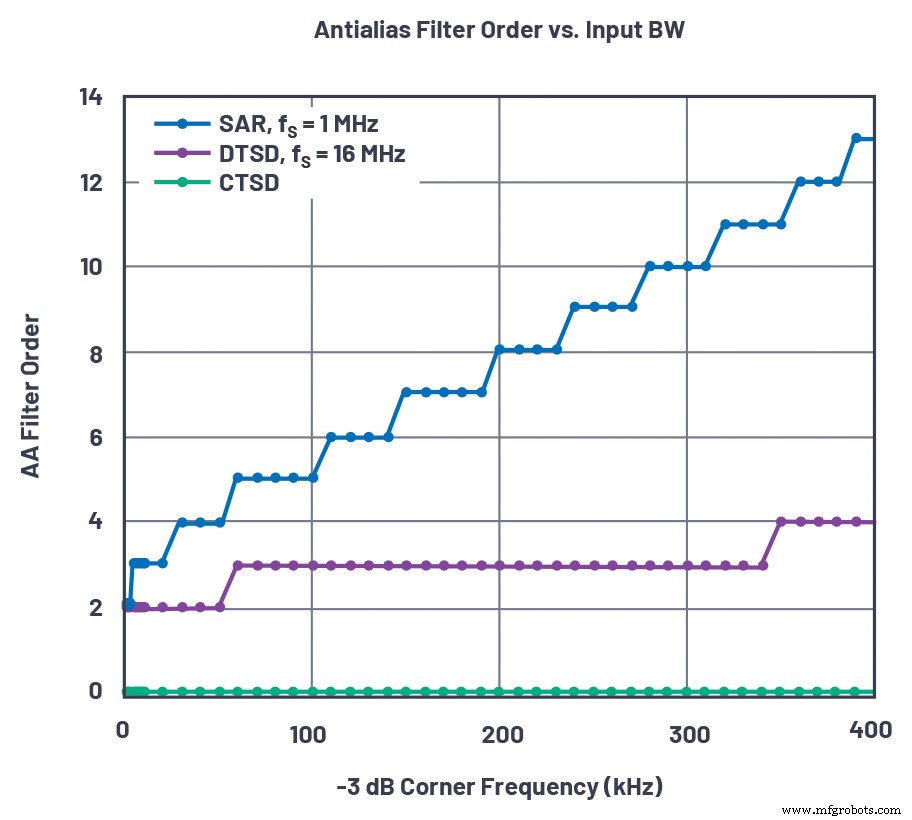

그림 9는 SAR 및 DTSD(discrete-time sigma-delta) 아키텍처에 대한 AAF 복잡성에 대한 아이디어를 제공합니다. 샘플링 주파수 fS에서 102dB 감쇠를 달성하기 위해 100kHz의 -3dB 입력 대역폭을 사용하는 경우 DTSD ADC에는 2차 안티앨리어싱 필터가 필요하고 fS에서 동일한 감쇠를 얻으려면 다음을 사용하는 5차 필터가 필요합니다. SAR ADC.

CTSD(연속 시그마 델타) ADC의 경우 감쇠가 내재되어 있으므로 안티앨리어싱 필터가 필요하지 않습니다.

더 큰 이미지를 보려면 클릭하세요.

그림 9. 다양한 아키텍처에 대한 AAF 필터 요구 사항. (출처:Analog Devices)

이러한 필터는 시스템 설계자에게 골칫거리가 될 수 있으며 관심 대역에서 제공하는 드룹에 대해 필터를 최적화하고 가능한 한 많은 거부를 제공해야 합니다. 또한 오프셋, 게인, 위상 오류 및 노이즈와 같은 다른 많은 오류를 시스템에 추가하여 성능을 저하시킵니다.

또한 고성능 ADC는 본질적으로 차동이므로 두 배의 수동 부품이 필요합니다. 다중 채널 애플리케이션에서 더 나은 위상 일치를 얻으려면 신호 체인의 모든 구성 요소가 잘 일치해야 합니다. 결과적으로 더 엄격한 허용 오차를 가진 구성 요소가 필요합니다.

전환된 커패시터 입력

스위치드 커패시터 입력 샘플링은 커패시터에 대한 샘플링된 입력의 안정화 시간에 의존하므로 샘플링 스위치를 켜거나 끌 때 과도 전류를 충전/방전해야 합니다. 이를 입력에 대한 반동이라고 하며 이러한 과도 전류를 지원할 수 있는 입력 구동 증폭기가 필요합니다. 또한 입력은 샘플링 시간이 끝날 때 안착되어야 하며 샘플링된 입력의 정확도는 ADC의 성능을 결정하므로 구동 증폭기는 킥백 이벤트 이후에 빠르게 안착되어야 합니다. 따라서 빠른 안정화를 지원하고 스위치드 커패시터 작동의 반동을 흡수할 수 있는 고대역폭 드라이버가 필요합니다. 스위치드 커패시터 입력에서 샘플링이 ON일 때마다 드라이버는 즉시 홀드 커패시터에 전하를 공급해야 합니다. 이러한 급격한 전류 급증은 드라이버에 충분한 대역폭 기능이 있는 경우에만 제때에 제공될 수 있습니다. 스위치의 기생으로 인해 샘플링 시 드라이버에서 반동이 발생합니다. 다음 샘플링 전에 반동이 안정되지 않으면 샘플링 오류가 발생하여 ADC 입력이 손상됩니다.

더 큰 이미지를 보려면 클릭하세요.

그림 10. 샘플링 반동. (출처:Analog Devices)

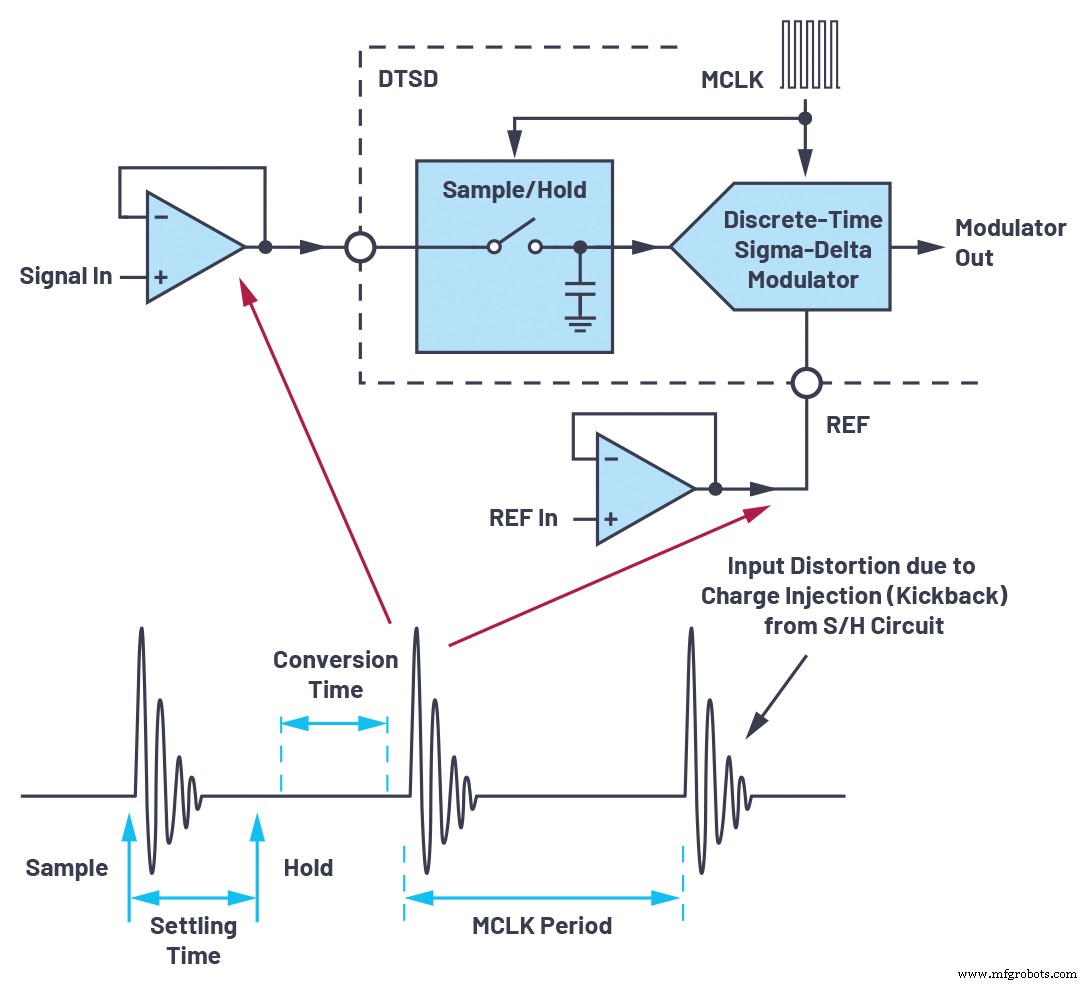

그림 10은 DTSD ADC의 반동을 보여줍니다. 예를 들어 샘플링 주파수가 24MHz인 경우 데이터 신호는 41ns 내에서 안정되어야 합니다. 레퍼런스는 스위치드 커패시터 입력이기도 하므로 레퍼런스 입력 핀에도 고대역폭 버퍼가 필요합니다. 이러한 입력 신호 및 참조 버퍼는 노이즈를 추가하고 신호 체인의 전체 성능을 떨어뜨립니다. 또한 입력 신호 드라이버(S&H 주파수 주변)의 왜곡 성분이 앤티앨리어싱 요구 사항을 추가합니다. 또한 스위치드 커패시터 입력에서 샘플링 속도의 변화는 입력 전류를 변화시킵니다. 이는 ADC 구동 중 드라이버 또는 이전 단계에서 발생하는 이득 오차를 줄이기 위해 시스템을 재조정하는 결과를 초래할 수 있습니다.

연속 시간 시그마-델타 ADC

CTSD ADC는 오버샘플링 및 노이즈 쉐이핑과 같은 원칙을 활용하지만 상당한 시스템 이점을 제공하는 샘플링 작업을 구현하는 대체 수단이 있는 대체 시그마-델타 ADC 아키텍처입니다.

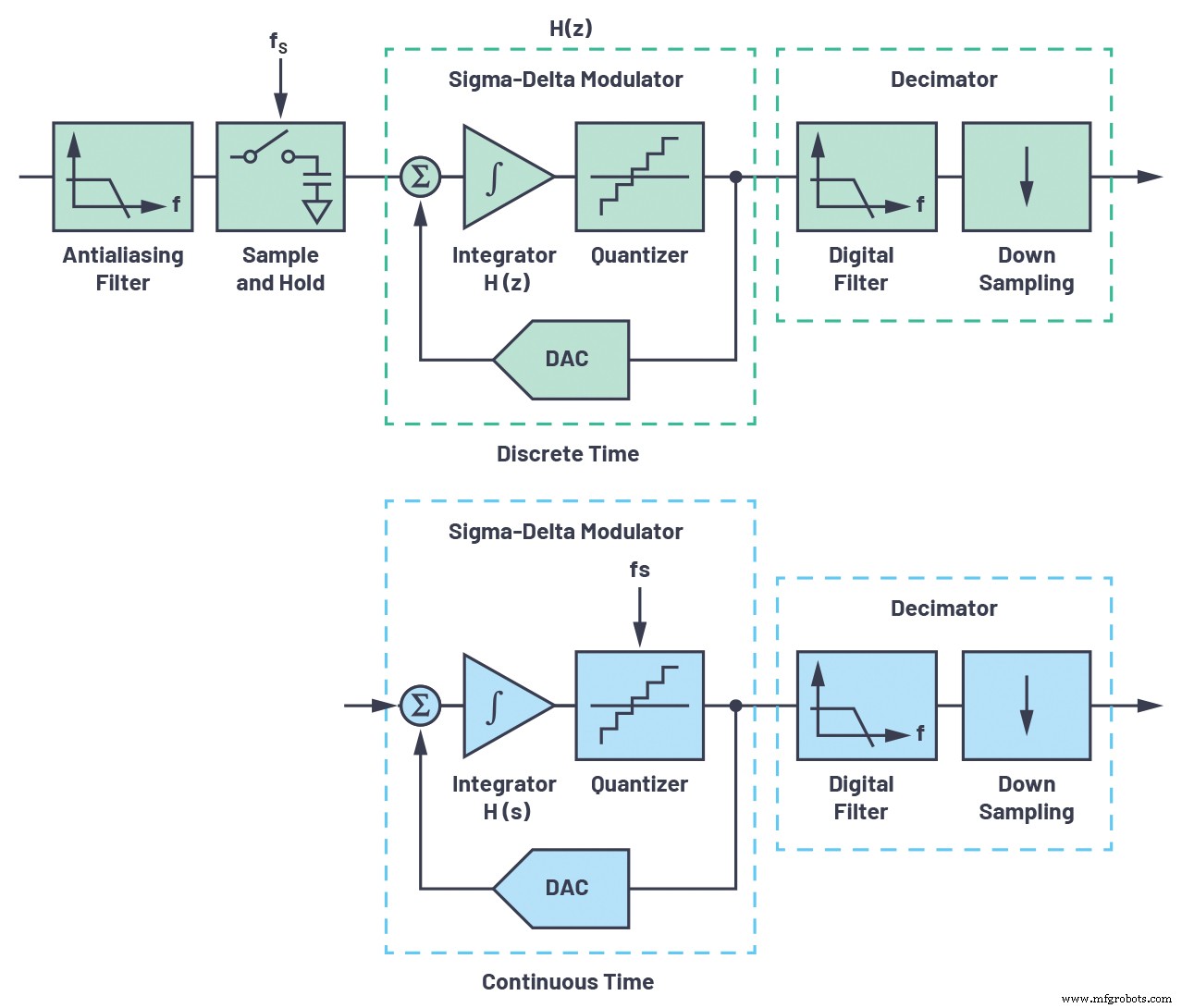

그림 11은 DTSD 아키텍처와 CTSD 아키텍처를 비교한 것입니다. DTSD 아키텍처에서 볼 수 있듯이 입력은 루프 전에 샘플링됩니다. 루프 필터 H(z)는 시간상 이산적이며 스위치드 커패시터 적분기를 사용하여 구현됩니다. 피드백 DAC도 전환된 커패시터 기반입니다. 입력에 샘플링이 있으므로 fS에서 앨리어싱 문제가 발생합니다. , 샘플링하기 전에 입력에 추가 앤티앨리어싱 필터가 필요합니다.

더 큰 이미지를 보려면 클릭하세요.

그림 11. 이산 시간 및 연속 시간 모듈식 블록 회로도. (출처:Analog Devices)

CTSD는 입력에 샘플러가 없습니다. 오히려 루프 내부의 양자화기에서 샘플링됩니다. 루프 필터는 이제 연속 시간 적분기를 사용하는 연속 시간이며 피드백 DAC도 마찬가지입니다. 형성되는 양자화와 유사하게 샘플링으로 인한 앨리어싱도 형성됩니다. 결과적으로 거의 비샘플링 ADC가 되어 고유한 클래스를 만듭니다.

변조기의 샘플링 주파수를 쉽게 조정할 수 있는 DTSD와 달리 CTSD의 샘플링 주파수는 고정되어 있습니다. 또한 CTSD ADC는 스위치드 커패시터 등가물보다 지터에 대한 내성이 약한 것으로 알려져 있습니다. 기성 크리스털 또는 CMOS 발진기는 로컬에서 ADC에 낮은 지터 클록을 제공하여 절연을 통해 낮은 지터 클록을 전송하는 것을 방지하고 EMC를 감소시킵니다.

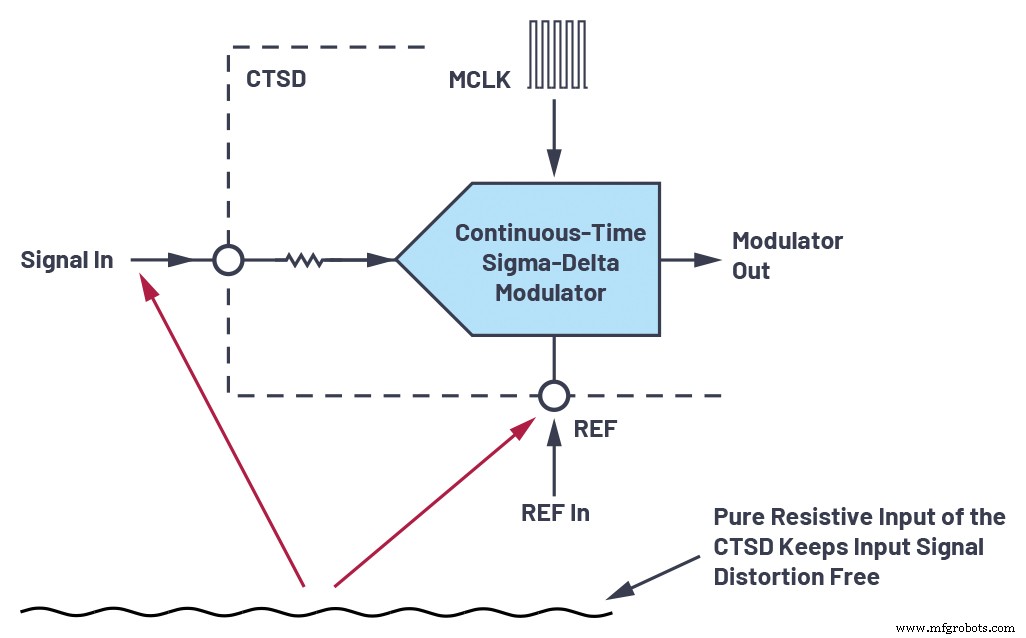

CTSD의 두 가지 주요 이점은 고유한 앨리어스 제거와 신호 및 참조에 대한 저항성 입력입니다.

내재된 앤티앨리어싱

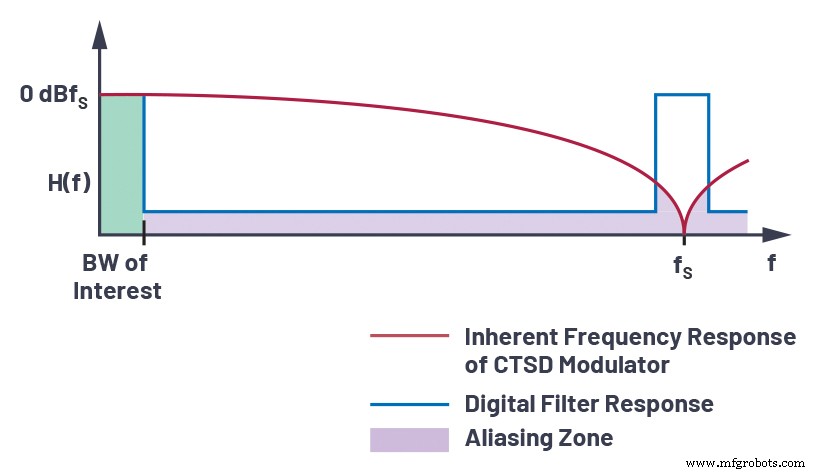

루프 내에서 양자화기를 이동하면 고유한 앨리어스 제거가 발생합니다. 그림 12에서 볼 수 있듯이 입력 신호는 샘플링되기 전에 루프 필터를 통과하고 양자화기에서 발생하는 폴드백(별칭) 오류도 이 필터를 봅니다. 신호 및 에일리어스 오류는 시그마-델타 루프와 동일한 잡음 전달 함수를 보게 되며 둘 다 시그마-델타 아키텍처의 양자화 잡음과 유사한 잡음 형성을 갖게 됩니다. 따라서 CTSD 루프의 주파수 응답은 자연스럽게 샘플링 주파수의 정수 배수 주변의 입력 신호를 거부하여 앤티앨리어싱 필터 역할을 합니다.

더 큰 이미지를 보려면 클릭하세요.

그림 12. CTSD 변조기의 주파수 응답. (출처:Analog Devices)

저항 입력

신호 및 기준 입력에 저항성 입력이 있으면 샘플 앤 홀드 구성보다 쉽게 구동할 수 있습니다. 일정한 저항 입력을 사용하면 반동이 없고 드라이버를 완전히 제거할 수 있습니다. 그림 13과 같이 입력은 왜곡이 없습니다. 그리고 입력 저항이 일정하기 때문에 이득 오류에 대한 시스템의 재조정도 제거됩니다.

더 큰 이미지를 보려면 클릭하세요.

그림 13. CTSD에 대한 입력 안정화. (출처:Analog Devices)

ADC에 단극 전원이 있더라도 아날로그 입력은 양극일 수 있습니다. 이것은 바이폴라 프런트 엔드에서 ADC로 레벨 시프팅의 필요성을 제거할 수 있습니다. ADC의 dc 성능은 입력 저항이 이제 입력 전류뿐만 아니라 입력 공통 모드 종속 전류를 갖는 것과 동일하지 않을 수 있습니다.

기준 부하는 또한 저항성이 있어 스위칭 킥백을 감소시키므로 별도의 기준 버퍼가 필요하지 않습니다. 저역 통과 필터용 저항은 온칩 저항 부하(같은 재료일 수 있으므로)와 함께 추적하여 이득 오류 온도 드리프트를 줄일 수 있도록 온칩으로 만들 수 있습니다.

CTSD 아키텍처는 새로운 것은 아니지만 산업 및 계측 시장의 메가트렌드는 더 높은 대역폭에서 dc 및 ac 정밀 성능을 요구합니다. 또한 고객은 출시 시간을 단축하기 위해 대부분의 솔루션에 맞는 단일 플랫폼 디자인을 선호합니다.

CTSD 아키텍처는 고성능 오디오에서 셀룰러 핸드셋 RF 프런트 엔드에 이르는 광범위한 애플리케이션 세트에서 선택되어 왔습니다. 그 이유는 다른 유형의 ADC에 비해 많은 이점이 있기 때문입니다. 이점에는 통합 용이성 및 낮은 전력 소비가 포함되지만 CTSD를 사용하면 여러 가지 중요한 시스템 수준 문제가 해결되기 때문에 더욱 중요할 수 있습니다. 많은 기술적 결점으로 인해 CTSD의 사용은 이전에 상대적인 오디오 주파수/대역폭 및 더 낮은 동적 범위로 제한되었습니다. 따라서 연속 근사 ADC 및 오버샘플링된 DTSD 컨버터와 같은 고성능 Nyquist 속도 컨버터는 정밀, 고성능/중간 대역폭 애플리케이션을 위한 주류 솔루션이었습니다.

그러나 최근의 기술 혁신으로 많은 한계를 극복할 수 있었습니다. 예를 들어 Analog Devices의 AD7134는 CTSD를 기반으로 하는 고정밀 dc ~ 400kHz 대역폭 ADC를 지원하여 훨씬 더 높은 성능 사양을 달성하는 동시에 dc 정확도를 제공하고 결과적으로 높은 수준의 여러 중요한 시스템 수준 문제에 대한 솔루션을 가능하게 합니다. 성능 계측 애플리케이션. AD7134는 또한 CTSD의 고정 샘플링 속도에서 파생된 가변 데이터 속도로 데이터를 제공하는 ASRC(비동기 샘플링 속도 변환기)를 통합합니다. 출력 데이터 속도는 변조기 샘플링 주파수와 무관할 수 있으며 다양한 세분화된 처리량에 대해 CTSD ADC를 성공적으로 사용할 수 있습니다. 세분화된 수준에서 출력 데이터 속도를 변경할 수 있는 유연성 덕분에 사용자는 일관된 샘플링을 사용할 수도 있습니다.

고유한 앨리어스 제거 기능은 앤티앨리어싱 필터가 필요하지 않으므로 구성 요소와 솔루션 크기가 줄어듭니다. 더 중요한 것은 드룹(droop)과 같은 안티앨리어싱 필터와 함께 발생하는 성능 문제, 오프셋(offset), 게인(gain), 위상 오류(phase error)와 같은 오류, 시스템의 노이즈가 더 이상 존재하지 않는다는 것입니다. 앤티앨리어싱 필터는 또한 필요한 제거에 따라 신호 체인의 전체 대기 시간을 크게 추가합니다. 필터를 제거하면 이 지연이 완전히 제거되어 잡음이 많은 디지털 제어 루프 애플리케이션에서 정밀 변환이 가능합니다.

시스템 수준에서 앤티앨리어싱 필터가 없으면 다중 채널 시스템의 위상 정합이 크게 향상될 수 있습니다. 이것은 진동 모니터링, 전력 측정, 데이터 수집 모듈 및 소나와 같이 낮은 채널 간 불일치를 요구하는 애플리케이션에서 특히 유용합니다. 고유한 필터링 동작으로 인해 CTSD ADC는 IC 자체 내에서뿐만 아니라 시스템 수준에서 모든 종류의 간섭에 영향을 받지 않습니다. DTSD ADC 및 SAR ADC에서는 ADC가 샘플링될 때 간섭이 덜 발생하도록 주의해야 합니다. 또한 고유의 필터링 작용으로 인해 전원 공급 라인의 간섭에 대한 내성이 있습니다. 일정한 저항성 아날로그 입력과 기준 입력을 사용하면 드라이버 요구 사항도 완전히 제거할 수 있습니다. 다시 말하지만, 이는 오프셋, 이득, 위상 오류 및 시스템에 대한 노이즈와 같은 오류와 같은 성능 문제를 해결합니다.

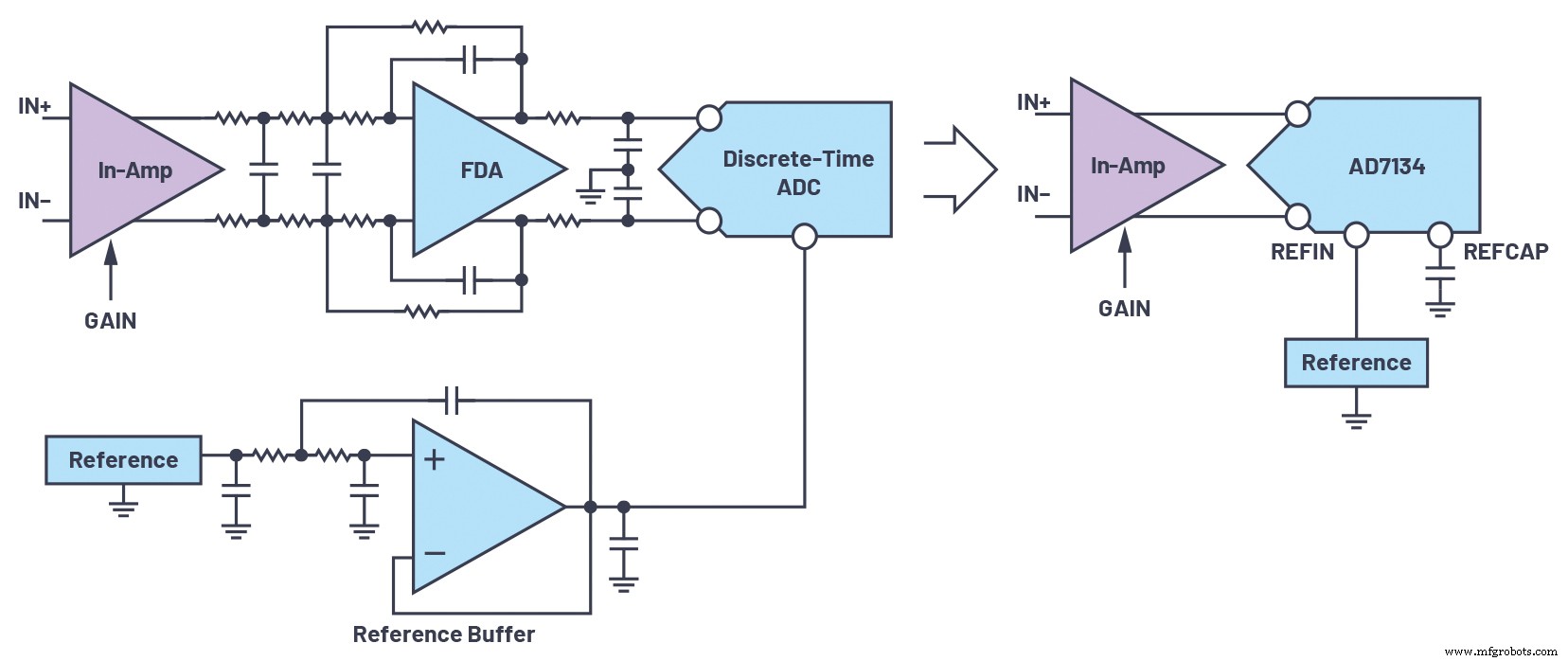

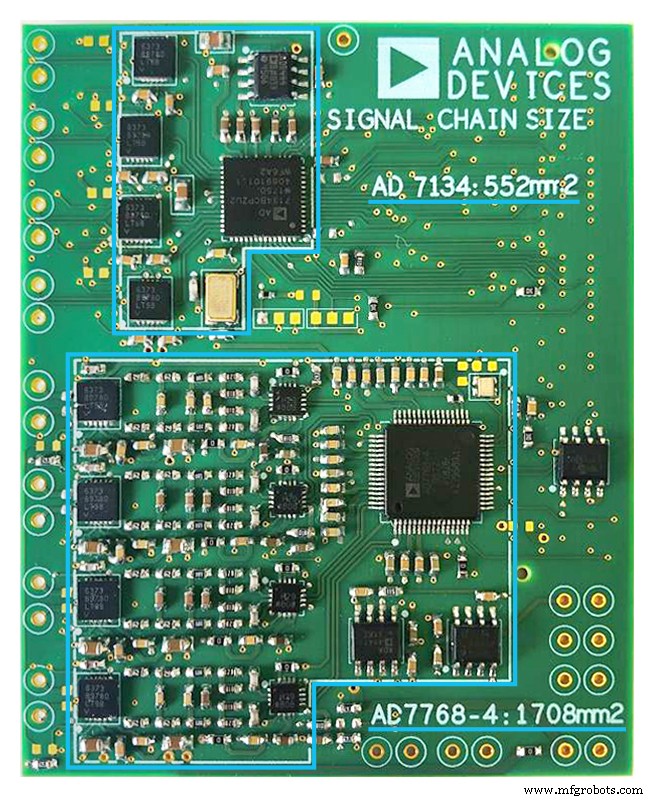

정밀 성능을 달성하기 위한 노력은 설계된 요소의 수가 크게 줄어들기 때문에 매우 최소화됩니다. 그 결과 더 빠른 설계 시간, 더 빠른 고객 출시 시간, 더 쉬운 BOM 관리 및 안정성이 제공됩니다. 앤티앨리어싱 필터, 드라이버 및 참조 버퍼를 제거하면 시스템 보드 영역이 크게 줄어듭니다. 계측 증폭기를 사용하여 ADC를 직접 구동할 수 있습니다. 예를 들어, AD7134는 차동 입력 전용 ADC이므로 LTC6373과 같은 차동 입력 증폭기를 드라이버로 사용할 수 있습니다. 그림 14의 비교는 이산 시간 기반 신호 체인과 연속 시간 기반 신호 체인에 대한 신호 체인을 보여줍니다. 우리의 실험은 동등한 이산 시간 기반 신호 체인과 비교할 때 70%의 면적 절약을 보여주므로 고밀도 다중 채널 애플리케이션에 탁월한 선택입니다.

결론적으로, 이 접근 방식은 시스템 크기를 크게 줄이고 신호 체인 설계를 단순화하며 시스템을 더욱 견고하게 만들고 정밀 계측 애플리케이션에서 요구하는 성능 매개변수를 교환하지 않고도 손쉬운 설계를 통해 전체 시장 출시 시간을 단축합니다.

더 큰 이미지를 보려면 클릭하세요.

그림 14. 이산 시간 기반(왼쪽) 및 연속 시간 기반(오른쪽) 신호 체인 비교. (출처:Analog Devices)

더 큰 이미지를 보려면 클릭하세요.

그림 15. 이산 시간 및 연속 시간 신호 체인의 크기 비교. (출처:Analog Devices)

참조

케스터, 월트. "MT-002:Nyquist Criterion이 샘플링 데이터 시스템 설계에 의미하는 것." Analog Devices, Inc., 2009.

파반, 샨티. "스위치드 커패시터 피드백 DAC가 있는 연속 시간 Δ∑ 변조기의 별칭 제거." 회로 및 시스템에 대한 IEEE 거래 I:일반 논문 , 권. 58, 2번, 2011년 2월.

Schreier, Richard 및 Gabor C. Temes. 델타-시그마 데이터 변환기 이해. John Wiley and Sons, 2005.

감사

저자는 이 기사에 대한 지원에 대해 Abhilasha Kawle, Avinash Gutta 및 Roberto Maurino에게 감사드립니다.

임베디드

Mitsubishi Electric은 EMEA 시장을 위한 감독 제어 및 데이터 수집(SCADA) 라인업을 확장하여 현재 GENESIS64 시리즈 이름으로 시스템 모니터링 및 프로세스 제어를 위한 두 가지 추가 유형의 소프트웨어를 제공하여 기존 MAPS SCADA 소프트웨어를 보완합니다. . 새로운 라인업은 소규모 생산 라인 모니터링 및 제어에서 플랜트 전체 시스템, 프로세스 자동화, 유틸리티 및 빌딩 자동화를 위한 다중 사이트 모니터링 및 비즈니스 인텔리전스(BI)에 이르기까지 다양한 목적을 포괄하는 다양한 IoT 요구를 충족

이 문서에서는 다양한 체인 드라이브 유형에 대해 알아봅니다. , 작동 , 장점 , 단점 , 애플리케이션 , 그리고 다운로드할 수 있습니다. PDF 파일 이 게시물의 끝부분에 있습니다. 체인 드라이브 및 유형: 체인 드라이브 작은 중심 거리에 적합하며 일반적으로 최대 3m까지 사용할 수 있지만 특수한 경우에는 최대 8m까지 사용할 수 있습니다. 체인 드라이브 전송 전력 최대 100kw 및 작동 주변 속도 최대 15m/s. 속도 비율은 8:1만큼 높을 수 있습니다. 벨트 드라이브와 로프 드라이브의 주요 단점은 속도 비율이 일정