verilog

Verilog 언어에 대한 자세한 내용을 살펴보기 전에 칩 설계의 다양한 추상화 계층을 이해하는 것이 좋습니다.

최상위 계층은 다양한 하위 블록을 정의하고 기능을 기반으로 그룹화하는 시스템 수준 아키텍처입니다. 예를 들어 프로세서 클러스터에는 여러 코어, 캐시 블록 및 캐시 일관성 논리가 있습니다. 이 모든 것이 캡슐화되어 입출력 신호가 있는 단일 블록으로 표시됩니다.

<노스크립트>

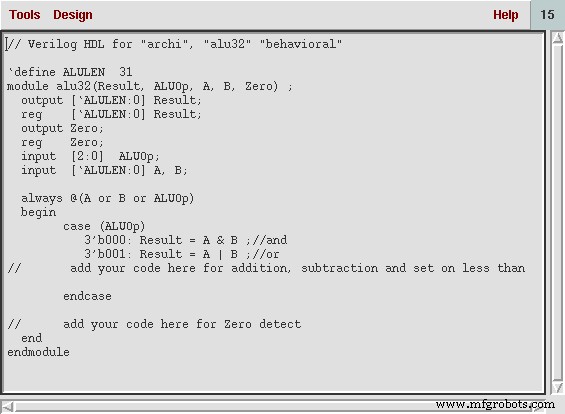

다음 레벨에서 각 하위 블록은 각 개별 블록의 기능을 정확하게 설명하기 위해 하드웨어 설명 언어로 작성됩니다. 회로도, 기술 라이브러리와 같은 하위 수준 구현 세부 정보는 이 단계에서 무시됩니다. 예를 들어, 컨트롤러 블록은 각각 기능의 더 작은 구성 요소를 설명하는 여러 Verilog 파일을 갖게 됩니다.

<노스크립트>

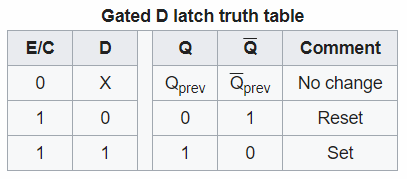

그런 다음 HDL은 플립플롭과 같은 디지털 요소를 특성화하는 기술 라이브러리를 포함하는 게이트 레벨 회로도로 변환됩니다. 예를 들어, D 래치를 위한 디지털 회로는 D 및 E 입력의 모든 조합이 진리표에 의해 주어진 출력 Q를 생성하도록 특정 방식으로 배열된 NAND 게이트를 포함합니다.

<노스크립트>진리표는 기본적으로 모든 입력 신호 레벨의 순열과 결과 출력 레벨을 제공하며 아래에 주어진 것은 활성화 핀이 있는 D 래치에 대한 것입니다. 하드웨어 회로도는 부울 논리와 K-맵을 사용하여 진리표에서 파생될 수도 있습니다. 그러나 프로세서 및 컨트롤러와 같은 더 복잡한 디지털 블록에 대해 이 방법을 따르는 것은 실용적이지 않습니다.

<노스크립트>

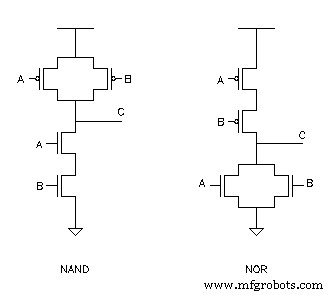

NAND 게이트의 구현은 특정 형식의 CMOS 트랜지스터를 연결하여 수행됩니다. 이 수준에서 트랜지스터 채널 폭, Vdd 및 출력 용량성 부하를 구동하는 능력이 설계 과정에서 고려됩니다.

<노스크립트>

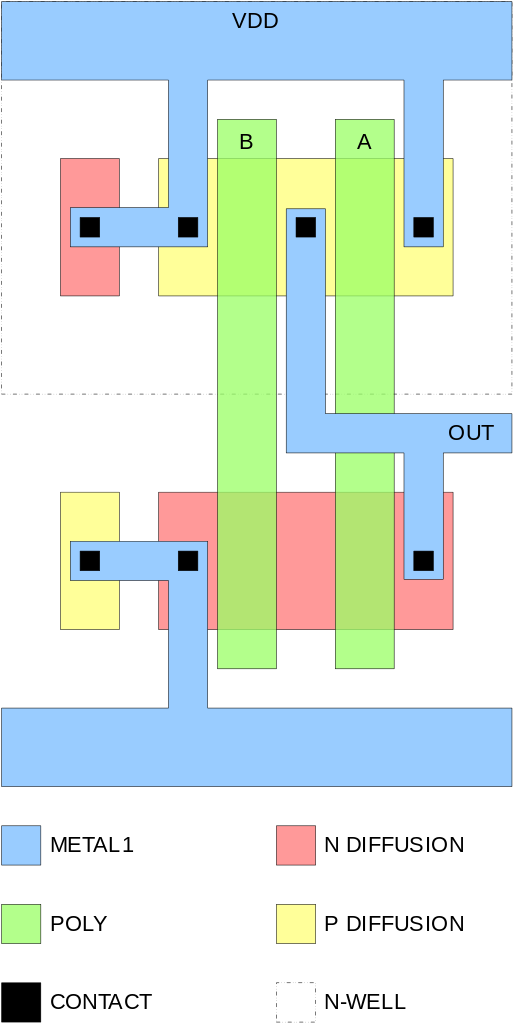

마지막 단계는 EDA 도구를 사용하여 이러한 트랜지스터를 실리콘으로 배치하여 제작할 수 있도록 하는 것입니다. 이 수준에서는 다른 레이아웃이 다른 의미 중에서 저항 및 커패시턴스와 같은 다른 물리적 속성을 갖기 때문에 일부 장치 및 기술 지식이 필요합니다.

<노스크립트>

다음으로, 디지털 블록의 설계에는 주로 하향식 및 상향식 방법론의 두 가지 스타일이 있습니다.

하향식이 스타일에서는 최상위 블록을 구축하는 데 필요한 하위 모듈의 식별과 함께 최상위 블록이 먼저 정의됩니다. 마찬가지로, 각 하위 블록은 더 작은 구성 요소로 더 분할되고, 프로세스는 리프 셀 또는 더 이상 분할할 수 없는 단계에 도달할 때까지 계속됩니다.

상향식이 경우 첫 번째 작업은 사용 가능한 빌딩 블록을 식별하는 것입니다. 그런 다음 그것들을 결합하고 특정한 방식으로 연결하여 더 큰 세포를 만들고 최상위 블록을 조립하는 데 사용합니다.

일반적으로 두 흐름의 조합이 사용됩니다. 설계자는 설계의 시스템 수준 보기를 정의하고 설계자는 각 기능 블록의 논리를 구현하고 게이트로 합성됩니다. 여기까지 하향식 스타일을 따릅니다. 그러나 이러한 게이트는 최상의 영역, 성능 및 전력에서 가장 작은 블록의 물리적 레이아웃부터 시작하는 상향식 흐름에 따라 구축되었습니다. 이러한 표준 셀에는 하드웨어 회로도도 있으며 상승 및 하강 시간, 전력 및 기타 지연과 같은 다양한 정보를 얻는 데 사용할 수 있습니다. 이러한 셀은 필요한 경우 선택하고 인스턴스화하는 합성 도구에서 사용할 수 있습니다.

verilog

수평계는 목수, 건축업자, 심지어 집에 있는 사람들이 그림을 걸기 위해 사용하는 매우 오래된 도구로 직선 또는 수직선을 결정하는 데 도움이 됩니다. 수평 방식으로 하나를 정렬할 때 목표는 레벨 중앙에 있는 소량의 액체에 있는 거품이 두 라인 사이의 중앙에 있도록 하는 것이기 때문에 이를 버블 레벨이라고도 합니다. 이렇게 하면 선이 직선인지 여부를 상당히 정확하게 알 수 있습니다. 수평계 수직선을 측정하기 위한 수준기 유형도 있으며, 이는 다소 다른 표준에 따라 작동할 수 있습니다. 위에서 언급했듯이 정신 수준은 확실히 고대입니다.

전체론적 설계는 설계되는 시스템을 더 큰 것의 일부인 상호 연결된 전체로 간주하는 설계 접근 방식입니다. 전체론적 개념은 건축뿐만 아니라 기계 장치의 설계, 공간 배치 등에 적용될 수 있습니다. 이러한 디자인 접근 방식은 종종 환경에 대한 우려를 포함하며, 전체적인 디자이너는 디자인이 환경에 미치는 영향을 고려하고 디자인에서 환경 영향을 줄이려고 시도합니다. 미학은 또한 전체적인 디자인에서 중요한 고려 사항이 될 수 있습니다. 디자이너는 사람들이 디자인을 보는 다양한 방식에 대해 생각하면서 디자인이 전체적으로 어떻게 보일지 고려할