verilog

Verilog의 어휘 규칙은 토큰 스트림을 포함한다는 점에서 C와 유사합니다. 어휘 토큰은 하나 이상의 문자로 구성될 수 있으며 토큰은 주석, 키워드, 숫자, 문자열 또는 공백일 수 있습니다. 모든 줄은 세미콜론 ;로 끝나야 합니다. .

Verilog는 대소문자를 구분합니다. , 따라서 var_a와 var_A는 다릅니다.

Verilog에서 주석을 작성하는 방법에는 두 가지가 있습니다.

//로 시작합니다. 그리고 Verilog 컴파일러에게 이 지점 이후의 모든 항목을 줄 끝까지 주석으로 처리하도록 지시합니다./*로 시작합니다. */로 끝남 중첩될 수 없습니다.그러나 한 줄 주석은 여러 줄 주석에 중첩될 수 있습니다.

// This is a single line comment

integer a; // Creates an int variable called a, and treats everything to the right of // as a comment

/*

This is a

multiple-line or

block comment

*/

/* This is /*

an invalid nested

block comment */

*/

/* However,

// this one is okay

*/

// This is also okay

///////////// Still okay

공백은 공백, 탭, 줄 바꿈 및 폼피드의 문자를 나타내는 데 사용되는 용어이며 일반적으로 토큰을 구분하는 경우를 제외하고 Verilog에서 무시됩니다. 사실, 이것은 코드의 들여쓰기를 도와 읽기 쉽게 만듭니다.

module dut; // 'module' is a keyword,

// 'dut' is an identifier

reg [8*6:1] name = "Hello!"; // The 2 spaces in the beginning are ignored

그러나 공백(공백)과 탭(TAB 키에서)은 문자열에서 무시되지 않습니다. 아래 예에서 문자열 addr이라는 변수는 문자열의 공백을 보존하기 때문에 "Earth" 값을 얻습니다.

// There is no space in the beginning of this line, // but there's a space in the string reg [8*6:1] addr = "Earth "; endmodule

세 가지 유형의 연산자가 있습니다. 단항 , 바이너리 , 및 삼항 또는 조건부 .

x = ~y; // ~ is a unary operator, and y is the operand

x = y | z; // | is a binary operator, where y and z are its operands

x = (y > 5) ? w : z; // ?: is a ternary operator, and the expression (y>5), w and z are its operands

표현식(y> 5)이 참이면 변수 x w의 값을 얻습니다. , 그렇지 않으면 z의 값 .

우리는 소수로 표현되는 숫자에 가장 익숙합니다. 그러나 숫자는 바이너리로도 표현될 수 있습니다. , 8진수 및 16진수 . 기본적으로 Verilog 시뮬레이터는 숫자를 소수로 취급합니다. 다른 기수로 나타내기 위해 , 특정 규칙을 따라야 합니다.

16 // Number 16 in decimal 0x10 // Number 16 in hexadecimal 10000 // Number 16 in binary 20 // Number 16 in octal

크기가 지정된 숫자는 아래와 같이 표시됩니다. 여기서 크기 숫자의 비트 수를 지정하기 위해 10진수로만 작성됩니다.

[size]'[base_format][number]

3'b010; // size is 3, base format is binary ('b), and the number is 010 (indicates value 2 in binary)

3'd2; // size is 3, base format is decimal ('d) and the number is 2 (specified in decimals)

8'h70; // size is 8, base format is hexadecimal ('h) and the number is 0x70 (in hex) to represent decimal 112

9'h1FA; // size is 9, base format is hexadecimal ('h) and the number is 0x1FA (in hex) to represent decimal 506

4'hA = 4'd10 = 4'b1010 = 4'o12 // Decimal 10 can be represented in any of the four formats

8'd234 = 8'D234 // Legal to use either lower case or upper case for base format

32'hFACE_47B2; // Underscore (_) can be used to separate 16 bit numbers for readability

기본 형식이 16진수인 경우 대문자는 숫자 지정에 적합합니다.

16'hcafe; // lowercase letters Valid 16'hCAFE; // uppercase letters Valid 32'h1D40_CAFE; // underscore can be used as separator between 4 letters Valid

base_format이 없는 숫자 사양은 기본값의 십진수입니다. . 크기가 없는 숫자 사양에는 시뮬레이터 및 머신 유형에 따라 기본 비트 수가 있습니다.

integer a = 5423; // base format is not specified, a gets a decimal value of 5423

integer a = 'h1AD7; // size is not specified, because a is int (32 bits) value stored in a = 32'h0000_1AD7

음수는 빼기 -를 넣어 지정합니다. 숫자의 크기 앞에 부호를 붙입니다. base_format 사이에 빼기 기호를 사용하는 것은 불법입니다. 및 번호 .

-6'd3; // 8-bit negative number stored as two's complement of 3 -6'sd9; // For signed maths 8'd-4; // Illegal

큰따옴표 " "로 묶인 일련의 문자 문자열이라고 합니다. 여러 줄로 나눌 수 없으며 문자열의 모든 문자를 저장하는 데 1바이트가 필요합니다.

"Hello World!" // String with 12 characters -> require 12 bytes "x + z" // String with 5 characters "How are you feeling today ?" // Illegal for a string to be split into multiple lines

식별자 나중에 참조할 수 있도록 변수의 이름입니다. 영숫자 [a-z][A-Z][0-9]로 구성됩니다. , 밑줄 _ 또는 달러 기호 $ 대소문자를 구분합니다. 숫자나 달러 기호로 시작할 수 없습니다.

integer var_a; // Identifier contains alphabets and underscore -> Valid integer $var_a; // Identifier starts with $ -> Invalid integer v$ar_a; // Identifier contains alphabets and $ -> Valid integer 2var; // Identifier starts with a digit -> Invalid integer var23_g; // Identifier contains alphanumeric characters and underscore -> Valid integer 23; // Identifier contains only numbers -> Invalid

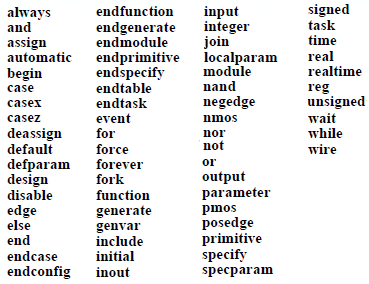

키워드는 언어 구성을 정의하기 위해 예약된 특수 식별자이며 소문자입니다. 중요한 키워드 목록은 아래와 같습니다.

<노스크립트>

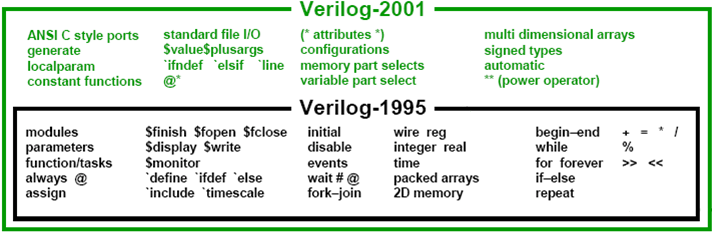

Verilog는 수년에 걸쳐 몇 번의 수정을 거쳤으며 1995년부터 2001년까지 더 많은 내용이 추가되었으며 아래에 나와 있습니다.

<노스크립트>

verilog

Verilog는 하드웨어 설명 언어이며 설계자가 RTL 설계를 시뮬레이션하여 논리 게이트로 변환할 필요가 없습니다. 시뮬레이션이 필요한 이유는 무엇입니까? 시뮬레이션은 RTL 코드가 의도한 대로 동작하는지 확인하기 위해 다른 시간에 다른 입력 자극을 설계에 적용하는 기술입니다. 기본적으로 시뮬레이션은 설계의 견고성을 검증하기 위해 잘 따라야 하는 기술입니다. 또한 가공된 칩이 실제 세계에서 사용되는 방식과 다양한 입력에 반응하는 방식과 유사합니다. 예를 들어, 위의 디자인은 출력 pe 보여진 바와 같이. 시뮬레이션을 통해

디자인 module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else if