verilog

Verilog 언어에서 데이터 유형의 주요 목적은 플립플롭의 비트와 같은 데이터 저장 요소와 논리 게이트와 순차 구조 사이를 연결하는 와이어와 같은 전송 요소를 나타내는 것입니다.

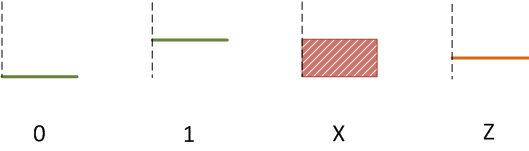

거의 모든 데이터 유형은 real을 제외하고 아래와 같이 4가지 다른 값 중 하나만 가질 수 있습니다. 및 event 데이터 유형.

| 0 | 논리 0 또는 거짓 조건을 나타냅니다. |

| 1 | 논리 1 또는 참 조건을 나타냅니다. |

| x | 알 수 없는 논리 값을 나타냅니다(0 또는 1일 수 있음) |

| z | 고임피던스 상태를 나타냄 |

다음 이미지는 이러한 값이 타이밍 다이어그램과 시뮬레이션 파형에 어떻게 표시되는지 보여줍니다. 대부분의 시뮬레이터는 red X을 나타냅니다. 및 주황색 중간은 하이 임피던스 또는 Z를 나타냅니다. .

Verilog는 기본적으로 플립플롭과 같은 하드웨어 요소와 NAND 및 NOR와 같은 조합 논리를 설명하는 데 사용되기 때문에 하드웨어에서 발견되는 가치 시스템을 모델링해야 합니다. 논리 1은 전압 공급 Vdd를 나타냅니다. 이는 제조 기술 노드에 따라 0.8V에서 3V 이상 사이의 범위일 수 있습니다. 논리 0은 접지를 나타냅니다. 따라서 0V의 값입니다.

X 또는 x 이는 값이 그 당시에 단순히 알려지지 않았음을 의미하며 0 또는 1일 수 있습니다. 이는 X 방식과 상당히 다릅니다. 부울 논리로 처리되며 여기서 "관심 없음"을 의미합니다.

불완전한 전기 회로와 마찬가지로 아무 것도 연결되지 않은 와이어는 해당 노드에서 높은 임피던스를 가지며 Z로 표시됩니다. 또는 z . Verilog에서도 연결되지 않은 와이어는 높은 임피던스를 발생시킵니다.

네트 및 변수 서로 다른 하드웨어 구조를 나타내고 값을 할당하고 유지하는 방식이 다른 두 가지 주요 데이터 유형 그룹입니다.

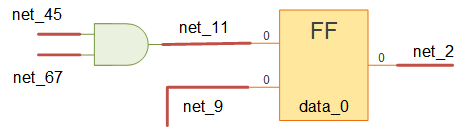

네트 논리 게이트와 같은 하드웨어 엔티티 사이를 연결하는 데 사용되므로 자체적으로 값을 저장하지 않습니다. 아래 그림에서 net_11이라는 네트는 AND 게이트의 출력과 data_0이라는 플립플롭의 첫 번째 입력을 연결하는 데 사용됩니다. 비슷한 방식으로 AND 게이트의 두 입력은 net_45와 net_67에 연결됩니다.

<노스크립트>

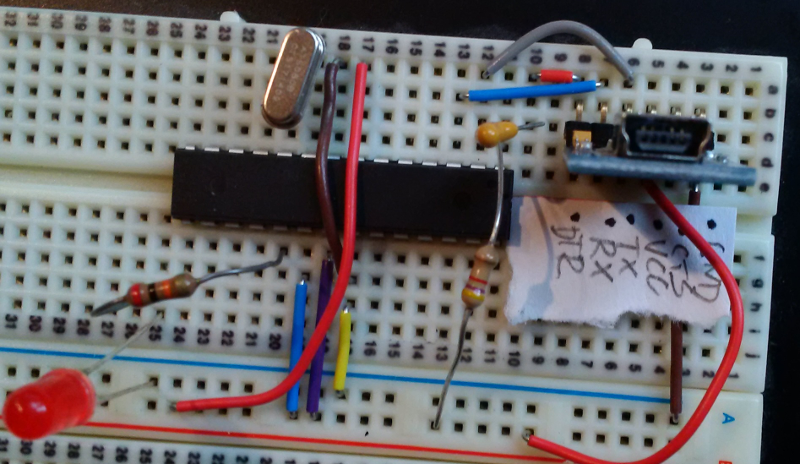

특성이 다른 다양한 유형의 네트가 있지만 가장 인기 있고 널리 사용되는 네트 디지털 디자인에서 유형은 wire입니다. . wire 요소를 연결하고 단일 게이트 또는 연속 할당에 의해 구동되는 네트를 연결하는 데 사용되는 Verilog 데이터 유형입니다. wire 브레드보드의 두 구성 요소를 연결하는 데 사용되는 전선과 유사합니다.

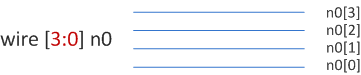

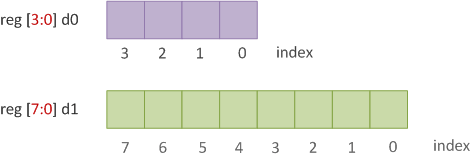

다중 네트에 대한 요구 사항이 있는 경우 함께 묶어 단일 wire을 형성할 수 있습니다. . 아래 표시된 이미지에는 각 와이어에 4개의 개별 값을 보낼 수 있는 4비트 와이어가 있습니다. 너비가 1보다 큰 개체는 다음 기사에서 볼 수 있는 벡터라고 합니다.

wire [3:0] n0; // 4-bit wire -> this is a vector

<노스크립트>

아래 코드와 같이 네트, 매개변수 또는 변수에 의해 이미 선언된 이름을 다시 선언하는 것은 불법입니다.

module design;

wire abc;

wire a;

wire b;

wire c;

wire abc; // Error: Identifier "abc" previously declared

assign abc = a & b | c;

endmodule

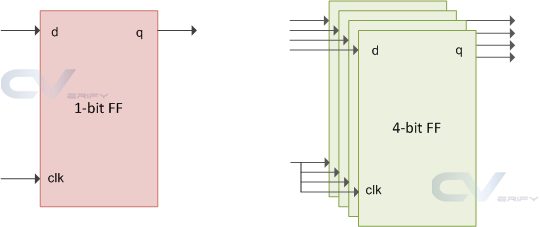

반면에 변수는 데이터 저장 요소의 추상화이며 값을 보유할 수 있습니다. 플립플롭은 저장 요소의 좋은 예입니다.

Verilog 데이터 유형 reg 할당 간에 값을 보유할 수 있으므로 하드웨어 레지스터를 모델링하는 데 사용할 수 있습니다. reg 조합 논리를 나타내는 데에도 사용할 수 있기 때문에 항상 플립플롭을 나타낼 필요는 없습니다.

왼쪽에 표시된 이미지에는 1비트를 저장할 수 있는 플립플롭이 있고 오른쪽에 4비트를 저장할 수 있는 플립플롭이 있습니다.

<노스크립트>

integer 32비트 너비의 범용 변수로 하드웨어 모델링 및 정수 값 저장 시 다른 용도로 사용할 수 있습니다.

integer count; // Count is an integer value > 0

time 변수는 부호 없는 64비트 너비이며 디버깅 목적으로 시뮬레이션 시간 수량을 저장하는 데 사용할 수 있습니다. realtime 변수는 단순히 시간을 부동 소수점 수량으로 저장합니다.

time end_time; // end_time can be stored a time value like 50ns

realtime rtime; // rtime = 40.25ps

real 변수는 부동 소수점 값을 저장할 수 있으며 integer과 같은 방식으로 할당할 수 있습니다. 및 reg .

real float; // float = 12.344 - can store floating numbers

module testbench;

integer int_a; // Integer variable

real real_b; // Real variable

time time_c; // Time variable

initial begin

int_a = 32'hcafe_1234; // Assign an integer value

real_b = 0.1234567; // Assign a floating point value

#20; // Advance simulation time by 20 units

time_c = $time; // Assign current simulation time

// Now print all variables using $display system task

$display ("int_a = 0x%0h", int_a);

$display ("real_b = %0.5f", real_b);

$display ("time_c = %0t", time_c);

end

endmodule

시뮬레이션 로그 ncsim> run int_a = 0xcafe1234 real_b = 0.12346 time_c = 20 ncsim: *W,RNQUIE: Simulation is complete.

문자열은 reg에 저장됩니다. , 및 reg의 너비 변수는 문자열을 담을 만큼 충분히 커야 합니다. 문자열의 각 문자는 ASCII 값을 나타내며 1바이트가 필요합니다. 변수의 크기가 문자열보다 작으면 Verilog는 문자열의 가장 왼쪽 비트를 자릅니다. 변수의 크기가 문자열보다 크면 Verilog는 문자열 왼쪽에 0을 추가합니다.

// "Hello World" requires 11 bytes

reg [8*11:1] str = "Hello World"; // Variable can store 11 bytes, str = "Hello World"

reg [8*5:1] str = "Hello World"; // Variable stores only 5 bytes (rest is truncated), str = "World"

reg [8*20:1] str = "Hello World"; // Variable can store 20 bytes (rest is padded with zeros), str = " Hello World"

다음은 위에 제공된 세 가지 변수를 시뮬레이션할 수 있는 방법을 보여주는 전체 예입니다.

module testbench;

reg [8*11:1] str1;

reg [8*5:1] str2;

reg [8*20:1] str3;

initial begin

str1 = "Hello World";

str2 = "Hello World";

str3 = "Hello World";

$display ("str1 = %s", str1);

$display ("str2 = %s", str2);

$display ("str3 = %s", str3);

end

endmodule

str1은 "Hello World" 문자열의 11바이트를 모두 저장할 수 있는 올바른 크기이므로 전체 문자열이 인쇄됩니다. 그러나 str2는 5바이트만 저장할 수 있으므로 상위 6바이트는 잘리고 "World"만 저장하게 됩니다. 세 번째 변수 str3은 11바이트보다 크고 왼쪽에 빈 공간을 채우므로 저장된 값은 " Hello World"가 됩니다.

시뮬레이션 로그ncsim> run str1 = Hello World str2 = World str3 = Hello World ncsim: *W,RNQUIE: Simulation is complete.

verilog

디지털 논리 게이트 먼저 논리 게이트에 대해 알아야 합니다. “논리 게이트는 논리 결정을 내리는 전자 회로 또는 장치입니다. 다시 말해, 논리 게이트는 하나 이상의 입력과 하나의 출력(입력 상태에 따라 다름) 또는 높거나 낮은 출력을 갖는 전자 회로입니다. 논리 게이트는 디지털 컴퓨터 및 다양한 유형의 디지털 시스템 및 회로에 널리 사용됩니다. 논리 게이트는 다양한 디지털 시스템의 빌딩 블록이므로 많은 디지털 시스템을 만드는 데 사용할 수 있습니다. 1854년 George Boole은 계산을 위해 부울 대수학을 도입했습니다. 디지

데이터 과학이란 무엇입니까? 데이터 과학은 구조적 및 비구조적 형태의 데이터를 수집, 준비 및 분석하기 위해 과학적 방법, 프로세스 및 시스템을 사용하는 학제 간 분야입니다. 데이터 과학은 수학, 통계, 데이터베이스, 정보 과학 및 컴퓨터 과학을 포함한 다양한 분야를 활용합니다. 데이터는 다양한 유형과 다양한 크기일 수 있습니다. 데이터 과학이 별도의 분야로 필요함: 데이터 과학을 별도의 분야 수준으로 업그레이드하는 주된 이유는 우리 주변의 데이터가 기하급수적으로 증가하기 때문입니다. 2020년까지 초당 약 1.7MB의 데이터