verilog

배열 net 또는 변수의 선언은 스칼라 또는 벡터가 될 수 있습니다. 식별자 이름 뒤에 주소 범위를 지정하여 여러 차원을 만들 수 있으며 이를 다차원 배열이라고 합니다. reg에 대해 Verilog에서 배열이 허용됩니다. , wire , integer 및 real 데이터 유형.

reg y1 [11:0]; // y is an scalar reg array of depth=12, each 1-bit wide

wire [0:7] y2 [3:0] // y is an 8-bit vector net with a depth of 4

reg [7:0] y3 [0:1][0:3]; // y is a 2D array rows=2,cols=4 each 8-bit wide

배열의 특정 요소에 액세스하려면 모든 차원에 대한 인덱스를 지정해야 하며 다른 변수의 표현식이 될 수 있습니다. Verilog에서 지원되는 다양한 데이터 유형에 대해 어레이를 구성할 수 있습니다.

n 1비트 reg의 메모리는 n비트 벡터 reg와 동일하지 않습니다.

y1 = 0; // Illegal - All elements can't be assigned in a single go

y2[0] = 8'ha2; // Assign 0xa2 to index=0

y2[2] = 8'h1c; // Assign 0x1c to index=2

y3[1][2] = 8'hdd; // Assign 0xdd to rows=1 cols=2

y3[0][0] = 8'haa; // Assign 0xaa to rows=0 cols=0

아래에 표시된 코드는 서로 다른 배열을 어떻게 모델링, 할당 및 액세스할 수 있는지 보여줍니다. mem1은 8비트 벡터이고, mem2는 깊이가 4인 8비트 배열(범위 [0:3]으로 지정)이며, mem3은 4행과 2열이 있는 16비트 벡터 2D 배열입니다. 이러한 변수에는 다른 값이 할당되어 인쇄됩니다.

module des ();

reg [7:0] mem1; // reg vector 8-bit wide

reg [7:0] mem2 [0:3]; // 8-bit wide vector array with depth=4

reg [15:0] mem3 [0:3][0:1]; // 16-bit wide vector 2D array with rows=4,cols=2

initial begin

int i;

mem1 = 8'ha9;

$display ("mem1 = 0x%0h", mem1);

mem2[0] = 8'haa;

mem2[1] = 8'hbb;

mem2[2] = 8'hcc;

mem2[3] = 8'hdd;

for(i = 0; i < 4; i = i+1) begin

$display("mem2[%0d] = 0x%0h", i, mem2[i]);

end

for(int i = 0; i < 4; i += 1) begin

for(int j = 0; j < 2; j += 1) begin

mem3[i][j] = i + j;

$display("mem3[%0d][%0d] = 0x%0h", i, j, mem3[i][j]);

end

end

end

endmodule

시뮬레이션 로그 ncsim> run mem1 = 0xa9 mem2[0] = 0xaa mem2[1] = 0xbb mem2[2] = 0xcc mem2[3] = 0xdd mem3[0][0] = 0x0 mem3[0][1] = 0x1 mem3[1][0] = 0x1 mem3[1][1] = 0x2 mem3[2][0] = 0x2 mem3[2][1] = 0x3 mem3[3][0] = 0x3 mem3[3][1] = 0x4 ncsim: *W,RNQUIE: Simulation is complete.

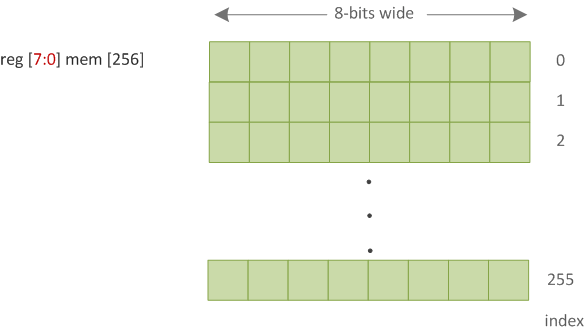

메모리는 디지털 회로에 데이터와 정보를 저장하는 데 도움이 되는 디지털 저장 요소입니다. RAM 및 ROM은 이러한 메모리 요소의 좋은 예입니다. 스토리지 요소는 reg 유형의 1차원 배열을 사용하여 모델링할 수 있습니다. 메모리라고 합니다. . 메모리의 각 요소는 단어를 나타낼 수 있으며 단일 배열 인덱스를 사용하여 참조됩니다.

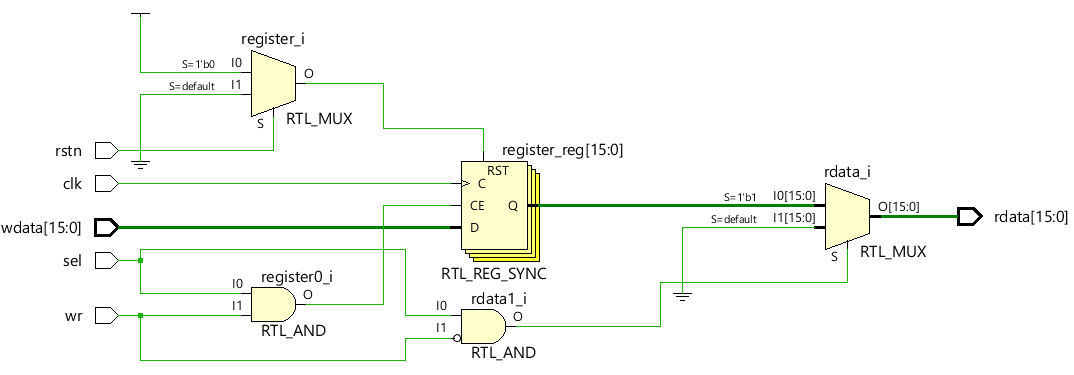

Verilog 벡터는 변수 이름의 왼쪽에 있는 크기 범위를 사용하여 선언되며 변수 크기와 일치하는 플롭으로 실현됩니다. 아래 표시된 코드에서 설계 모듈은 클록, 리셋 및 일부 제어 신호를 받아 블록에 읽고 쓸 수 있습니다.

여기에는 레지스터라고 하는 16비트 저장 요소가 포함되어 있어 쓰기 중에 단순히 업데이트되고 읽기 중에 현재 값을 반환합니다. 레지스터는 sel 및 wr이 동일한 클록 에지에서 하이일 때 기록됩니다. sel이 높고 wr이 낮을 때 현재 데이터를 반환합니다.

module des ( input clk,

input rstn,

input wr,

input sel,

input [15:0] wdata,

output [15:0] rdata);

reg [15:0] register;

always @ (posedge clk) begin

if (!rstn)

register <= 0;

else begin

if (sel & wr)

register <= wdata;

else

register <= register;

end

end

assign rdata = (sel & ~wr) ? register : 0;

endmodule

하드웨어 회로도는 쓰기를 위한 제어 로직이 활성화될 때 16비트 플롭이 업데이트되고 읽기를 위해 제어 로직이 구성될 때 현재 값이 반환됨을 보여줍니다.

<노스크립트>

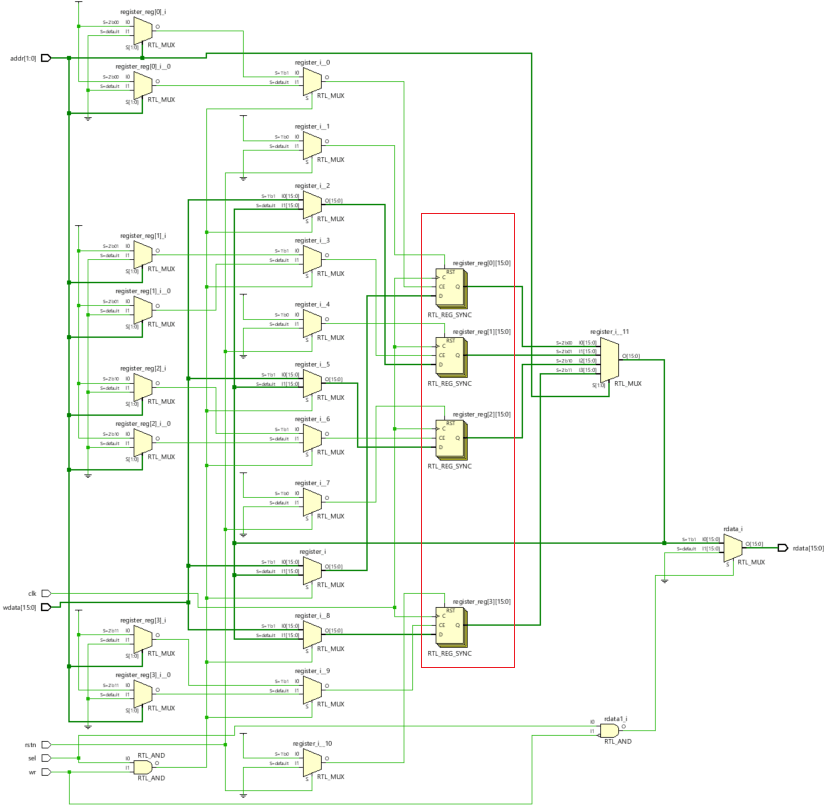

이 예에서 레지스터는 각각 너비가 16비트인 4개의 위치가 있는 배열입니다. 디자인 모듈은 배열의 특정 인덱스에 액세스하기 위해 addr이라고 하는 추가 입력 신호를 받습니다.

module des ( input clk,

input rstn,

input [1:0] addr,

input wr,

input sel,

input [15:0] wdata,

output [15:0] rdata);

reg [15:0] register [0:3];

integer i;

always @ (posedge clk) begin

if (!rstn) begin

for (i = 0; i < 4; i = i+1) begin

register[i] <= 0;

end

end else begin

if (sel & wr)

register[addr] <= wdata;

else

register[addr] <= register[addr];

end

end

assign rdata = (sel & ~wr) ? register[addr] : 0;

endmodule

어레이의 각 인덱스가 16비트 플롭이고 입력 주소가 특정 플롭 세트에 액세스하는 데 사용된다는 하드웨어 회로도를 볼 수 있습니다.

<노스크립트>

verilog

배열은 동일한 유형의 요소에 대한 고정 크기 순차 컬렉션을 저장합니다. 배열은 데이터 모음을 저장하는 데 사용되지만 배열을 인접한 메모리 위치에 저장된 동일한 유형의 변수 모음으로 생각하는 것이 더 유용합니다. number0, number1, ..., number99와 같은 개별 변수를 선언하는 대신 숫자와 같은 하나의 배열 변수를 선언하고 숫자[0], 숫자[1], ..., 숫자[99]를 사용하여 표현합니다. 개별 변수. 배열의 특정 요소는 인덱스에 의해 액세스됩니다. 모든 배열은 연속적인 메모리 위치로 구성됩니다. 가장 낮은

소개: 이 기사에서는 VHDL과 Verilog를 소개합니다. 또한 Verilog 모듈의 기본 구조를 연구하고 Verilog 와이어 데이터 유형과 벡터 형식에 익숙해집니다. Verilog와 VHDL의 기본적인 차이점도 알려드리겠습니다. Verilog란 무엇입니까? Verilog는 IEEE 1364로 표준화된 HDL(Hardware Description Language) 유형입니다. 디지털 회로의 설계 및 검증에 사용되는 전자 회로 및 시스템을 설명하는 데 가장 일반적으로 사용됩니다. VHDL이란 무엇입니까? VHDL은 전자 시