산업기술

소개:

이 기사에서는 VHDL과 Verilog를 소개합니다. 또한 Verilog 모듈의 기본 구조를 연구하고 Verilog '와이어' 데이터 유형과 벡터 형식에 익숙해집니다. Verilog와 VHDL의 기본적인 차이점도 알려드리겠습니다.

Verilog란 무엇입니까?

Verilog는 IEEE 1364로 표준화된 HDL(Hardware Description Language) 유형입니다. 디지털 회로의 설계 및 검증에 사용되는 전자 회로 및 시스템을 설명하는 데 가장 일반적으로 사용됩니다.

VHDL이란 무엇입니까?

VHDL은 전자 시스템의 동작과 구조를 설명하기 위해 전자 설계 자동화에 사용되는 HDL(Hardware Description Language) 유형이기도 하며 특히 디지털 전자 하드웨어 설계의 구조와 동작을 설명하는 언어로 적합합니다. 기존의 디지털 회로.

Verilog와 VHDL이 모두 필요한가요?

계속하기 전에 이 두 언어가 모두 필요한지 논의해 보겠습니다. 둘 다 복잡한 디지털 회로를 설계하는 데 사용되는 강력한 도구이지만 사용하려는 도구를 자유롭게 마스터할 수 있습니다. 그러나 두 언어에 대한 기본적인 이해가 있어야 합니다.

Verilog의 진화

Verilog는 1984년 Gateway Design Automation에서 설계되었습니다. 1987년에 VHDL은 IEEE 표준이 되었고 Verilog는 1995년에 이를 현장에 만들었습니다. 오늘날 이 두 가지 모두 강력한 HDL(하드웨어 설명 언어)입니다. Verilog는 '검증'과 '논리'의 합성어입니다. 언어가 가장 먼저 시뮬레이션 및 검증 도구로 사용되었기 때문입니다.

이제 Verilog의 몇 가지 개념에 대해 논의할 것입니다.

예 1:

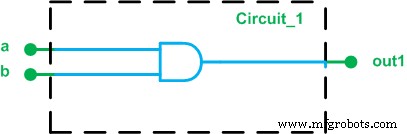

이 예에서는 아래에 표시된 회로에 대한 Verilog 코드를 작성해 보겠습니다.

2개의 입력이 있고 하나의 출력이 표시되며 포트는 1비트 폭입니다. 회로는 out1 포트에서 출력이 발생하는 두 입력의 AND 기능을 보여줍니다. Verilog 설명은 다음과 같이 표시될 수 있습니다.

1행과 8행:

'module'과 'endmodule' 키워드는 Circuit_1을 설명하는 줄을 지정하는 데 사용됩니다.

2~6행:

이 라인은 'Circuit_1'의 환경과 인터페이스를 지정합니다. 'input' 및 'output' 키워드는 입력 및 출력 포트를 나타냅니다. 이 후 키워드 '와이어'는 설계에서 물리적 와이어를 나타내는 Verilog 데이터 유형을 지정합니다. 우리 모듈에는 세 개의 와이어, b 및 out1이 있습니다.

7행:

라인은 비트 AND 연산자 '&'를 사용하여 회로의 AND 기능을 설명합니다. 키워드 '할당; 출력 포트에 &b를 넣는 데 사용됩니다. 이는 표현식이 오른쪽에서 변경될 때마다 항상 활성화되고 왼쪽이 다시 평가되기 때문에 연속 할당이라고도 합니다. 즉, 출력이 지속적으로 업데이트됩니다.

예 1과 VHDL 코드 비교:

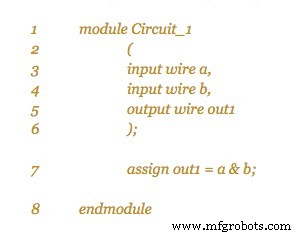

아래 그림은 Circuit_1 모듈에 대한 Verilog 및 VHDL 설명을 보여줍니다.

VHDL에는 데이터 유형과 연산자를 정의하는 일부 라이브러리가 포함되어야 합니다. 따라서 VHDL 코드가 더 설명적입니다. 그러나 어떤 경우에는 이것이 더 높은 수준의 시스템 모델링과 같이 유리합니다.

Verilog의 4가치 시스템:

Verilog 데이터 유형에는 4가지 값이 사용됩니다.

VHDL std_logic 데이터 유형은 9가지 다른 값을 사용할 수 있지만 일반적으로 사용되는 값은 '0', '1', 'Z' 및 '-'입니다('-'는 알 수 없는 값을 나타냄).

예시 2:

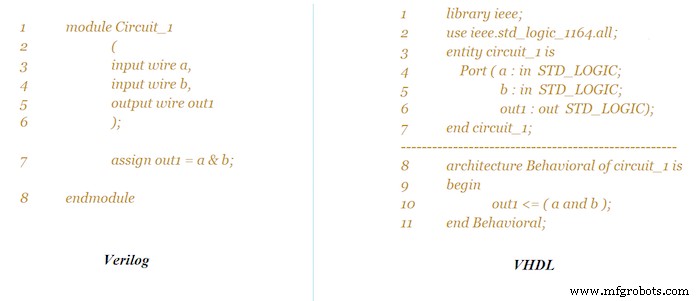

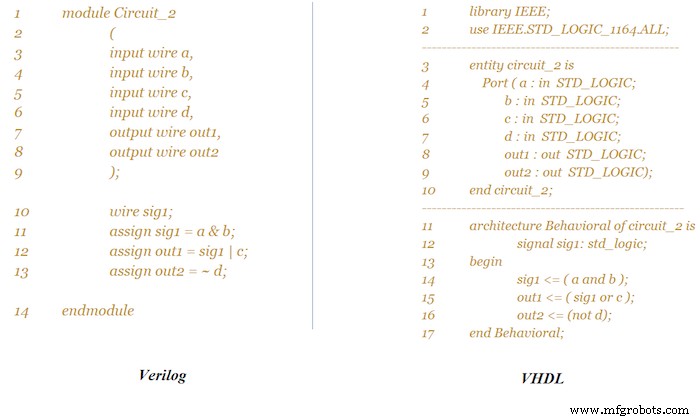

다음 예에서는 아래 그림과 같은 회로(Circuit_2)에 대한 Verilog 코드를 작성해 보겠습니다.

다음 Verilog 코드는 표시된 회로를 설명합니다.

사용된 요소는 이전 예의 요소와 유사하지만 내부 신호는 10행에 정의되어 있습니다. 키워드 '와이어'는 이 연결의 데이터 유형을 지정합니다. 비트 연산자 '~'는 NOT에 사용되고 '|'는 OR 연산에 사용됩니다. 비트 연산자 '^'는 XOR 연산에 사용됩니다.

다음 그림은 Circuit_2 모듈에 대한 Verilog 및 VHDL 설명을 모두 보여주므로 차이점을 관찰할 수 있습니다.

예 3:

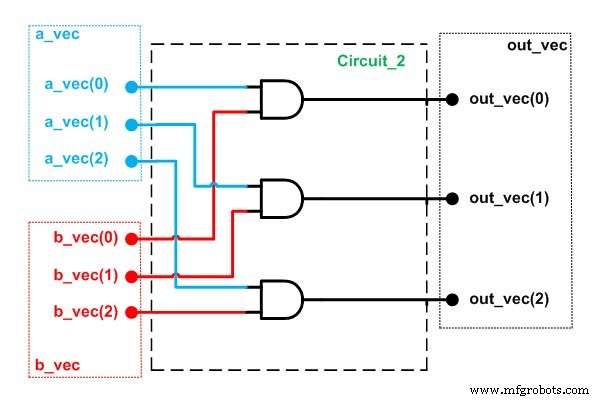

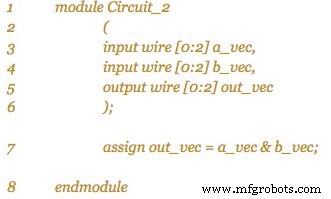

세 번째이자 마지막 예에서는 다음 그림에 표시된 회로도에 대한 Verilog 코드를 제공합니다.  빨간색과 파란색 입력 포트가 AND 연산자와 결합되어 있음을 알 수 있습니다. 결과는 출력 포트로 표시됩니다. 신호를 그룹화하고 코드를 간결하고 읽기 쉽게 만드는 벡터로 처리할 수 있습니다. Verilog 코드를 사용하여 위의 회로를 설명할 수 있습니다. Listing 1의 코드를 쉽게 확장하여 이 회로를 설명할 수도 있습니다.

빨간색과 파란색 입력 포트가 AND 연산자와 결합되어 있음을 알 수 있습니다. 결과는 출력 포트로 표시됩니다. 신호를 그룹화하고 코드를 간결하고 읽기 쉽게 만드는 벡터로 처리할 수 있습니다. Verilog 코드를 사용하여 위의 회로를 설명할 수 있습니다. Listing 1의 코드를 쉽게 확장하여 이 회로를 설명할 수도 있습니다.

벡터의 인덱스 범위는 그림과 같이 오름차순([0:2]) 또는 내림차순([2:0])일 수 있습니다. 내림차순 형식은 일반적으로 오류가 덜 발생하므로 대신 사용할 수 있습니다.

산업기술

최근에 기술은 전자 회로 구성 요소의 진화와 관련하여 엄청난 발전을 보였습니다. 예를 들어, 트랜지스터에는 이제 여러 JFET와 BJT가 있습니다. 그러나 이 경우 고속 조인트 전계 효과 트랜지스터 유형인 TL072 핀아웃에 중점을 둡니다. 저음 또는 고음 제어가 필요한 프로젝트를 수행하려는 경우 TL072 핀아웃이 적합한 IC입니다. 여기에는 오디오 회로, UPS, AC 인버터 및 태양광 인버터가 포함됩니다. 더 나아가 이 모든 연산 증폭기, 핀 구성 및 사용 방법에 대해 논의합니다. (SOIC 패키지의 TL072C 저잡음

선택할 수 있는 금속 합금의 유형만큼 금속 제조 기술의 유형도 많습니다. 초보자이든, 특정 기술의 전문가이든, 금속 가공의 거장이든, 항상 새로운 것을 배울 수 있습니다. 금속 제조 기술은 가산 또는 감산, 자동화 또는 수동 또는 완전히 다른 것일 수 있습니다. 여기에서는 전통적인 것부터 현대적인 것에 이르기까지 다양한 금속 제조 기술을 살펴보고 일반적인 응용 분야에 대해 논의합니다. 전통적인 금속 제조 기술 다음과 같은 전통적인 금속 제조 기술은 오늘날 금속 가공 산업에서 여전히 가장 인기 있고 일반적으로 사용되는 방법 중 일