VHDL

VHDL에서 사용되는 가장 일반적인 유형은 std_logic입니다. . 이 유형을 단일 물리적 와이어에 의해 전달되는 디지털 정보인 단일 비트로 생각하십시오. std_logic integer보다 디자인의 리소스를 더 세밀하게 제어할 수 있습니다. 이전 자습서에서 사용한 유형입니다.

일반적으로 우리는 디지털 인터페이스의 와이어가 '1' 값을 갖기를 원합니다. 또는 '0' . 이 두 값은 비트, 즉 이진수가 가질 수 있는 유일한 값입니다. 그러나 실제로 물리적 디지털 신호는 std_logic과 같은 여러 상태에 있을 수 있습니다. type 은 에뮬레이션을 잘 수행합니다. 따라서 VHDL에서 가장 많이 사용되는 유형입니다.

이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다.

std_logic 유형은 다음 값을 가질 수 있습니다.

| '1' | 논리 1 |

| '0' | 논리 0 |

| 'Z' | 고임피던스 |

| 'ㅁ' | 약한 신호, 0인지 1인지 알 수 없음 |

| 'L' | 약한 0, 풀다운 |

| 'H' | 약한 1, 풀업 |

| '-' | 신경 쓰지 마세요 |

| 'U' | 초기화되지 않음 |

| 'X' | 알 수 없는 여러 드라이버 |

이것은 단일 이진 값을 모델링해야 하는 유형에 대해 다양한 상태처럼 보일 수 있습니다. 걱정하지 마세요. 이 튜토리얼 시리즈에서는 이러한 유형을 모두 사용하지 않을 것입니다. '1'을 사용할 것입니다. 및 '0' 물론. 또한 'U'도 볼 수 있습니다. 및 'X' , 이는 디자인의 오류를 찾는 데 도움이 됩니다. 다른 값은 I

2

와 같은 통신을 모델링하는 데 사용할 수 있는 고급 VHDL 기능입니다. C 장치 또는 3상태 버스를 만들기 위한 것입니다.

여러 프로세스가 신호에 다른 값을 쓰려고 하는 경우 여러 드라이버가 있다고 말합니다. . std_logic인 경우 신호에 여러 드라이버가 있으면 적어도 시뮬레이터에서는 컴파일 또는 런타임 오류가 발생하지 않습니다. std_logic 때문입니다. 해결된 유형입니다. , 값이 분해능 함수에 의해 결정됨을 의미합니다.

std_logic 값 두 개의 드라이버가 있는 신호는 이 분해능 표에 따라 결정됩니다.

| U | X | 0 | 1 | Z | W | L | H | – | |

|---|---|---|---|---|---|---|---|---|---|

| U | X | X | 1 | 1 | 1 | 1 | 1 | X | 1 |

| U | X | 0 | X | 0 | 0 | 0 | 0 | X | 0 |

| U | U | U | U | U | U | U | U | U | U |

| U | X | X | X | X | X | X | X | X | X |

| U | X | 0 | 1 | Z | W | L | H | X | Z |

| U | X | 0 | 1 | W | W | W | W | X | W |

| U | X | 0 | 1 | L | W | L | W | X | L |

| U | X | 0 | 1 | H | W | W | H | X | H |

| U | X | X | X | X | X | X | X | X | – |

이 비디오 자습서에서는 선언을 사용하고 std_logic를 표시하는 방법을 배웁니다. 파형의 신호:

이 튜토리얼에서 만든 최종 코드:

library ieee;

use ieee.std_logic_1164.all;

entity T10_StdLogicTb is

end entity;

architecture sim of T10_StdLogicTb is

signal Signal1 : std_logic := '0';

signal Signal2 : std_logic;

signal Signal3 : std_logic;

begin

process is

begin

wait for 10 ns;

Signal1 <= not Signal1;

end process;

-- Driver A

process is

begin

Signal2 <= 'Z';

Signal3 <= '0';

wait;

end process;

-- Driver B

process(Signal1) is

begin

if Signal1 = '0' then

Signal2 <= 'Z';

Signal3 <= 'Z';

else

Signal2 <= '1';

Signal3 <= '1';

end if;

end process;

end architecture;

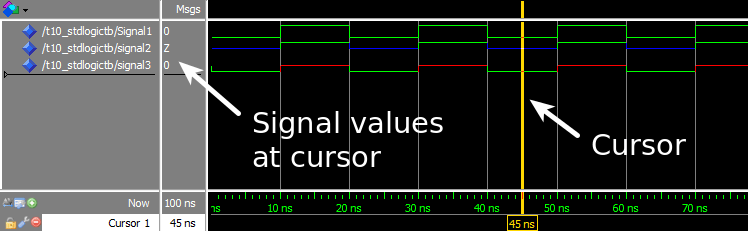

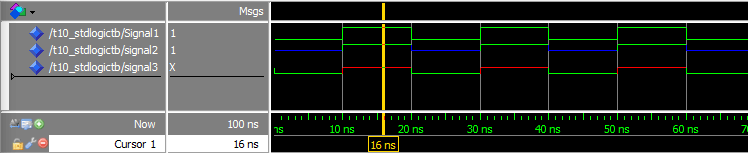

실행을 누르고 타임라인을 확대한 후 ModelSim의 파형 창:

반복되는 신호 주기의 다른 부분에 커서가 있는 파형:

이 연습은 VHDL의 해상도 기능이 std_logic와 어떻게 작동하는지 보여주었습니다. 유형. 디지털 논리로 작업할 때 파형의 타임라인을 연구하는 것이 더 실용적인 경우가 많습니다. 인쇄물을 사용하는 것보다 따라서 이 실습에서는 ModelSim 파형을 사용하여 신호 값을 확인했습니다.

첫 번째 프로세스 및 Signal1 세 번째 프로세스가 Signal2에서 구동하는 값을 변경하는 데만 사용됩니다. 및 Signal3 .

두 번째 프로세스인 드라이버 A는 'Z' Signal2에 및 '0' Signal3에 끊임없이.

세 번째 프로세스인 Driver B는 '1' 운전을 번갈아 가며 진행합니다. 및 'Z' Signal2 모두에 및 Signal3 .

파형 스크린샷에서 Signal1 '0' 사이에서 변경됩니다. 및 '1' , 이 신호를 구동하려는 프로세스가 하나만 있기 때문입니다. 또한 VHDL 코드 주석에 게시된 분해능 표에 따라 여러 드라이버 신호가 해결되었음을 확인할 수 있습니다.

| 신호 | 드라이버 A | 드라이버 B | 결과 |

|---|---|---|---|

| 신호2 | 'Z' | 'Z' | 'Z' |

| 신호2 | 'Z' | '1' | '1' |

| 시그널3 | '0' | 'Z' | '0' |

| 시그널3 | '0' | '1' | 'X' |

std_logic VHDL에서 단일 비트 값을 유지하는 데 사용되는 가장 일반적인 유형입니다.std_logic를 생각해 보세요. 디지털 디자인에서 물리적 와이어로서의 신호std_logic을 구동하려고 하는 경우 신호, 그 값은 분해능 표에 의해 결정됩니다.다음 튜토리얼로 이동 »

VHDL

유압 실린더는 광범위한 기계 및 산업 장비 및 응용 분야에 기능을 제공하는 종종 잊혀지고 종종 간과되는 근육입니다. 잘 엔지니어링되고 세심하게 제작된 유압 실린더 안팎으로 흐르는 압력 유체에서 발생하는 엄청난 양의 동력은 건설, 항공기 지원 및 유지 보수, 폐기물 관리 및 재활용, 철도 운영, 제조 등 다양한 산업 분야에서 미션 크리티컬한 구성 요소입니다. , 해운 및 군대 - 목록은 계속됩니다. 유압 실린더의 고유한 힘과 기능에도 불구하고 여전히 정기적인 유지 관리가 필요하며 때로는 사용되는 응용 분야에 지정된 대로 작동해야 합니

CNC(Computer Numerical Controlled) 가공은 금속 또는 플라스틱의 단일 블록에서 재료 층을 체계적으로 제거하여 부품을 생산하는 절삭 가공 공정입니다. CNC 가공은 대부분 전산화되기 때문에 공차가 매우 정밀하고 복잡한 부품을 생산하는 것으로 유명합니다. CNC 가공은 새로운 것은 아니지만 작동 방식에 대해서는 여전히 약간의 혼란이 있습니다. CNC 머시닝에는 다양한 유형이 있으며 사실을 정확히 파악하는 것은 어려울 수 있습니다. 다음은 엔지니어가 알아야 할 CNC 가공에 대한 가장 일반적인 5가지 오해와