VHDL

std_logic_vector 유형은 VHDL에서 신호 버스를 만드는 데 사용할 수 있습니다. std_logic VHDL에서 가장 일반적으로 사용되는 유형이며 std_logic_vector 배열 버전입니다.

std_logic 동안 단일 와이어로 전달할 수 있는 값을 모델링하는 데는 훌륭하지만 구성 요소에서 오가는 와이어 컬렉션을 구현하는 데는 그다지 실용적이지 않습니다. std_logic_vector 하위 요소의 모음임을 의미하는 복합 유형입니다. std_logic_vector의 신호 또는 변수 유형은 임의의 수의 std_logic를 포함할 수 있습니다. 요소.

이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다.

std_logic_vector 선언 구문 신호:signal <name> : std_logic_vector(<lsb> to <msb>) := <initial_value>;

또는signal <name> : std_logic_vector(<msb> downto <lsb>) := <initial_value>;

여기서 <name> 신호 및 <initial_value>에 대한 임의의 이름입니다. 선택적 초기 값입니다. <lsb> 최하위 비트의 인덱스이며 <msb> 최상위 비트의 인덱스입니다.

to 또는 downto 버스 범위의 방향, 기본적으로 엔디안을 지정합니다. 둘 다 똑같이 잘 작동하지만 VHDL 디자이너가 downto를 사용하여 벡터를 선언하는 것이 가장 일반적입니다. . 따라서 항상 downto을 사용하는 것이 좋습니다. 혼동을 피하기 위해 비트 벡터를 선언할 때.

바이트를 보유할 수 있는 벡터 신호를 선언하기 위한 VHDL 코드:signal MySlv : std_logic_vector(7 downto 0);

1비트를 보유할 수 있는 벡터 신호를 선언하기 위한 VHDL 코드:signal MySlv : std_logic_vector(0 downto 0);

0비트(빈 범위)를 보유할 수 있는 벡터 신호를 선언하기 위한 VHDL 코드 ):signal MySlv : std_logic_vector(-1 downto 0);

이 비디오 자습서에서는 std_logic_vector을 선언하는 방법을 배웁니다. 신호를 보내고 초기 값을 제공합니다. 또한 For-Loop를 사용하여 벡터의 비트를 반복하여 시프트 레지스터를 생성하는 방법도 배웁니다. :

이 튜토리얼에서 만든 최종 코드:

library ieee;

use ieee.std_logic_1164.all;

entity T11_StdLogicVectorTb is

end entity;

architecture sim of T11_StdLogicVectorTb is

signal Slv1 : std_logic_vector(7 downto 0);

signal Slv2 : std_logic_vector(7 downto 0) := (others => '0');

signal Slv3 : std_logic_vector(7 downto 0) := (others => '1');

signal Slv4 : std_logic_vector(7 downto 0) := x"AA";

signal Slv5 : std_logic_vector(0 to 7) := "10101010";

signal Slv6 : std_logic_vector(7 downto 0) := "00000001";

begin

-- Shift register

process is

begin

wait for 10 ns;

for i in Slv6'left downto Slv6'right + 1 loop

Slv6(i) <= Slv6(i-1);

end loop;

Slv6(Slv6'right) <= Slv6(Slv6'left);

end process;

end architecture;

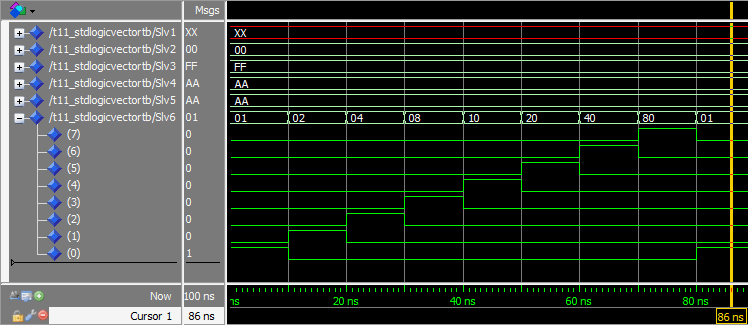

실행을 누르고 타임라인을 확대한 후 ModelSim의 파형 창:

이 연습에서는 6개의 std_logic_vector를 선언했습니다. 버스, 각각 8비트 길이(1바이트).

신호 Slv1 초기 값 없이 선언되었습니다. 파형 스크린샷에서 값이 XX인 버스를 볼 수 있습니다. 버스에 표시되는 값이 16진수이고 XX가 16진수가 아닌 값을 나타내기 때문입니다. 그러나 파형에서 버스를 확장했을 때 개별 비트가 실제로 U임을 알 수 있었습니다.

신호 Slv2 모두 0의 초기 값을 사용하여 선언되었습니다. 각 비트의 정확한 값을 지정하는 대신 (other => '0')를 사용했습니다. 초기 값 대신. 이를 집계라고 합니다. 과제. 중요한 부분은 길이에 관계없이 벡터의 모든 비트를 지정한 값으로 설정한다는 것입니다.

신호 Slv3 모든 비트에 초기 값 1을 제공하기 위해 집계 할당을 사용하여 선언되었습니다. 파형에서 이 신호에 FF가 표시되는 것을 볼 수 있습니다. 이는 8개의 1에 대한 16진수입니다.

신호 Slv4 16진수 AA로 지정된 초기 값으로 선언되었습니다. 각 16진수는 길이가 4비트이므로 벡터에 길이가 8비트인 두 자리(AA)를 제공해야 합니다.

신호 Slv5 Slv4과 정확히 동일한 초기값을 선언합니다. , 그러나 이제 이 값을 2진수 값 10101010으로 지정했습니다. 파형에서 두 신호 모두 16진수 값이 AA임을 알 수 있습니다.

신호 Slv6 '1'인 맨 오른쪽 비트를 제외하고 모두 0의 초기 값으로 선언되었습니다. . 프로세스를 사용하여 시프트 레지스터를 생성했습니다. 이 신호에서. 시프트 레지스터는 이름에서 알 수 있듯이 10나노초마다 벡터의 내용을 왼쪽으로 한 칸 이동합니다.

우리의 프로세스는 10ns마다 깨어나고 For-Loop는 벡터의 모든 비트를 왼쪽으로 한 위치 이동합니다. 마지막 비트는 Slv6(Slv6'right) <= Slv6(Slv6'left);만큼 첫 번째 인덱스로 다시 이동합니다. 성명. 파형에서 '1'을 볼 수 있습니다. 벡터를 통해 파문.

이것은 '1' 시프트 레지스터를 통해 전파됩니다.

'left'을 사용하여 및 'right 속성을 사용하여 코드를 보다 일반적으로 만들었습니다. Sig6의 너비를 변경하면 , 프로세스는 계속 작동합니다. 값을 하드코딩하는 대신 가능한 한 속성을 사용하는 것이 좋은 디자인 방법입니다.

사용할 수 있는 속성이 더 있는지 궁금할 수 있습니다. 고급 VHDL 기능으로 간주하기 때문에 이 튜토리얼 시리즈에서 더 이상 이야기하지 않겠습니다.

std_logic_vector(N-1 downto 0)를 사용하여 선언해야 합니다. (others => '0')를 사용하여 벡터의 모든 비트를 0으로 만들 수 있습니다. 'left과 같은 속성을 사용하여 코드를 보다 일반적으로 만들 수 있습니다. 및 'right

기본 VHDL 퀴즈 – 2부 »

또는

다음 튜토리얼로 이동 »

VHDL

새로운 프로그래밍 언어를 배울 때 저는 항상 인쇄하는 방법을 배우는 것으로 시작하는 것을 좋아합니다. Hello World! 출력을 마스터하면 환경이 작동하고 있음을 알 수 있습니다. 또한 언어의 기본 골격, 출력을 생성하는 데 필요한 최소한의 코드도 보여줍니다. 라고 생각할 수도 있지만 VHDL은 하드웨어 설명 언어인데 어떻게 텍스트를 출력할 수 있습니까? FPGA에 연결된 화면이 필요하고 그 사이에 모든 종류의 로직이 필요하며 이는 전혀 간단하지 않습니다. 이 모든 것이 사실이지만 FPGA와 ASIC은 잠시 잊고 VHDL 언어

3D 프린팅에는 항상 사용자에 따라 달라지는 일련의 요소가 있습니다. , 인쇄가 만족스럽거나 실패하는 경우가 많습니다. 각 사용자가 각 3D 프린트에서 사용하는 프린트 프로필에 모든 요소가 수집됩니다. 3D FDM 인쇄 프로필에서 무한한 수의 매개변수를 수정할 수 있습니다. :프린팅 온도 및 속도, 내부 및 외부 부품 제조 방법 및 3D 프린팅에 영향을 미치는 나머지 모든 매개변수. 이러한 이유로 가장 중요한 정보는 인쇄 프로필을 만들 때 아래에서 설명합니다. 고려할 측면 인쇄 매개변수를 수정하기 전에 직접적으로 영향을 미치