임베디드

RISC-V 시장이 처음 시작되었을 때 초기 러시는 딥 임베디드 애플리케이션에서 독점 CPU 명령 세트 아키텍처(ISA)를 사용했을 설계 비용 절감이었습니다. 이러한 SoC(시스템 온 칩)가 FinFET 반도체 공정 기술로 제조되기 시작했을 때 마스크 비용이 너무 비싸서 많은 유한 상태 기계가 RISC-V 명령 세트를 기반으로 하는 프로그래밍 가능한 마이크로 시퀀서로 대체되었습니다. 이는 2014년부터 2018년까지 간단한 RISC-V 코어의 상품화 초기에 흥분을 일으켰습니다.

RISC-V 아키텍처가 더욱 성숙해지고 SoC 설계자가 ISA에 익숙해짐에 따라 고성능을 요구하는 실시간 애플리케이션, 특히 인공 지능과 같은 애플리케이션을 위한 고도로 전문화된 가속 엔진의 프런트 엔드 역할을 하는 실시간 애플리케이션에 채택되었습니다. . 이러한 채택의 주요 이유 중 하나는 RISC-V가 사용자가 명령을 추가할 수 있는 개방형 아키텍처이기 때문에 RISC-V 프로세서는 기존 아키텍처의 경우처럼 가속기를 메모리 매핑된 I/O 장치로 취급할 필요가 없었기 때문입니다. . 대신 지연 시간이 짧은 보조 프로세서를 사용할 수 있습니다.

벡터 확장 기능이 있는 RISC-V 프로세서의 가용성은 인공 지능(AI), 증강 현실/가상 현실(AR/VR) 및 컴퓨터 비전과 같은 애플리케이션을 위한 커널의 내부 루프 사이에 있는 레이어를 특수 가속기가 처리할 수 있게 했습니다. 그러나 이것은 외부 가속기에서 내부 벡터 레지스터로 데이터를 가져오는 사용자 정의 로드 명령과 같은 특수 목적 확장 없이는 불가능합니다.

이러한 변화를 주도하는 것은 이러한 애플리케이션에서 요구하는 프로그래밍 모델입니다. 하나의 대규모 승수 배열인 특수 목적 가속기는 수행하는 작업과 데이터 이동 모두에서 다소 유연하지만 매우 효율적입니다. 이를 x86과 같은 범용 프로세서와 비교하면 프로그래머가 컴퓨팅 엔진의 제약에 관계없이 프로그래밍할 수 있는 최고의 유연성을 제공합니다. 대부분의 설계에는 그렇지 않은 100W의 전력만 소모할 수 있습니다.

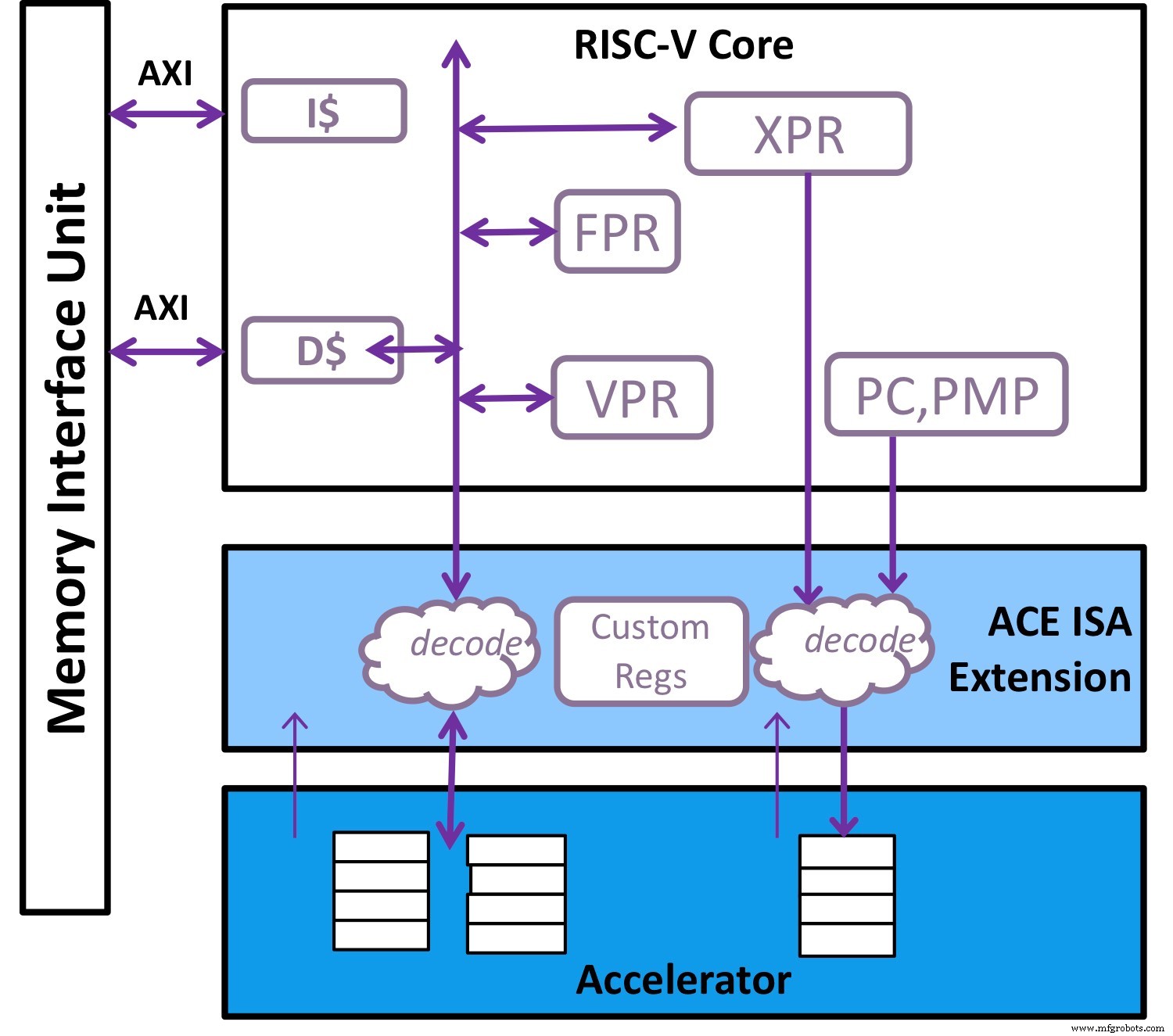

특수 맞춤형 지침으로 보강된 RISC-V의 표준 벡터 확장은 가속기의 이상적인 동반자입니다(이미지:Andes Technology)

분명한 해결책은 범용 CPU의 유연성과 매우 특정한 작업을 처리할 수 있는 가속기를 결합하는 것입니다(위 그림 참조). RISC-V에서 전문화된 맞춤형 명령어로 보강된 성숙한 표준 벡터 확장은 가속기의 이상적인 동반자이며, 이러한 채택은 지난 18개월 동안 DSA(도메인별 가속) 솔루션이 RISC-V 플랫폼에 수렴됨에 따라 명백해졌습니다.

이 비전을 가능하게 하기 위해 우리는 가속기가 메모리를 포함한 자체 리소스를 사용하여 자체 명령 세트를 실행할 수 있어야 함을 관찰했습니다. 가속기의 실행을 간소화하기 위해 RISC-V는 마이크로코드를 필요한 만큼 확장하고 필요한 모든 제어 정보를 하나의 명령으로 가속기에 압축할 수 있어야 합니다. 또한 이 가속기 명령 집합은 RISC-V 프로세서의 스칼라 레지스터 및 벡터 레지스터는 물론 제어 레지스터 파일 및 메모리와 같은 자체 리소스를 인식해야 합니다.

액셀러레이터가 특별한 방식으로 데이터를 재정렬하거나 조작하는 데 도움이 필요할 때 Andes 아키텍처는 벡터 처리 장치(VPU)로 이를 처리하여 데이터 순열 이동, 수집, 압축 및 확장의 복잡한 작업을 처리합니다. 레이어 사이에는 합병증을 수반하는 일부 커널이 있습니다. 여기에서 VPU는 이러한 요구 사항을 해결하는 데 도움이 되는 유연성을 제공합니다. 이 소켓에서 가속기와 VPU는 모두 엄청난 양의 병렬 계산을 수행합니다. 따라서 하드웨어를 추가하여 계산 요구에 맞게 메모리 하위 시스템의 대역폭을 크게 높였습니다. 여기에는 프리페치 및 비순차적 반환이 있는 비차단 트랜잭션이 포함되지만 이에 국한되지 않습니다.

최신 V-extension 0.8 버전을 지원하는 Andes Technology의 첫 RISC-V 벡터 프로세서인 NX27V는 8-bit, 16-bit, 32-bit 정수 단위에서 16-bit, 32-bit 부동소수점까지 각각의 연산을 수행합니다. 또한 기계 학습 알고리즘의 가중치 값에 대한 저장 및 전송 대역폭을 줄이기 위해 Bfloat16 및 Int4 형식을 지원합니다. RISC-V 벡터 사양은 설계자가 벡터 길이, 각 벡터 레지스터의 비트 수, SIMD 너비, 각 사이클마다 벡터 엔진이 처리하는 비트 수와 같은 주요 설계 매개변수를 구성할 수 있도록 하는 데 있어 매우 유연합니다.

NX27V는 최대 512비트의 벡터 길이를 가지며 최대 8개의 벡터 레지스터를 결합하여 4096비트까지 확장할 수 있습니다. 병렬 파이프라인에서 작동하는 여러 기능 장치가 추가되어 다양한 애플리케이션에 필요한 계산 처리량을 유지할 수 있습니다. 512비트 벡터 길이와 동일한 SIMD 너비로 구성된 구현에서는 0.3mm 2 영역 내에서 최악의 조건에서 7nm에서 1GHz 속도에 도달합니다. . 소프트웨어 개발 지원을 위해 컴파일러, 디버거, 벡터 라이브러리 및 사이클 시뮬레이터, NX27V 파이프라인용 시각화 도구인 Clarity는 중요한 루프의 성능을 분석하고 최적화하는 데 도움이 됩니다. 이 솔루션은 이미 사전 체험판 프로그램에서 제공되기 시작했습니다.

지난 15개월 동안 우리는 강력한 RISC-V 벡터 확장을 추가하고 이를 고대역폭 메모리 하위 시스템과 일치시키고 가속기를 CPU에 더 가깝게 가져옴으로써 고성능에 대한 많은 수요를 보았습니다. 이것이 RISC-V 및 벡터 처리에 대한 수요를 주도할 것으로 생각되는 컴퓨팅 요구 사항 유형입니다.

>> 이 기사는 원래 다음 날짜에 게시되었습니다. 자매 사이트인 EE Times.

임베디드

클라우드 네이티브는 이미 소프트웨어 개발의 미래로 입증되었습니다. 2025년까지 엔터프라이즈 앱의 80%가 클라우드 기반이 되거나 클라우드 네이티브 앱으로 전환하는 과정에 있을 것입니다. IT 부서는 비용을 절감하고 설계를 오프사이트에서 안전하게 유지하기 위해 클라우드로 마이그레이션하고 있습니다. 이러한 전환에 대해 생각하기 전에 해당 애플리케이션의 아키텍처를 이해해야 합니다. 클라우드 네이티브 아키텍처란 무엇입니까? 클라우드 네이티브 애플리케이션은 클라우드 컴퓨팅 인프라에서 실행되는 컨테이너에 패키징된 마이크로서비스로 구성됩니

자동화된 로봇 시스템은 40년 이상 공장에서 작동해 왔습니다. 그들 중 다수는 주기적으로 적절한 로봇 유지 보수를 받는 한 동일한 작업을 수십 년 동안 지속할 수 있습니다. 로봇에 이러한 유지 보수를 수행함으로써 제조업체는 누구나 상상할 수 있는 것 이상으로 로봇의 수명을 연장할 것입니다. 좋은 로봇은 올바른 유지 관리를 통해 수십 년 동안 사용할 수 있습니다. 그러나 잘못된 유지 관리로 인해 정기적으로 중단 및 생산 중단이 발생할 수 있습니다. 로봇은 적절하게 기름칠을 해야 하고 로봇의 기어와 관절은 생산 중에 관절이 마모되