산업기술

논리 회로는 n비트 값을 함께 추가하기 위해 리플 캐리 가산기에 의존할 수 있습니다. 결과적으로 이 디지털 회로 구현은 많은 애플리케이션에서 유용한 기능을 제공합니다. 그러나 느린 계산 프로세스로 인해 지연된 성능도 나타납니다. 여기에는 일반적으로 각 전가산기 단계가 비트를 다음 전가산기 단계로 파급할 때까지 기다리는 것이 포함됩니다. 이러한 프로세스는 끝에 도달할 때까지 반복되어 결과를 제공합니다.

리플 캐리 가산기를 이해하는 것은 다소 혼란스러울 수 있습니다. 이를 염두에 두고 이 주제에 대해 더 많은 지식을 얻을 수 있도록 이 기사를 작성했습니다. 그럼 시작하겠습니다!

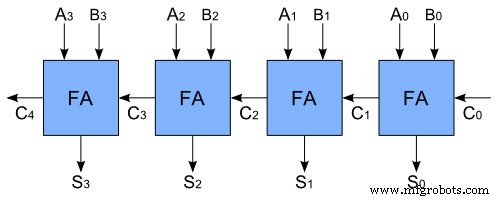

리플 캐리 가산기는 두 개의 이진 n비트 수를 더하고 결과를 제공하는 디지털 회로 역할을 합니다. 그 구조는 여러 개의 전가산기로 구성되며 각 가산기는 계단식 설정으로 연결됩니다. 이러한 방식으로 전가산기의 캐리 출력은 다음 전가산기 입력에 연결됩니다.

4비트 리플의 다이어그램은 가산기를 운반합니다.

출처:Wikimedia Commons

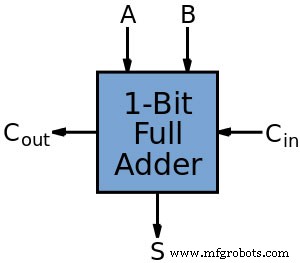

전가산기는 2개의 출력을 생성하면서 3개의 입력을 추가하도록 설계된 논리 회로를 나타냅니다. 보다 구체적으로 두 개의 입력은 A와 B 역할을 하고 세 번째 입력은 캐리인 비트를 나타냅니다. (C-IN) 한편, 하나의 출력은 캐리아웃 비트(C-OUT)를 나타내고, 다른 하나는 합 비트(S)를 나타낸다. 궁극적으로 전체 가산기 회로는 8개의 입력에 연결하여 바이트 전체 가산기를 형성할 수 있습니다. 이것은 한 가산기에서 다음 가산기로 캐리 비트를 캐스케이드합니다. 두 개의 반가산기 회로를 결합하면 전가산기가 됩니다.

완전한 가산기 논리 다이어그램

출처:Wikimedia Commons

각 캐리는 전체 가산기 단계를 통해 생성되고 입력을 통해 다음 전체 가산기로 진행됩니다. 전체 프로세스는 최종 전체 가산기에 도달할 때까지 진행됩니다. 결과적으로 각 캐리 출력 비트는 다음 전가산기 단계로 리플이 발생합니다. 전반적으로 가장 중요한 작업은 4비트 가산기, 8비트 가산기, 16비트 가산기 등과 같이 각 입력 비트 시퀀스를 함께 추가하는 것입니다.

논리 회로의 전파 지연으로 인해 합계 및 캐리아웃 비트는 캐리인 단계가 발생할 때까지 유효하지 않은 상태로 유지됩니다. 전파 지연은 일반적으로 입력과 출력 사이에 경과된 시간으로 인해 발생합니다. 예를 들어 NOT 게이트 입력이 0으로 설정되면 출력은 1 등으로 구성됩니다. 전파 지연은 출력 설정을 0으로 설정하고 입력을 1로 구성하는 사이에 경과된 시간을 정의합니다. 또한 캐리 전파 지연은 캐리인 신호를 수신하고 캐리아웃 신호를 구현하는 데 걸리는 시간을 정의합니다.

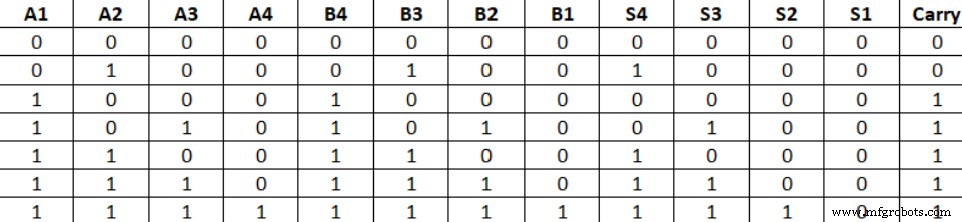

아래 그림과 같이 진리표는 리플 캐리 가산기의 모든 입력에 대한 각 출력 값을 결정합니다.

잔물결은 가산기 진리표를 전달합니다.

리플 캐리 가산기를 구현하려면 VHDL 코드와 Verilog 코드가 필요합니다. 두 가지 예가 제공됩니다. 첫 번째는 2비트 리플 캐리 가산기를 포함합니다. 한편, 다른 예는 각 입력 너비를 매개변수로 수집하는 리플 캐리 가산기를 생성합니다.

시계에는 리플 캐리 가산기가 포함되어 있습니다.

장점

리플 캐리 가산기는 저렴합니다.

출처:Wikimedia Commons

단점

지연으로 인해 전반적인 기능에 불편함

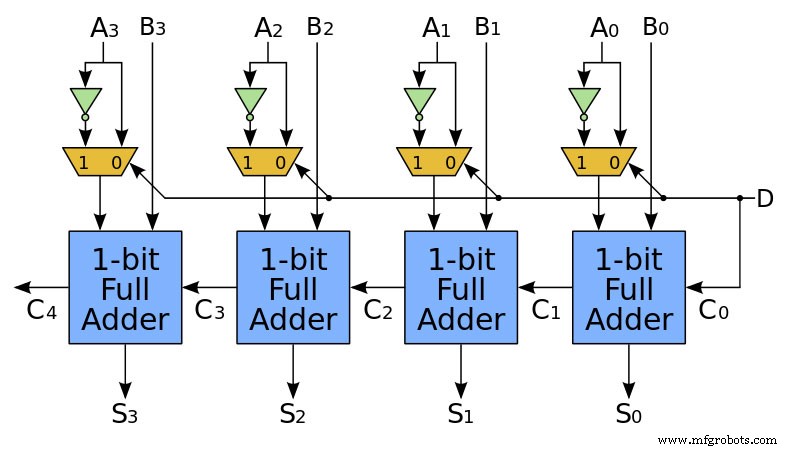

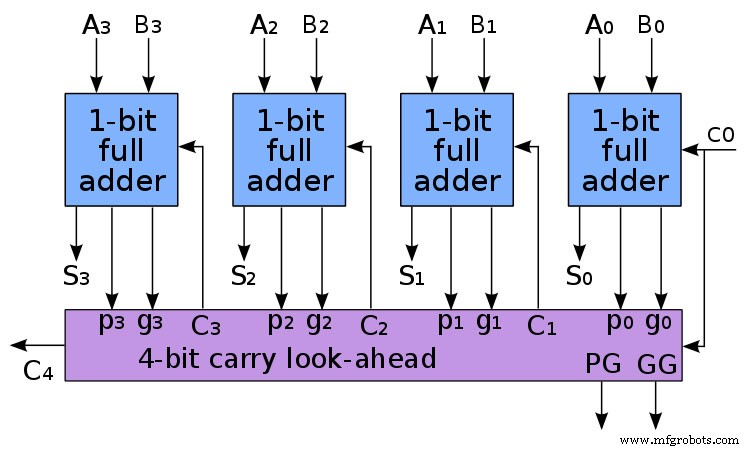

캐리 예측 로직은 합에 도달하기 전에 캐리인 비트를 계산하여 시간 지연을 효과적으로 줄입니다. 이는 두 가지 방법을 통해 캐리 신호를 생성한 후 발생합니다. 첫 번째 비트는 1과 동일한 a 및 b 비트를 모두 포함합니다. 한편, 두 번째 접근 방식은 캐리인 및 1에 해당하는 a 또는 b 비트를 포함합니다. 이 비트는 이전 단계에서 구현되고 캐리인은 가산기의 시작 부분에서 시작됩니다.

미리보기 가산기 회로도를 수행하십시오.

출처:Wikimedia Commons

리플 캐리 가산기에서 각 전가산기는 합을 계산하기 전에 다음 가산기로 캐리인 비트를 처리합니다. 따라서 해당 프로세스는 긴 지연을 초래합니다.

전반적으로 캐리 리플 가산기는 디지털 회로에서 두 개의 n비트 숫자를 더할 수 있는 기능을 제공합니다. 느린 프로세스이지만 여전히 디지털 신호 처리에 본질적으로 도움이 되는 유용한 응용 프로그램이 있습니다. 이러한 방식으로 리플 캐리 가산기는 최종 전체 가산기에 도달할 때까지 각 전가산기 단계에 캐리인 비트를 리플링합니다. 이 시점에서 필요한 계산을 수행합니다. 그러나 carry-lookahead 가산기는 다른 기술을 사용하기 때문에 이 계산을 더 빨리 수행합니다. 따라서 지연 시간을 줄입니다.

리플 캐리 가산기에 대해 질문이 있습니까? 언제든지 저희에게 연락하십시오!

산업기술

3D 프린터는 디지털 3D 모델 파일을 사용하여 레이어로 구성 요소를 만듭니다. 이 파일에는 3D 슬라이서가 모델을 수평 레이어로 나누고 3D 프린터에 어떤 움직임을 만들어야 하는지 알려주는 언어인 G 코드를 생성하는 데 사용하는 데이터 전달 비트가 포함되어 있습니다. 그러나 각 형식에 다른 정보가 포함되어 있기 때문에 3D 프린팅에 어떤 파일 형식도 사용할 수 없습니다. 다음은 STL 파일에 대해 알아야 할 모든 것입니다. STL 파일이란 무엇입니까? STL 파일(STL은 표준 테셀레이션 언어(Standard Tessellati

핫 스탬핑이란 무엇입니까? 핫 스탬핑은 가열된 이미지 몰드 또는 스탬핑 다이를 사용하여 금속 호일 또는 사전 건조된 잉크를 표면에 전사하는 리소그래피 인쇄 프로세스입니다. 일반적으로 프로세스는 다음과 같이 작동합니다. 핫 스탬핑 기계는 새겨진 몰드 또는 다이를 가열한 다음 마킹 호일을 표면에 누릅니다. 호일은 핫 스탬프가 제품 재료와 접촉하는 위치에만 증착되므로 엔지니어는 후반 작업에서 부품 및 어셈블리에 우아하고 양각된 디자인을 만들 수 있습니다. 핫 스탬핑 포일은 색상 층(안료 또는 금속일 수 있음), 접착 베이스 및 이형