verilog

플립플롭은 클록의 양수 또는 음수 에지 입력에서 데이터를 캡처합니다. 주목해야 할 중요한 점은 다음 클럭 에지까지 클럭 에지 이후 데이터에 어떤 일이 발생하든지 출력에 반영되지 않는다는 것입니다. 래치 반면에 인에이블 핀이 어서트되어 있는 한 출력은 클록 에지에서 캡처하지 않고 입력을 따릅니다.

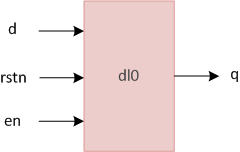

이 예에서는 3개의 입력과 1개의 출력이 있는 래치를 만들 것입니다. 입력 d 0 또는 1이 될 수 있는 데이터를 나타냅니다. rstn 액티브 로우 리셋 및 en을 나타냅니다. 입력 데이터를 출력에 래치하는 데 사용되는 활성화를 나타냅니다. 리셋이 액티브 로우라는 것은 단순히 이 입력이 0이 될 때 디자인 요소가 리셋된다는 것을 의미합니다. 즉, 리셋은 값이 낮을 때 활성화됩니다. 출력 q의 값 입력 d에 의해 결정됩니다. , ko 그리고 처음 .

<노스크립트>

module d_latch ( input d, // 1-bit input pin for data

input en, // 1-bit input pin for enabling the latch

input rstn, // 1-bit input pin for active-low reset

output reg q); // 1-bit output pin for data output

// This always block is "always" triggered whenever en/rstn/d changes

// If reset is asserted then output will be zero

// Else as long as enable is high, output q follows input d

always @ (en or rstn or d)

if (!rstn)

q <= 0;

else

if (en)

q <= d;

endmodule

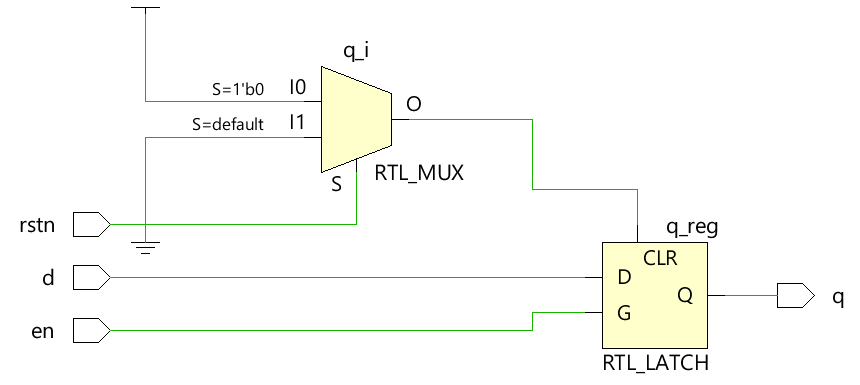

always에 대한 민감도 목록에 유의하십시오. 블록은 출력을 업데이트하는 데 필요한 모든 신호를 포함합니다. 이 블록은 감도 목록에 있는 신호가 값을 변경할 때마다 트리거됩니다. 또한 q en일 때만 d 값을 얻습니다. 높으므로 양성입니다. 걸쇠.

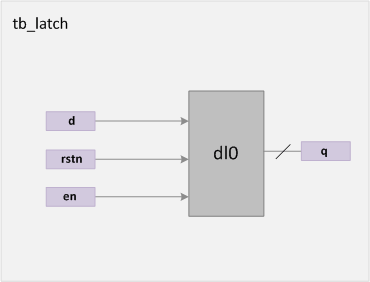

module tb_latch;

// Declare variables that can be used to drive values to the design

reg d;

reg en;

reg rstn;

reg [2:0] delay;

reg [1:0] delay2;

integer i;

// Instantiate design and connect design ports with TB signals

d_latch dl0 ( .d (d),

.en (en),

.rstn (rstn),

.q (q));

// This initial block forms the stimulus to test the design

initial begin

$monitor ("[%0t] en=%0b d=%0b q=%0b", $time, en, d, q);

// 1. Initialize testbench variables

d <= 0;

en <= 0;

rstn <= 0;

// 2. Release reset

#10 rstn <= 1;

// 3. Randomly change d and enable

for (i = 0; i < 5; i=i+1) begin

delay = $random;

delay2 = $random;

#(delay2) en <= ~en;

#(delay) d <= i;

end

end

endmodule

테스트벤치가 더 무작위적인 방식으로 신호를 주장하고 주장하지 않도록 하기 위해 reg을 선언했습니다. 지연이라는 변수 크기가 3비트이므로 0에서 7 사이의 값을 사용할 수 있습니다. 그런 다음 지연 변수는 d 할당을 지연하는 데 사용됩니다. 및 ko 모든 루프에서 다른 패턴을 얻으려면.

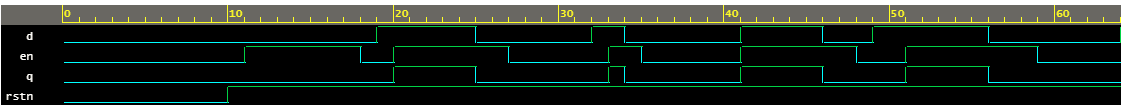

ncsim> run [0] en=0 d=0 q=0 [11] en=1 d=0 q=0 [18] en=0 d=0 q=0 [19] en=0 d=1 q=0 [20] en=1 d=1 q=1 [25] en=1 d=0 q=0 [27] en=0 d=0 q=0 [32] en=0 d=1 q=0 [33] en=1 d=1 q=1 [34] en=1 d=0 q=0 ncsim: *W,RNQUIE: Simulation is complete.

이미지를 클릭하시면 크게 보실 수 있습니다.

<노스크립트>

verilog

nand과 같은 표준 Verilog 프리미티브 및 not 복잡한 논리를 표현하기에는 항상 쉽거나 충분하지 않을 수 있습니다. UDP라는 새로운 기본 요소 또는 사용자 정의 프리미티브 조합 논리 또는 순차 논리를 모델링하도록 정의할 수 있습니다. 모든 UDP에는 0, 1 또는 X가 될 수 있고 Z가 될 수 없는 정확히 하나의 출력이 있습니다(지원되지 않음). Z 값을 갖는 모든 입력은 X로 처리됩니다. Verilog UDP 기호 Verilog 사용자 정의 프리미티브는 module과 동일한 수준에서 작성할 수 있습니다. 정의, 그러

먹스 또는 멀티플렉서란 무엇입니까? 멀티플렉서 또는 mux 요컨대 선택 신호를 기반으로 N 입력 중 하나에서 출력으로 데이터를 전송하는 디지털 요소입니다. 아래에 표시된 경우는 N이 4인 경우입니다. 예를 들어, 4비트 멀티플렉서는 선택 신호를 사용하여 각 입력을 출력으로 전송할 수 있는 4비트 각각의 N 입력을 갖습니다. sel은 2비트 입력이며 4개의 값을 가질 수 있습니다. 선택 라인의 각 값은 입력 중 하나를 출력 핀 아웃으로 보낼 수 있도록 합니다. sel a b c d out