verilog

4비트 카운터는 4'b0000에서 4'h1111로 증가하기 시작한 다음 다시 4'b0000으로 롤오버됩니다. 실행 중인 시계가 제공되고 재설정이 높게 유지되는 한 계속 계산됩니다.

롤오버는 최종 추가의 가장 중요한 비트가 폐기될 때 발생합니다. 카운터가 최대값이 4'b1111이고 한 번 더 카운트 요청을 받으면 카운터는 5'b10000에 도달하려고 시도하지만 4비트만 지원할 수 있으므로 MSB는 폐기되어 0이 됩니다.

0000 0001 0010 ... 1110 1111 rolls over 0000 0001 ...

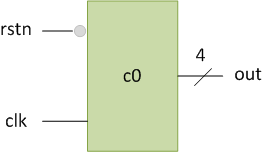

이 설계에는 클록용 입력과 액티브 로우 리셋용 입력이 있습니다. 액티브 로우 리셋은 리셋 핀의 값이 0일 때 디자인이 리셋되는 것입니다. 본질적으로 카운터 값을 제공하는 4비트 출력이 호출됩니다.

<노스크립트>

module counter ( input clk, // Declare input port for clock to allow counter to count up

input rstn, // Declare input port for reset to allow the counter to be reset to 0 when required

output reg[3:0] out); // Declare 4-bit output port to get the counter values

// This always block will be triggered at the rising edge of clk (0->1)

// Once inside this block, it checks if the reset is 0, if yes then change out to zero

// If reset is 1, then design should be allowed to count up, so increment counter

always @ (posedge clk) begin

if (! rstn)

out <= 0;

else

out <= out + 1;

end

endmodule

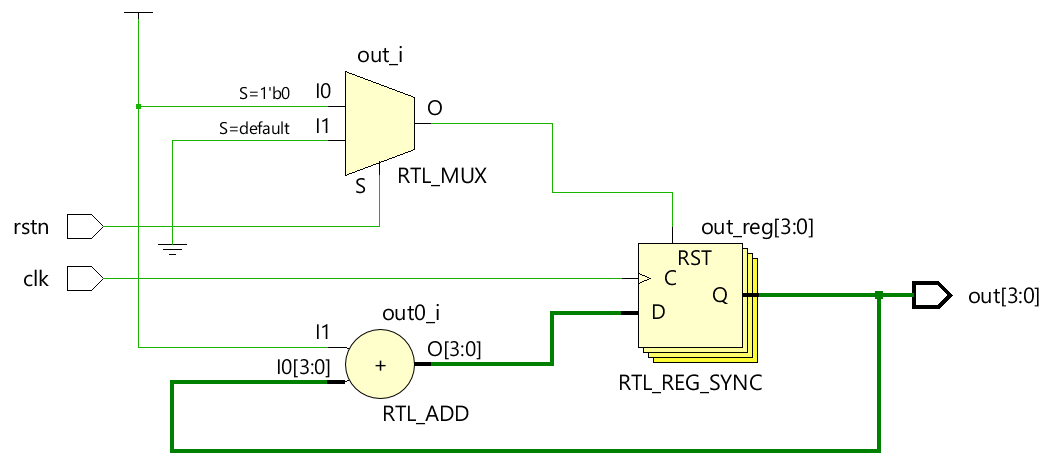

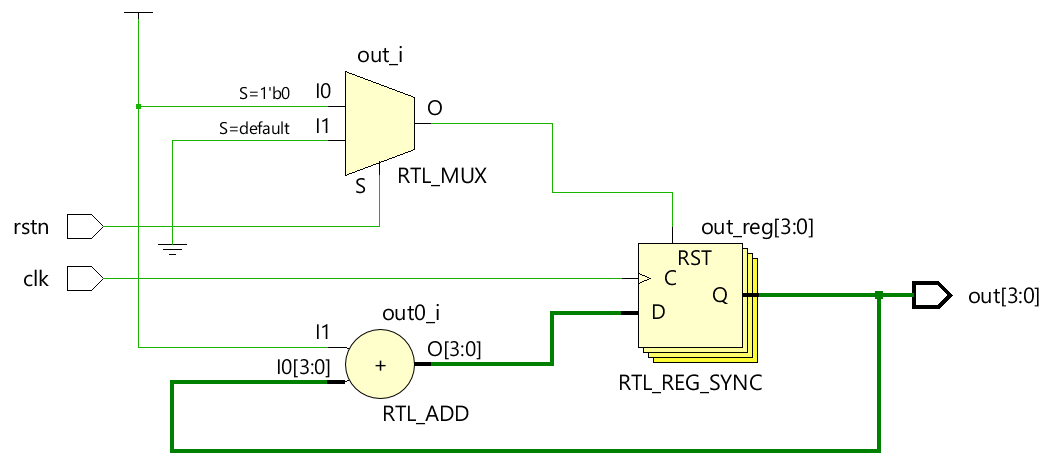

module 카운터에는 클럭과 활성 로우 리셋(n으로 표시됨)이 있습니다. )를 입력으로 사용하고 카운터 값을 4비트 출력으로 사용합니다. always 차단은 항상입니다. 상승 에지 또는 양의 에지를 나타내는 0에서 1로 클럭이 전환될 때마다 실행됩니다. if-else에 의해 달성되는 리셋이 하이 또는 1로 유지되는 경우에만 출력이 증가합니다. 차단하다. 클럭의 양의 에지에서 리셋이 낮은 것으로 확인되면 출력은 기본값인 4'b0000으로 리셋됩니다.

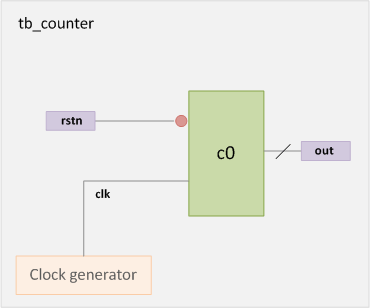

설계를 테스트벤치 모듈로 인스턴스화하여 카운터가 예상대로 계산되는지 확인할 수 있습니다.

<노스크립트>

테스트벤치 모듈의 이름은 tb_counter입니다. 시뮬레이션의 최상위 모듈이므로 포트가 필요하지 않습니다. 그러나 클럭을 생성, 저장 및 구동하고 재설정하려면 내부 변수가 필요합니다. 이를 위해 reg 유형의 두 변수를 선언했습니다. 시계 및 재설정을 위해. wire도 필요합니다. net을 입력하여 디자인의 출력과 연결합니다. 그렇지 않으면 기본적으로 1비트 스칼라 네트로 설정됩니다.

시계는 always를 통해 생성됩니다. 10 시간 단위의 기간을 제공하는 블록. initial 블록은 초기 값을 내부 변수로 설정하고 재설정 값을 설계에 적용하는 데 사용됩니다. 디자인이 인스턴스화됩니다. 테스트벤치에서 내부 변수에 연결하여 테스트벤치에서 값을 가져올 때 값을 얻습니다. $display이(가) 없습니다. 테스트벤치에서 명령문을 실행하므로 콘솔에 메시지가 표시되지 않습니다.

module tb_counter;

reg clk; // Declare an internal TB variable called clk to drive clock to the design

reg rstn; // Declare an internal TB variable called rstn to drive active low reset to design

wire [3:0] out; // Declare a wire to connect to design output

// Instantiate counter design and connect with Testbench variables

counter c0 ( .clk (clk),

.rstn (rstn),

.out (out));

// Generate a clock that should be driven to design

// This clock will flip its value every 5ns -> time period = 10ns -> freq = 100 MHz

always #5 clk = ~clk;

// This initial block forms the stimulus of the testbench

initial begin

// 1. Initialize testbench variables to 0 at start of simulation

clk <= 0;

rstn <= 0;

// 2. Drive rest of the stimulus, reset is asserted in between

#20 rstn <= 1;

#80 rstn <= 0;

#50 rstn <= 1;

// 3. Finish the stimulus after 200ns

#20 $finish;

end

endmodule

시뮬레이션 로그 ncsim> run [0ns] clk=0 rstn=0 out=0xx [5ns] clk=1 rstn=0 out=0x0 [10ns] clk=0 rstn=0 out=0x0 [15ns] clk=1 rstn=0 out=0x0 [20ns] clk=0 rstn=1 out=0x0 [25ns] clk=1 rstn=1 out=0x1 [30ns] clk=0 rstn=1 out=0x1 [35ns] clk=1 rstn=1 out=0x2 [40ns] clk=0 rstn=1 out=0x2 [45ns] clk=1 rstn=1 out=0x3 [50ns] clk=0 rstn=1 out=0x3 [55ns] clk=1 rstn=1 out=0x4 [60ns] clk=0 rstn=1 out=0x4 [65ns] clk=1 rstn=1 out=0x5 [70ns] clk=0 rstn=1 out=0x5 [75ns] clk=1 rstn=1 out=0x6 [80ns] clk=0 rstn=1 out=0x6 [85ns] clk=1 rstn=1 out=0x7 [90ns] clk=0 rstn=1 out=0x7 [95ns] clk=1 rstn=1 out=0x8 [100ns] clk=0 rstn=0 out=0x8 [105ns] clk=1 rstn=0 out=0x0 [110ns] clk=0 rstn=0 out=0x0 [115ns] clk=1 rstn=0 out=0x0 [120ns] clk=0 rstn=0 out=0x0 [125ns] clk=1 rstn=0 out=0x0 [130ns] clk=0 rstn=0 out=0x0 [135ns] clk=1 rstn=0 out=0x0 [140ns] clk=0 rstn=0 out=0x0 [145ns] clk=1 rstn=0 out=0x0 [150ns] clk=0 rstn=1 out=0x0 [155ns] clk=1 rstn=1 out=0x1 [160ns] clk=0 rstn=1 out=0x1 [165ns] clk=1 rstn=1 out=0x2 Simulation complete via $finish(1) at time 170 NS + 0<노스크립트>

액티브 로우 리셋이 0이 되면 카운터가 0으로 리셋되고, 약 150ns에서 리셋이 해제되면 카운터는 클럭의 다음 발생 시점부터 카운트를 시작합니다.

verilog

Fanuc TC에서 프로그램 편집 후 재설정 CNC 기계공은 CNC 부품 프로그램을 변경하는 경우 FANUC TC cnc 제어 기능이 있는 cnc 기계(예:Gildemeister NEF 560)에서 CYCLE START를 누르기 전에 항상 RESET 버튼을 누르는 것을 기억해야 합니다.

Heidenhain TNC 640/530/410/426/430/320용 Heidenhain M 코드(기타 기능) 하이덴하인 TNC 320 하이덴하인 M 코드 M 코드 설명 M0 프로그램 실행 중지(Spindle STOP, Coolant OFF) M1 옵션 프로그램 STOP(스핀들 STOP, 절삭유 OFF) M2 프로그램 실행 중지(스핀들 정지, 냉각수 꺼짐, 블록 1로 이동, 상태 표시 지우기(기계 매개변수에 따라 다름)) M3 시계 방향으로 스핀들 ON M4 시계 반대 방향으로 스핀들 ON M5 스핀들 정지 M6