VHDL

VHDL은 끔찍한 약어입니다. V를 나타냅니다. HSIC H 하드웨어 D 설명 L 앙앙. 약어 안의 약어, 굉장합니다! VHSIC는 V를 나타냅니다. 에리 H 응 S 오줌 나 통합된 C 일렉트릭. 따라서 확장된 VHDL은 V입니다. ery 고속 집적 회로 H 하드웨어 D 설명 L 앙앙. PHEW 한 입입니다. VHDL은 교육 및 비즈니스에서 FPGA 및 ASIC을 설계하는 데 사용하는 두 가지 언어 중 하나입니다. 이러한 매혹적인 회로에 익숙하지 않은 경우 먼저 FPGA 및 ASIC에 대한 소개를 통해 이점을 얻을 수 있습니다. VHDL 및 Verilog는 디지털 설계자가 회로를 설명하는 데 사용하는 두 가지 언어이며 C 및 Java와 같은 기존 소프트웨어 언어와는 설계상 다릅니다.

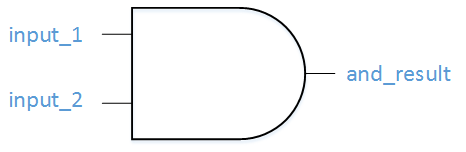

아래 예에서는 설명하는 VHDL 파일을 생성할 것입니다. 앤 게이트. 간단히 말해서 And Gate에는 두 개의 입력과 하나의 출력이 있습니다. 두 입력이 모두 1일 때만 출력은 1입니다. 아래는 VHDL로 설명할 And Gate의 그림입니다.

앤드 게이트

앤드 게이트 가자! VHDL의 기본 단위를 신호라고 합니다. . 지금은 신호가 0 또는 1일 수 있다고 가정해 보겠습니다(실제로 다른 가능성이 있지만 우리는 그것에 대해 알아보겠습니다). 다음은 몇 가지 기본 VHDL 논리입니다.

signal and_gate : std_logic; and_gate <= input_1 and input_2;

코드의 첫 번째 줄은 std_logic 유형의 신호를 정의하며 이를 and_gate라고 합니다. Std_logic은 신호를 정의하는 데 가장 일반적으로 사용되는 유형이지만 배우게 될 다른 유형도 있습니다. 이 코드는 단일 출력(and_gate)과 2개의 입력(input_1 및 input_2)으로 AND 게이트를 생성합니다. 키워드 "and"는 VHDL에 예약되어 있습니다. <=연산자는 할당 연산자로 알려져 있습니다. 위의 코드를 구두로 구문 분석할 때 "The signal and_gate GETS input_1 and-ed with input_2"라고 큰 소리로 말할 수 있습니다.

이제 input_1과 input_2가 어디에서 왔는지 스스로에게 물을 수 있습니다. 이름에서 알 수 있듯이 이 파일에 대한 입력이므로 도구에 이에 대해 알려야 합니다. 파일에 대한 입력 및 출력은 엔티티에 정의됩니다. . 엔티티에는 파일에 대한 모든 입력 및 출력을 정의하는 포트가 있습니다. 간단한 엔터티를 만들어 보겠습니다.

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

이것은 당신의 기본 엔티티입니다. example_and라는 엔티티와 3개의 신호, 2개의 입력과 1개의 출력을 정의하며, 모두 std_logic 유형입니다. 이 작업을 완료하려면 아키텍처가 하나의 다른 VHDL 키워드가 필요합니다. . 아키텍처는 특정 엔터티의 기능을 설명하는 데 사용됩니다. 논문이라고 생각하시면 됩니다. 엔터티는 목차이고 아키텍처는 내용입니다. 이 엔터티에 대한 아키텍처를 만들어 보겠습니다.

architecture rtl of example_and is signal and_gate : std_logic; begin and_gate <= input_1 and input_2; and_result <= and_gate; end rtl;

위의 코드는 example_and 엔터티의 rtl이라는 아키텍처를 정의합니다. 아키텍처에서 사용하는 모든 신호는 "is"와 "begin" 키워드 사이에 정의되어야 합니다. 실제 아키텍처 논리는 "시작"과 "끝" 키워드 사이에 있습니다. 이 파일은 거의 완료되었습니다. 도구에 마지막으로 알려야 할 사항은 사용할 라이브러리입니다. 라이브러리는 특정 키워드가 파일에서 작동하는 방식을 정의합니다. 지금은 파일 상단에 다음 두 줄이 있어야 한다는 사실을 당연하게 생각하십시오.

library ieee; use ieee.std_logic_1164.all;

축하합니다! 첫 번째 VHDL 파일을 만들었습니다. 완성된 파일은 여기에서 볼 수 있습니다:

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

바보 같은 게이트를 만들기 위해 많은 코드를 작성해야 했던 것 같습니까? 우선, 게이트는 바보가 아닙니다. 둘째, 당신이 옳습니다. VHDL은 매우 장황한 언어입니다. 소프트웨어에서 매우 쉬운 작업을 수행하면 Verilog 또는 VHDL과 같은 HDL에서 훨씬 더 오래 걸린다는 사실에 익숙해지십시오. 그러나 일부 소프트웨어 담당자에게 Conway의 Game of Life를 표시하는 VGA 모니터에 이미지를 생성해 달라고 하고 그들의 머리가 빙글빙글 돌아가는 것을 지켜보세요! 그건 그렇고, 그 비디오는 VHDL과 FPGA로 생성됩니다. 당신은 곧 그렇게 할 수 있을 것입니다!

VHDL

Arduino 자습서 시리즈의 일곱 번째 Arduino 자습서에 오신 것을 환영합니다. 이 튜토리얼에서는 Arduino를 Matlab에 연결하는 방법과 직렬 포트를 사용하여 통신하는 방법을 배웁니다. 또한 Matlab을 사용하여 Arduino Board를 제어하는 예를 만들 것입니다. 이것은 따라하기 쉬운 단계별 비디오 자습서입니다. 또한 동영상 아래에서 이 튜토리얼에 필요한 부분과 동영상의 예제 소스 코드를 찾을 수 있습니다. 이 Arduino 튜토리얼에 필요한 구성요소 아두이노 보드 ..................

소개 안녕하세요 여러분, 저는 Strton 런타임과 IEC61850 표준 주변의 프로그래밍 환경에 대해 이야기하겠습니다. 이 런타임은 에너지 분야에서 완전히 진화한 프로토콜인 표준 에디션 2를 따릅니다. 과거에 피닉스컨택트는 PCWORX용 IEC61850 스택과 이전 PLC 제품군(AXC1050)을 개발했지만 오늘날에는 매장에서 사용할 수 있는 이 애플리케이션 덕분에 PLCNextEngineer와 IEC61850 표준을 결합할 수 있습니다. 또한 이 런타임은 61850 클라이언트를 구성할 수 있는 큰 이점을 제공