VHDL

이 가이드에서는 통합 논리 분석기(ILA) 사용에 대해 설명합니다. 및 가상 입력/출력(VIO) Xilinx Vivado IDE에서 VHDL 설계를 디버그 및 모니터링하기 위한 코어.

많은 경우 설계자는 온칩 검증을 수행해야 합니다. 즉, 검증 목적으로 FPGA 설계에서 내부 신호의 동작에 액세스하는 것입니다.

한 가지 옵션은 이러한 신호를 FPGA 핀으로 가져와 LED에 연결하여 시각적으로 동작을 확인하는 것입니다. 이 옵션은 쉽고 빠르며 간단한 경우에 잘 작동하지만 유연하거나 확장 가능하거나 현실적이지 않습니다.

또 다른 옵션은 이러한 신호의 동작을 표시하고 설명할 수 있는 고급 기능을 갖춘 외부 로직 분석기를 사용하는 것입니다. 그러나 이를 위해서는 비교적 고가의 외부 장비가 필요합니다.

통합 논리 분석기(ILA)는 이전 두 옵션의 장점을 결합한 대안입니다. 쉽고 빠르며 유연하며 설계자가 선택한 신호의 동작을 빠르게 보고 확인할 수 있는 많은 고급 기능이 있습니다.

이 기사에는 Vivado GUI의 여러 스크린샷이 포함되어 있습니다. 이미지를 클릭하면 커집니다!

사이드바를 사용하여 개요 탐색 이 자습서의 경우 아래로 스크롤하고 모바일 장치를 사용하는 경우 오른쪽 상단 모서리에 있는 팝업 탐색 버튼을 클릭합니다.

ILA 및 VIO는 Xilinx에서 무료로 사용자 지정할 수 있는 IP입니다. ILA IP를 사용하면 FPGA 내부의 내부 신호를 쉽게 조사하고 시뮬레이션과 같은 환경으로 가져와 이를 모니터링하고 동작을 확인할 수 있습니다.

ILA와 달리 VIO IP를 사용하면 FPGA 내부의 내부 신호를 가상으로 구동하여 RESET 신호 구동과 같은 설계를 자극하거나 제어할 수 있습니다.

저는 Kintex-7 FPGA KC705 평가 키트를 사용하고 있지만 이 튜토리얼에 표시된 방법은 모든 최신 Xilinx FPGA 보드에서 작동해야 합니다.

아래 양식을 사용하여 예제 프로젝트와 VHDL 코드를 다운로드할 수 있습니다. Vivado 버전 2020.2 이상에서 작동해야 합니다.

Zip 압축을 풀고 ila_tutorial.xpr을 엽니다. Vivado의 파일을 클릭하여 예제 디자인을 보거나 이 기사의 나머지 부분을 읽고 처음부터 만드는 방법을 배우십시오.

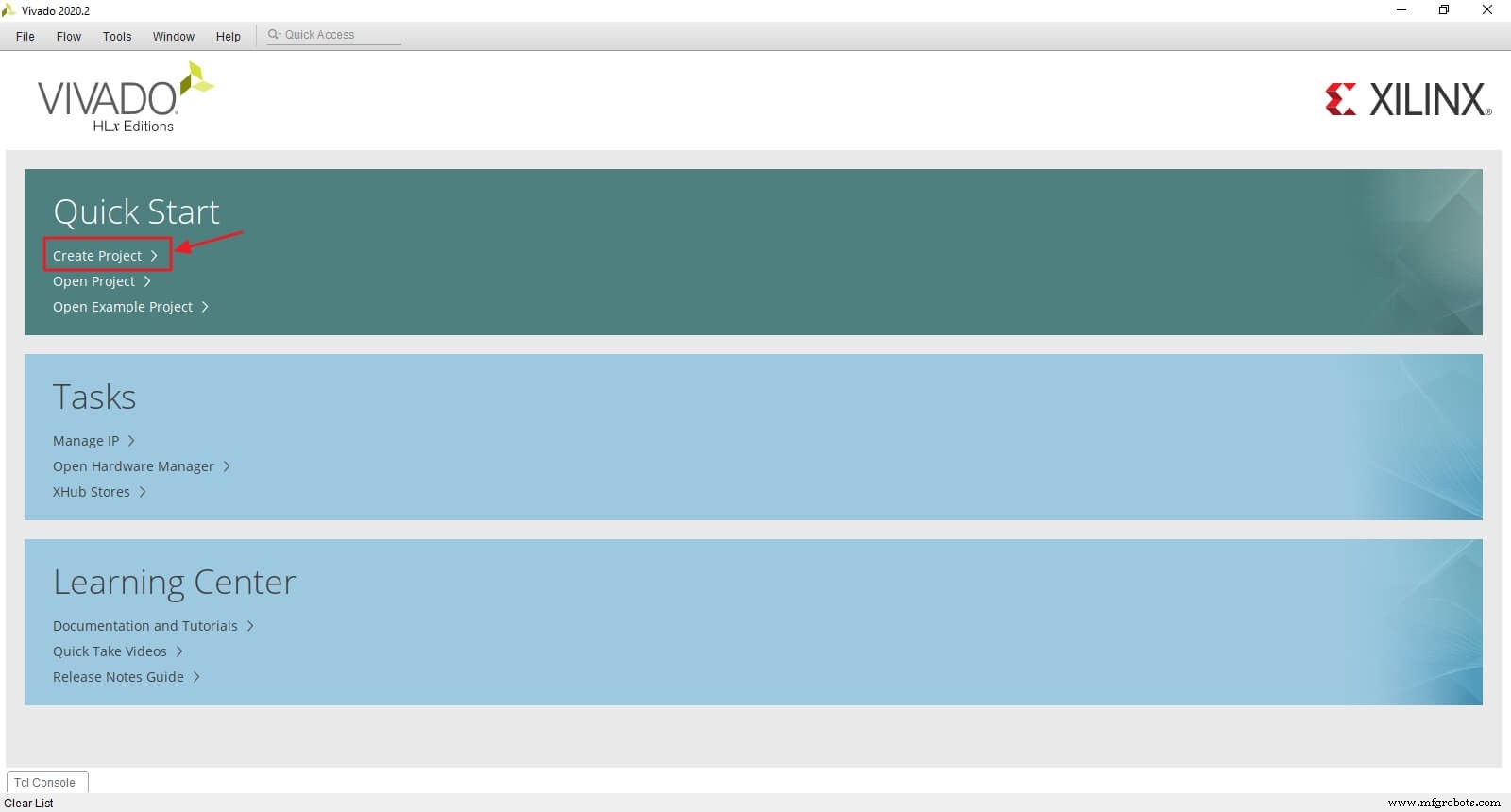

Vivado를 열어 시작하십시오. Vivado의 시작 화면에서 프로젝트 만들기를 클릭합니다. 버튼.

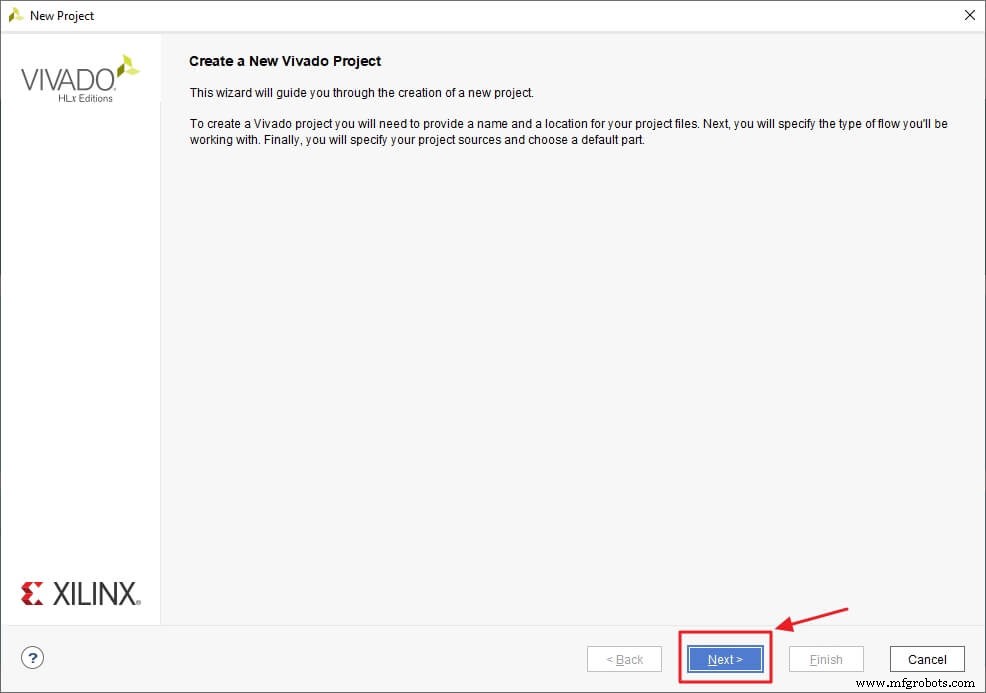

다음 을 클릭하십시오. 계속합니다.

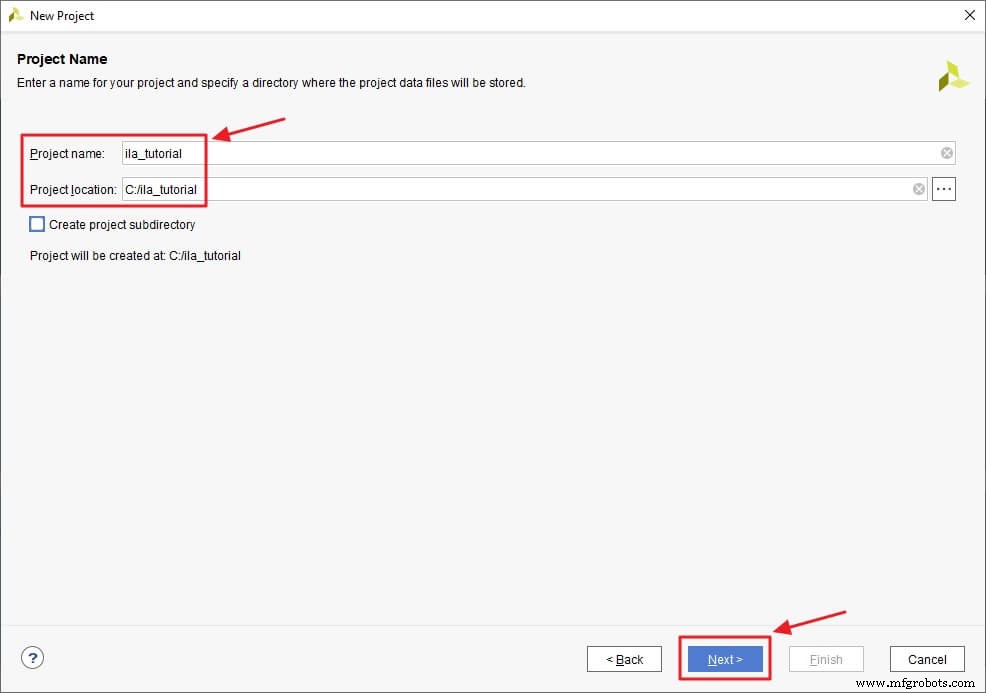

프로젝트 이름을 ila_tutorial으로 변경 다음을 클릭합니다.

참고: 프로젝트 이름에 공백을 사용하지 마십시오. 대신 밑줄이나 대시를 사용하세요.

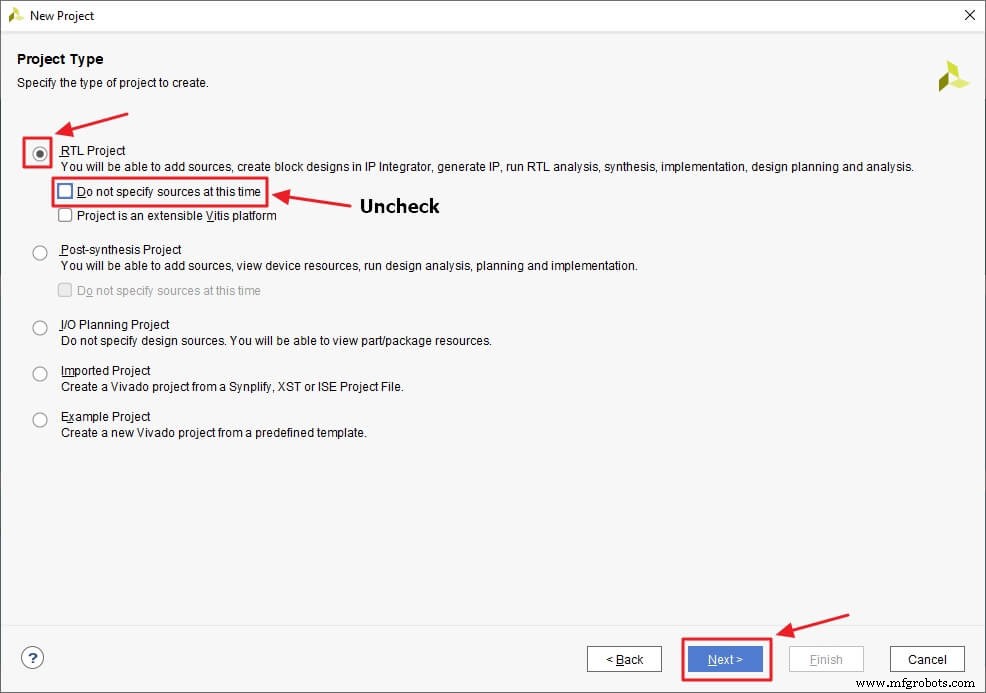

RTL 프로젝트 선택 지금은 출처를 지정하지 않음을 선택 취소합니다. 다음 을 클릭하십시오. 계속합니다.

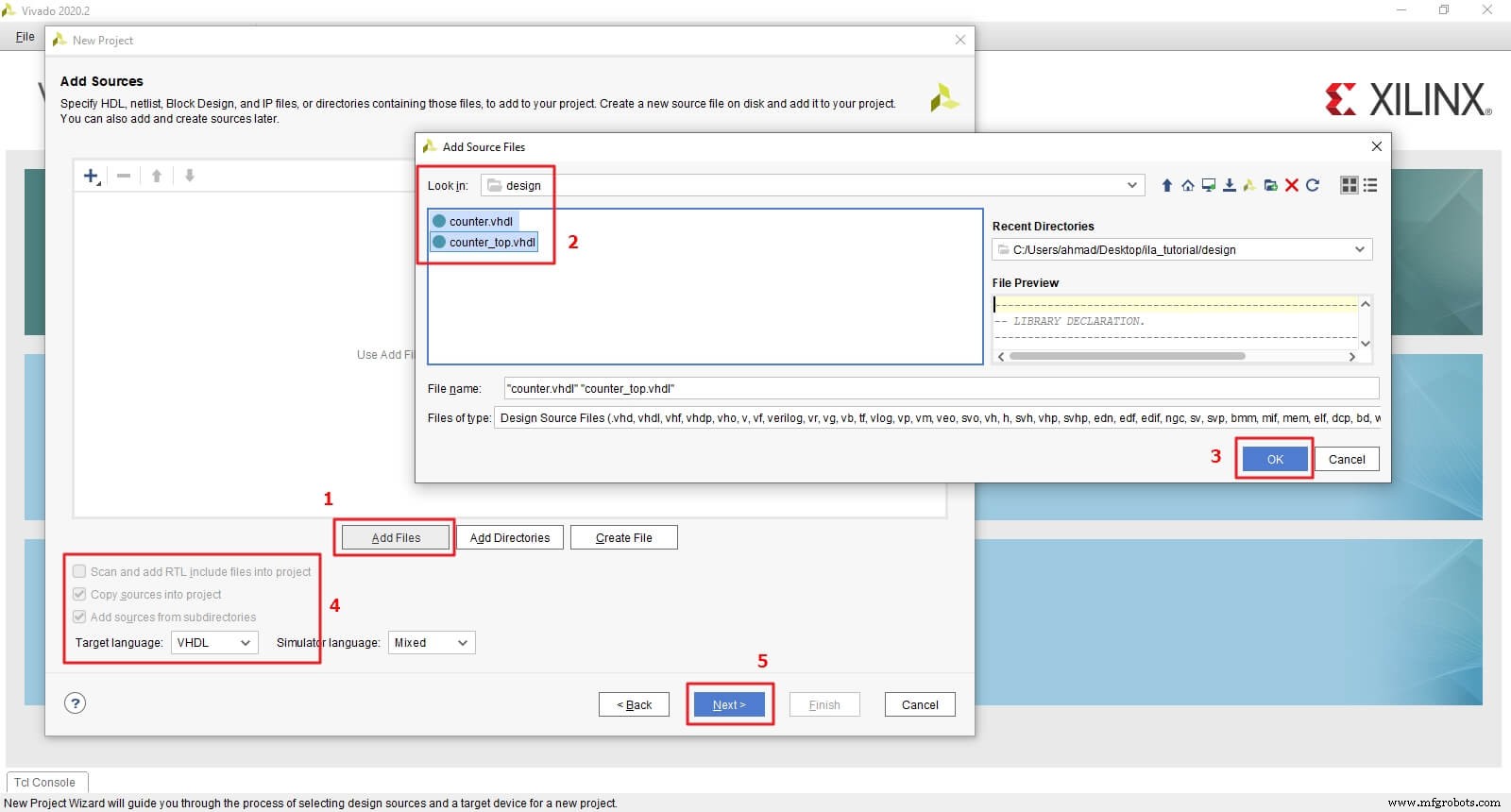

소스 파일을 추가하십시오. counter.vhdl 및 counter_top.vhdl 디자인 폴더에서 VHDL 선택 대상 언어에 대한. 프로젝트에 소스 복사를 선택합니다. 다음 을 클릭하십시오. 계속합니다.

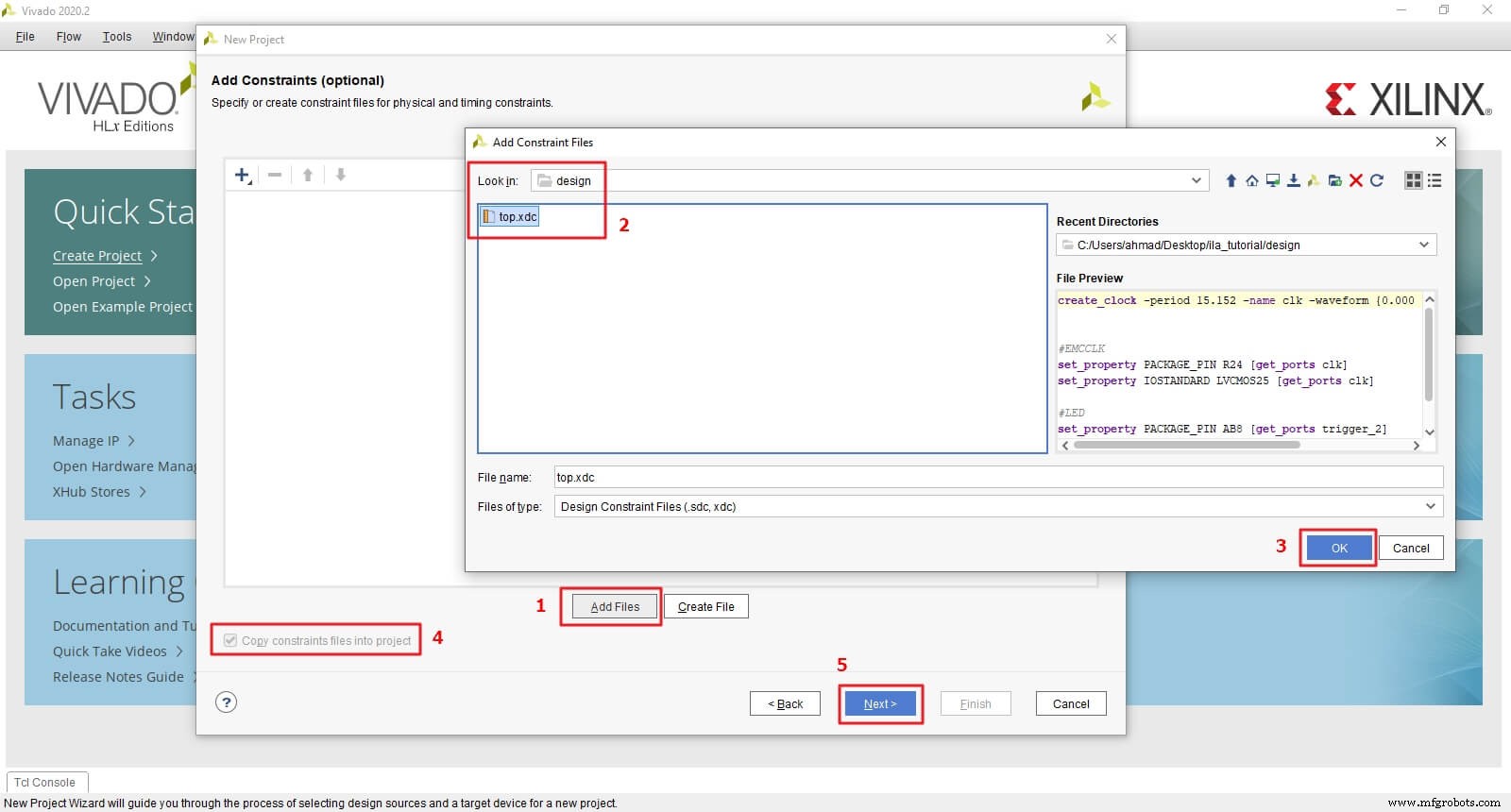

제약 조건 파일 top.xdc 추가 디자인 폴더에서 제약 파일을 프로젝트에 복사 를 선택하십시오. 다음 을 클릭하십시오. 계속합니다.

참고: 이 제약 파일은 KC705 보드에만 해당됩니다. clk 핀을 변경해야 합니다. 및 LED 핀 당신의 보드에 따라. 또한 -마침표 당신의 보드 시계.

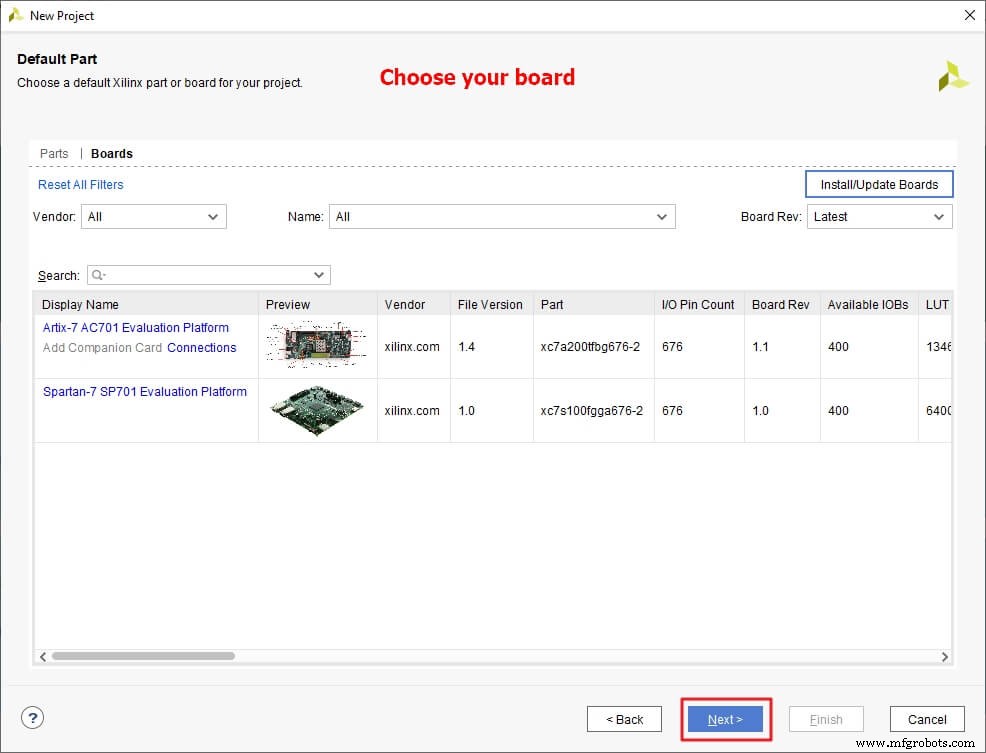

보드를 검색하고 목록에서 선택하십시오. 다음 을 클릭하십시오. 계속합니다.

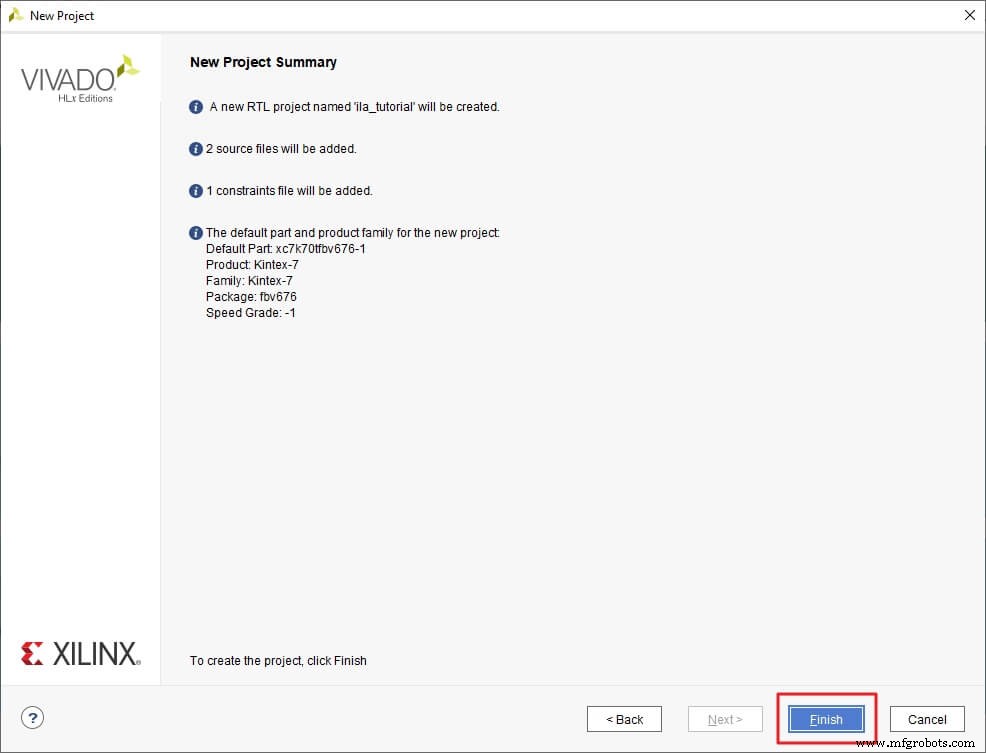

New Project 마법사의 마지막 화면입니다. 마침 을 클릭하십시오. 프로젝트를 여세요.

이 자습서에서는 간단한 두 카운터 체인 예제를 사용합니다.

counter.vhdl 파일에는 활성화된 경우 0에서 15까지 계산되는 간단한 4비트 카운터에 대한 RTL 코드가 포함되어 있습니다. 카운트가 12와 15 사이일 때 1비트 출력을 주장합니다. 다른 모든 값의 경우 출력은 낮은 '0'으로 유지됩니다. .

다음은 카운터 모듈의 엔티티 인터페이스입니다.

----------------------------------------------------------------------------

-- ENTITY DECLARATION.

----------------------------------------------------------------------------

ENTITY counter IS

PORT(clk : IN STD_LOGIC; -- Main clock

reset : IN STD_LOGIC; -- reset, active_high

enable : IN STD_LOGIC; -- enable the next counter

trigger : OUT STD_LOGIC -- trigger the next counter

);

END ENTITY;

카운터 디자인에는 두 가지 내부 신호가 있습니다. count 및 trigger_o .

– 카운트 계산 기능을 구현하는 데 사용됩니다.

– 및 trigger_o 출력 포트 트리거를 연결하기 위한 중간 신호입니다. .

ATTRIBUTE에 대해 걱정하지 마세요. , 나중에 설명하겠습니다.

----------------------------------------------------------------------------

-- ARCHITECTURE DECLARATION.

----------------------------------------------------------------------------

ARCHITECTURE rtl OF counter IS

-- INTERNAL SIGNALS DECLARATION --

SIGNAL count : UNSIGNED(3 DOWNTO 0) := (OTHERS => '0');

SIGNAL trigger_o : STD_LOGIC := '0';

-- ATTRIBUTE DECLARATION --

ATTRIBUTE MARK_DEBUG : STRING;

ATTRIBUTE MARK_DEBUG OF count : SIGNAL IS "true";

아래 목록에서 카운터에 대한 구현을 볼 수 있습니다. seq_proc 프로세스는 입력 포트 clk 의 상승 에지에서 트리거됩니다. 입력 포트가 재설정 되면 재설정 모드에 있습니다. 높은 '1'입니다.

수 신호는 입력 포트가 활성화 일 때 증가합니다. 높은 '1'이고 trigger_o 신호 count 값이 높을 때 신호가 높게 표시됩니다. 12에서 15 사이입니다.

seq_proc: PROCESS (reset, clk)

BEGIN -- for seq_proc

IF (reset = '1') THEN

count <= (OTHERS => '0');

trigger_o <= '0';

ELSIF rising_edge(clk) THEN

IF (enable = '1') THEN

count <= count + 1;

IF (count > x"B" AND count <= x"F") THEN

trigger_o <= '1';

ELSE

trigger_o <= '0';

END IF;

END IF;

END IF;

END PROCESS;

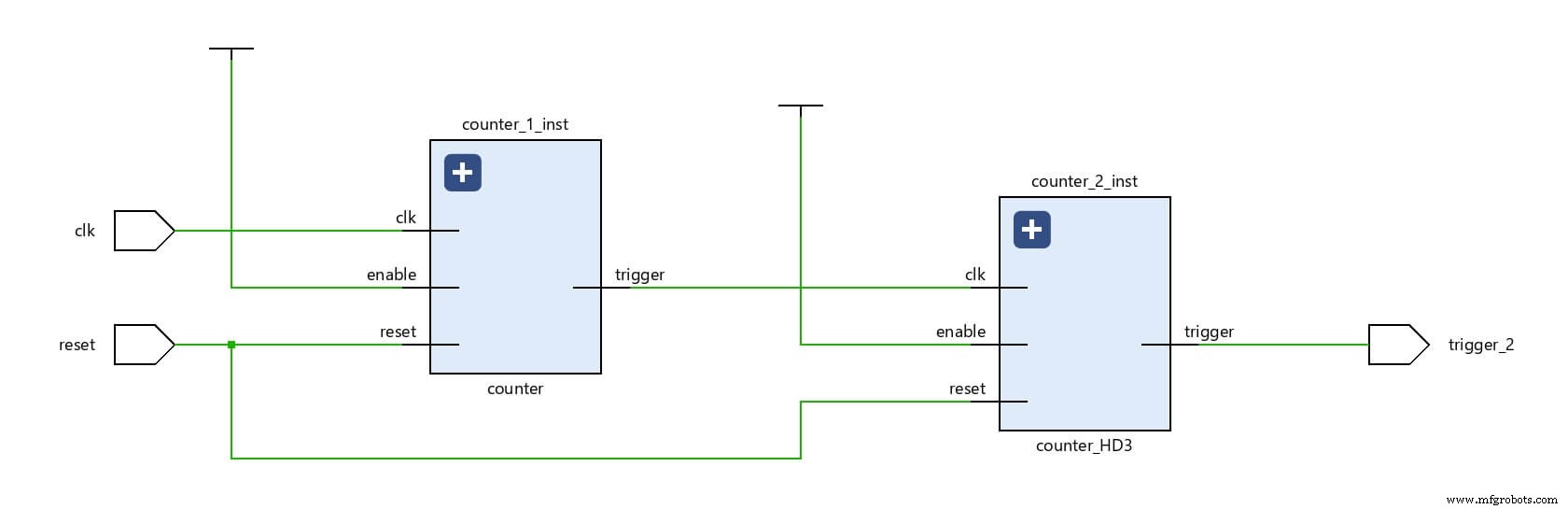

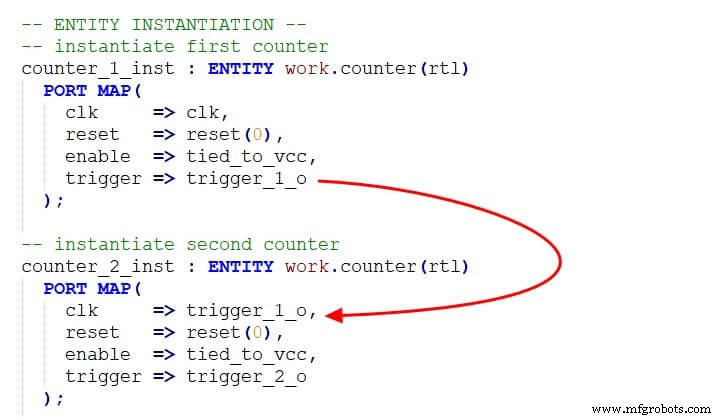

counter_top.vhdl 파일 순차적으로 연결된 카운터의 두 인스턴스를 포함합니다.

– counter_1_inst 항상 활성화되어 있으며 counter_2_inst 시계 . 즉, 출력 포트는 트리거 counter_1_inst 의 입력 포트에 연결되어 있습니다. clk counter_2_inst의 .

– 결과 동작은 counter_1_inst counter_2_inst 활성화 16개 클럭 사이클 중 4개만. 따라서 counter_2_inst 16번 카운트할 때마다 카운터가 4번 증가합니다.

이제 디자인 예제를 이해했으므로 입력 포트 재설정을 제어하는 VIO를 만듭니다. . 그러면 Vivado IDE에서 재설정을 조작(토글)할 수 있으므로 카운터를 시작/중지할 시기를 수동으로 제어할 수 있습니다.

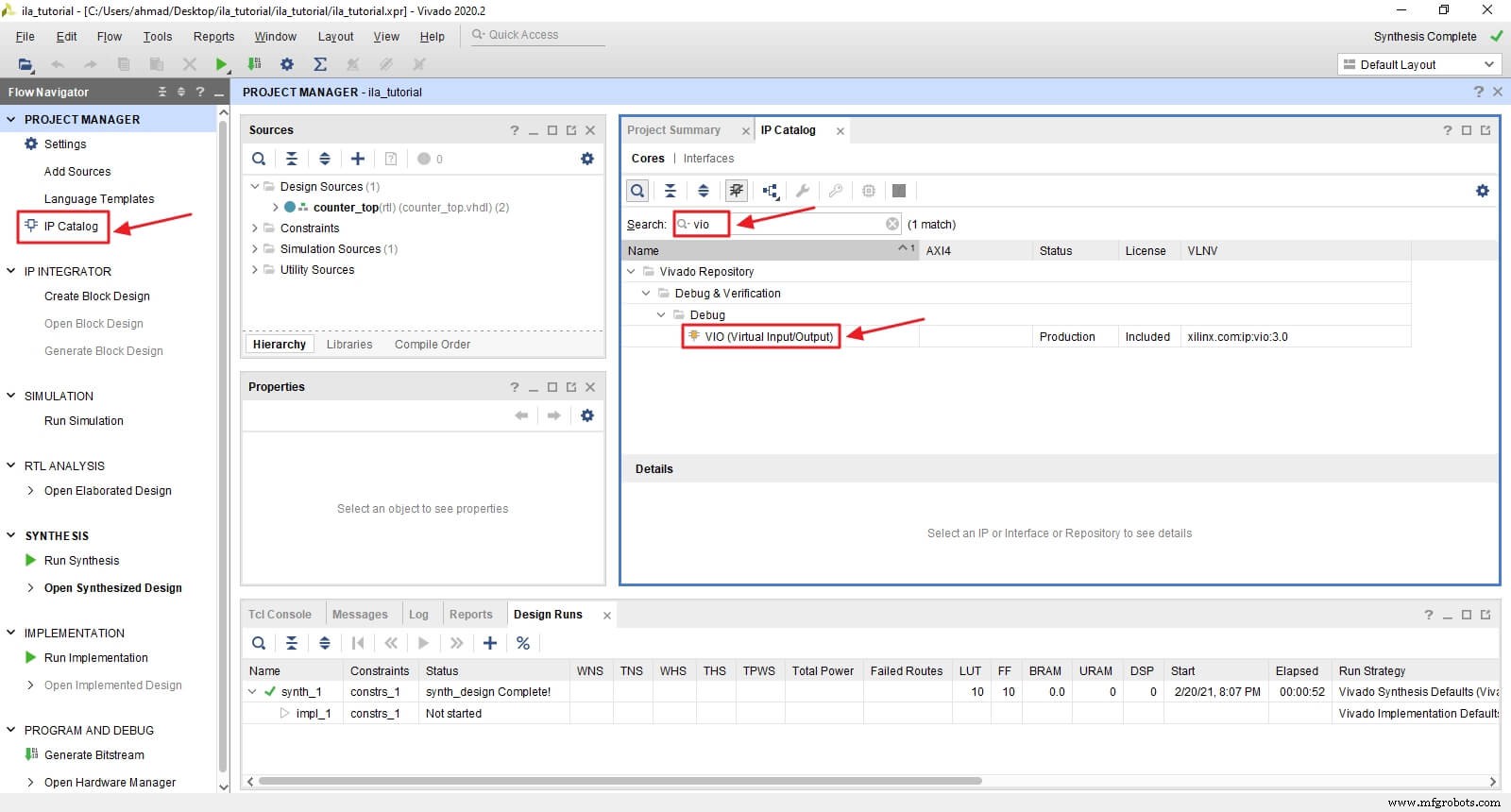

IP 카탈로그를 클릭합니다. , VIO 검색 을 클릭한 다음 VIO(가상 입력/출력)를 두 번 클릭합니다. .

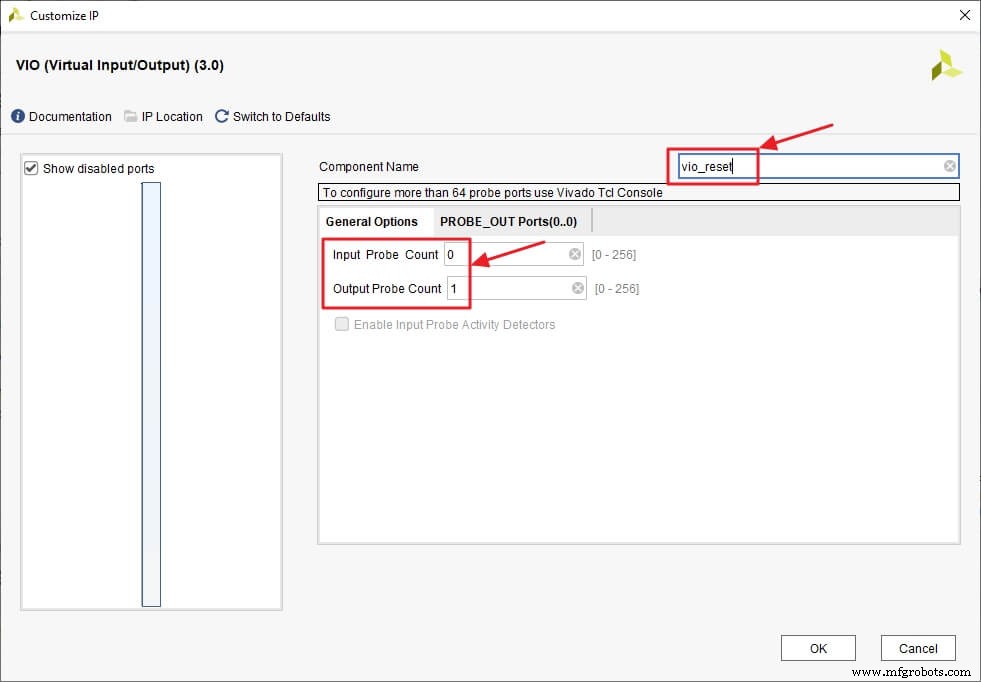

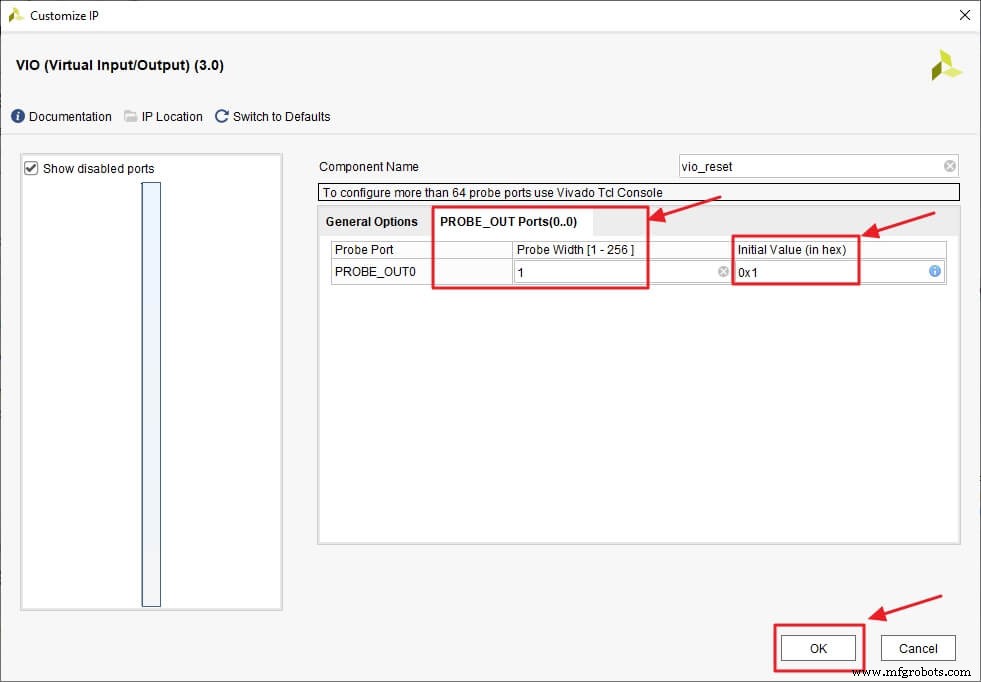

먼저 이름을 vio_reset으로 변경합니다. .

둘째, 재설정을 위한 출력 포트만 필요하므로 입력 프로브 카운트 상자에 0을 입력합니다. 출력 프로브 카운트 상자에 1을 입력합니다. .

PROBE_OUT을 클릭합니다. 포트 탭. 재설정은 1비트 신호이므로 probe_width 상자에 1을 입력하고 또한 초기 값 상자에 0x1을 입력합니다. 따라서 높은 '1'로 시작합니다. 그런 다음 확인을 클릭합니다. 및 생성 . 이제 Vivado가 VIO 합성을 시작합니다.

Vivado가 VIO 합성을 완료한 후에는 구성 요소를 선언하고 counter_top.vhdl에서 인스턴스화하여 디자인에 추가해야 합니다. 파일은 아래와 같습니다.

먼저 vio_reset에 대한 구성요소 선언을 추가합니다. counter_top.vhdl의 구성요소 선언 섹션에서 파일.

-- Declare vio_reset

COMPONENT vio_reset

PORT(

clk : IN STD_LOGIC;

probe_out0 : OUT STD_LOGIC_VECTOR(0 DOWNTO 0)

);

END COMPONENT;

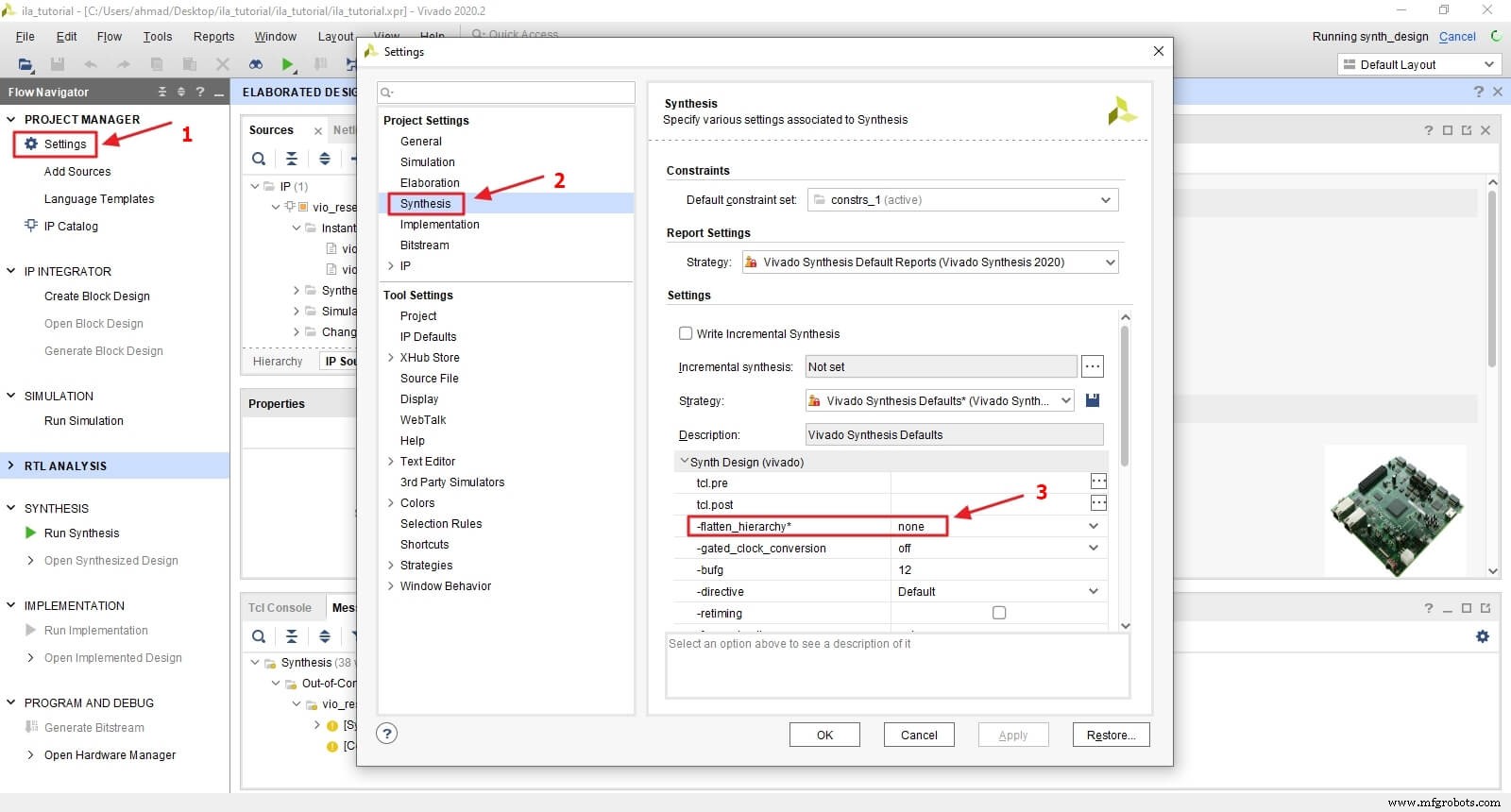

이제 VIO가 완료되었으며 디자인을 합성할 준비가 되었습니다. 하지만 그 전에 합성 설정을 변경해야 합니다. flatten_hierarchy 없음으로 .

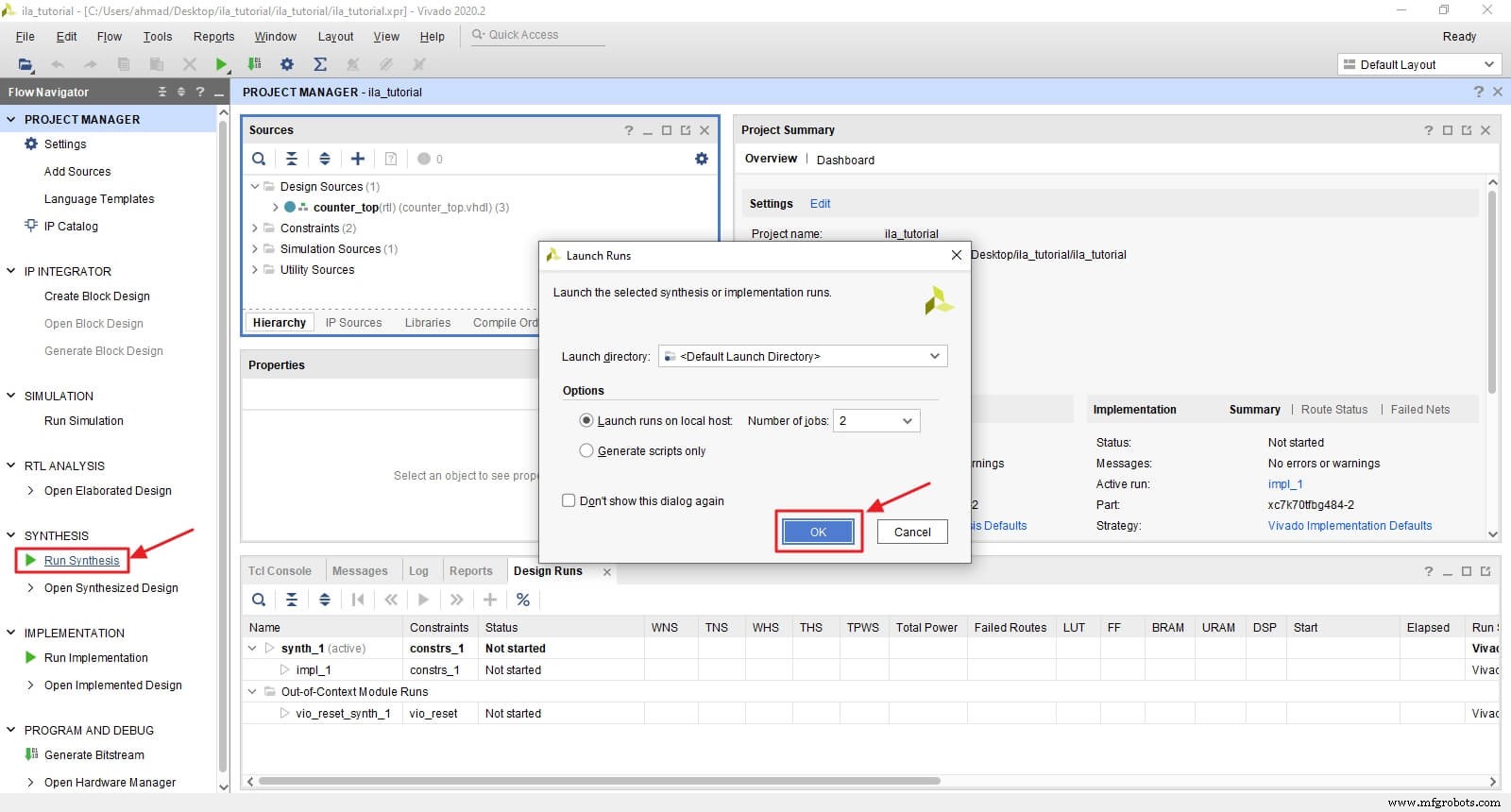

합성 실행 을 클릭하십시오. 그런 다음 확인에서 .

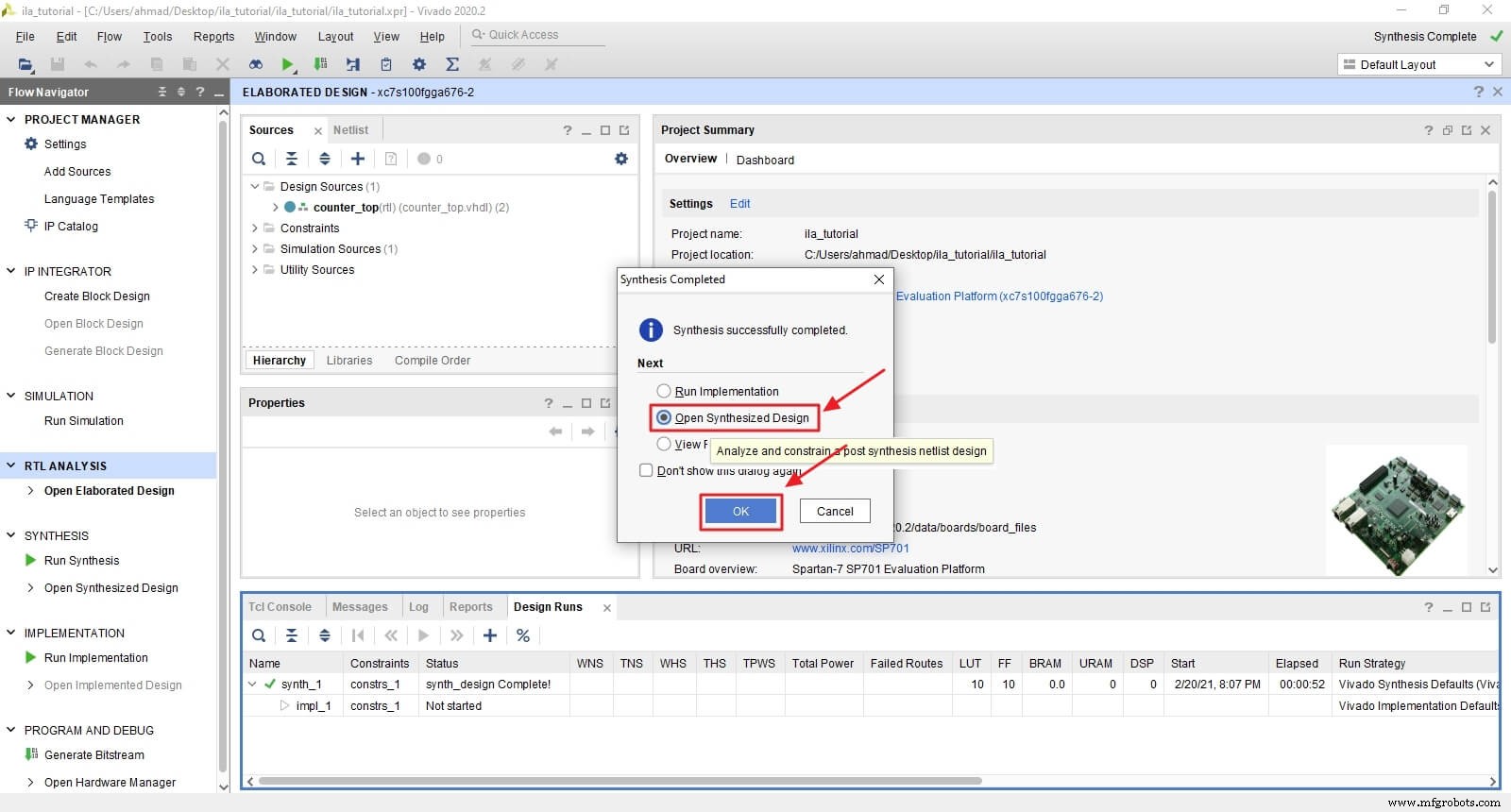

Vivado가 합성을 완료하면 합성된 디자인 열기를 클릭합니다. .

레이아웃을 디버그 로 변경 레이아웃 을 클릭하여 그런 다음 디버그 .

합성된 디자인에는 이제 vio_reset이 포함됩니다. 이제 우리가 조사하려는 신호를 지정할 시간입니다. 세 가지 방법이 있습니다.

처음 두 가지 방법을 사용하고 세 번째 방법은 나중 자습서를 위해 남겨 둡니다.

이 방법은 특히 복합 유형(배열 또는 레코드)인 경우 프로브를 삽입하는 가장 쉽고 빠른 방법입니다. 그러나 실제 제품에서 중복되는 VHDL 코드인 디자인 파일에 코드를 추가해야 합니다.

다음과 같이 VHDL 설계 파일에 프로브를 삽입할 수 있습니다.

-- ATTRIBUTE DECLARATION --

ATTRIBUTE MARK_DEBUG : STRING;

ATTRIBUTE MARK_DEBUG OF count : SIGNAL IS "true";

참고: 각 VHDL 디자인 파일에서 속성을 한 번만 선언하면 여러 신호에 연결할 수 있습니다.

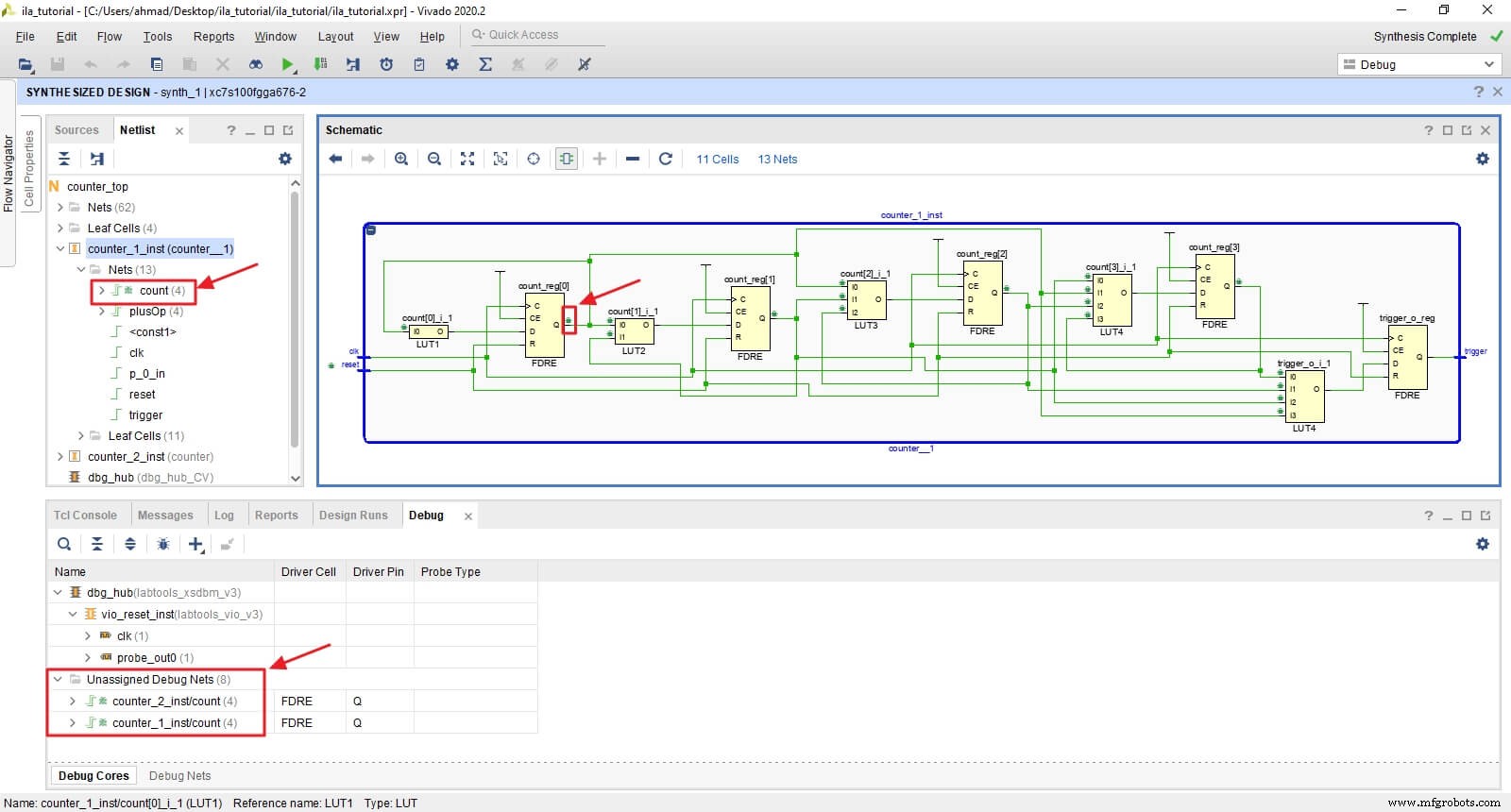

합성된 디자인에서 신호가 카운트한다는 것을 알 수 있습니다. counter_1_inst 모두에서 및 counter_2_inst 할당되지 않은 디버그 네트 아래에 나열됩니다. Netlist 및 도식 .

이 삽입 방법도 쉽지만 먼저 디자인을 합성한 다음 디버깅을 위해 표시하기 위해 각 신호를 수동으로 클릭해야 합니다. 디자인이 크고 많은 신호를 모니터링하려는 경우 지칠 수 있습니다.

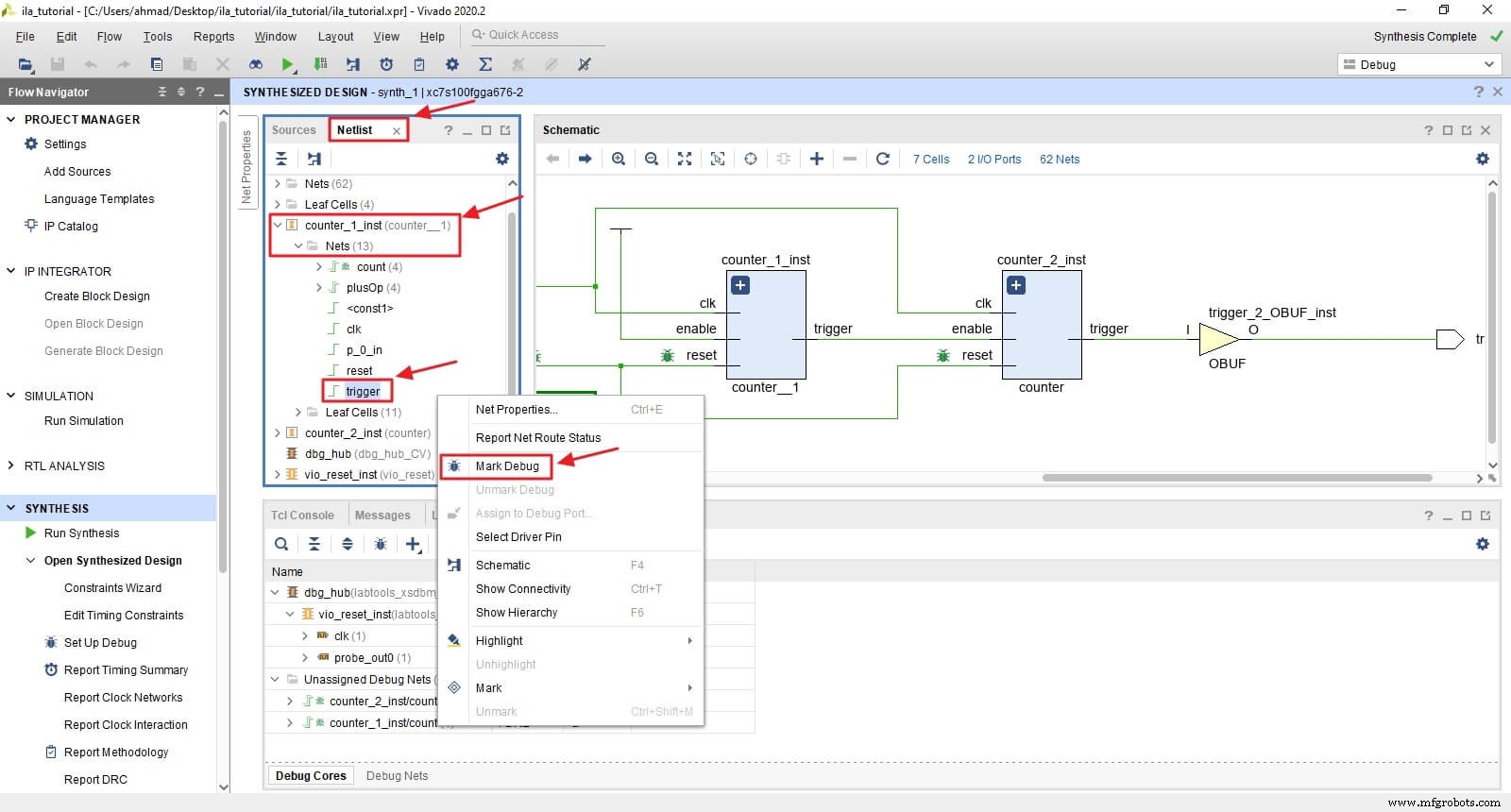

출력 포트 트리거를 조사합니다. Netlist를 사용하는 두 카운터 모두에서 . Netlist 창에서 이 작업을 수행할 수 있습니다. 또는 도식 신호망을 찾은 다음 오른쪽 클릭 여기에서 디버그 표시를 선택합니다. .

Netlist 창에서 트리거를 찾습니다. counter_1_inst → Nets → 아래 트리거 . 그런 다음 마우스 오른쪽 버튼으로 클릭하고 디버그 표시를 선택합니다. .

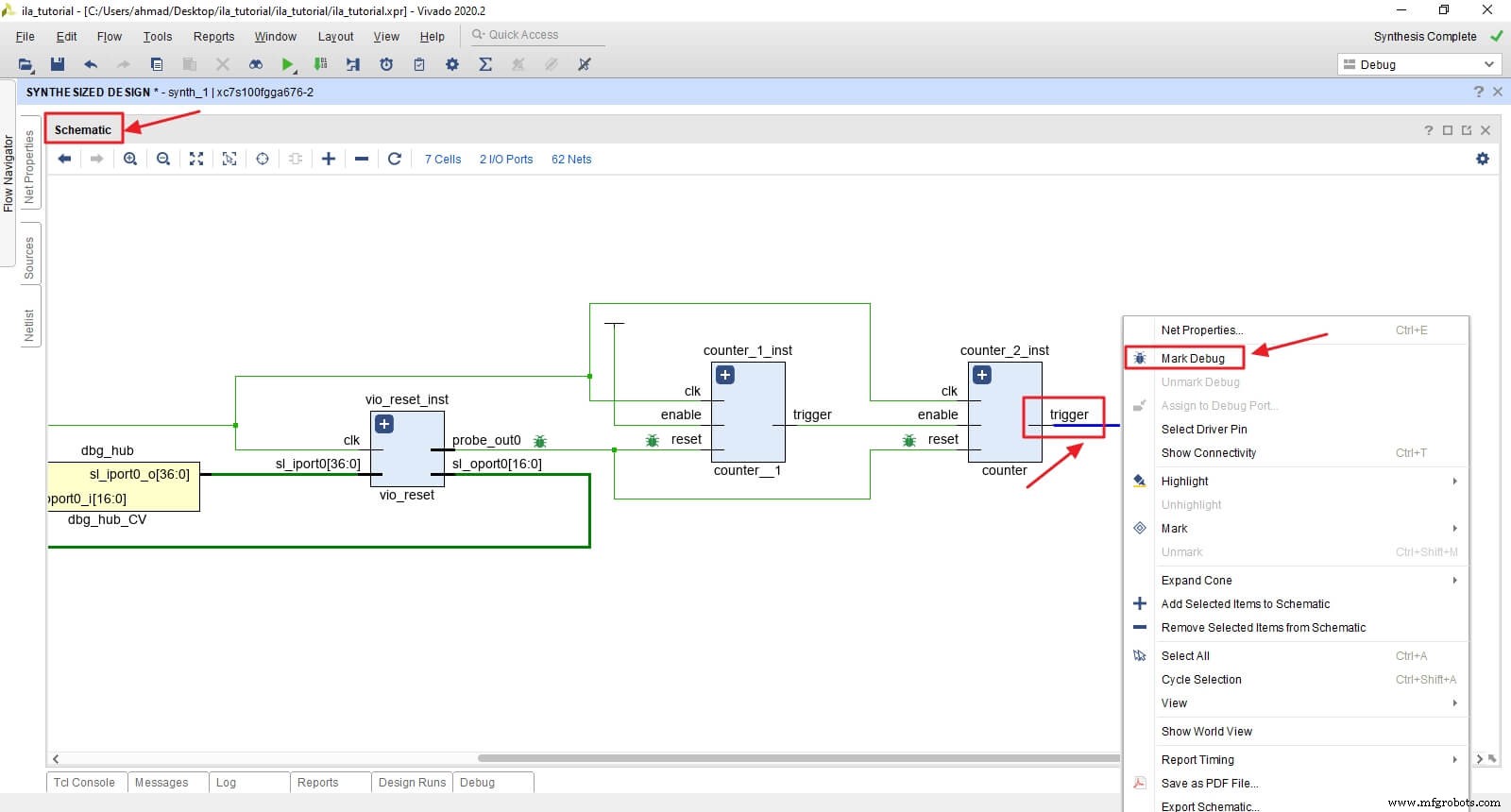

회로도 창에서 트리거를 찾습니다. counter_2_inst의 출력 . 그런 다음 마우스 오른쪽 버튼으로 클릭하고 디버그 표시를 선택합니다. .

이제 할당되지 않은 디버그 네트 아래에 나열되는 것을 볼 수 있습니다. .

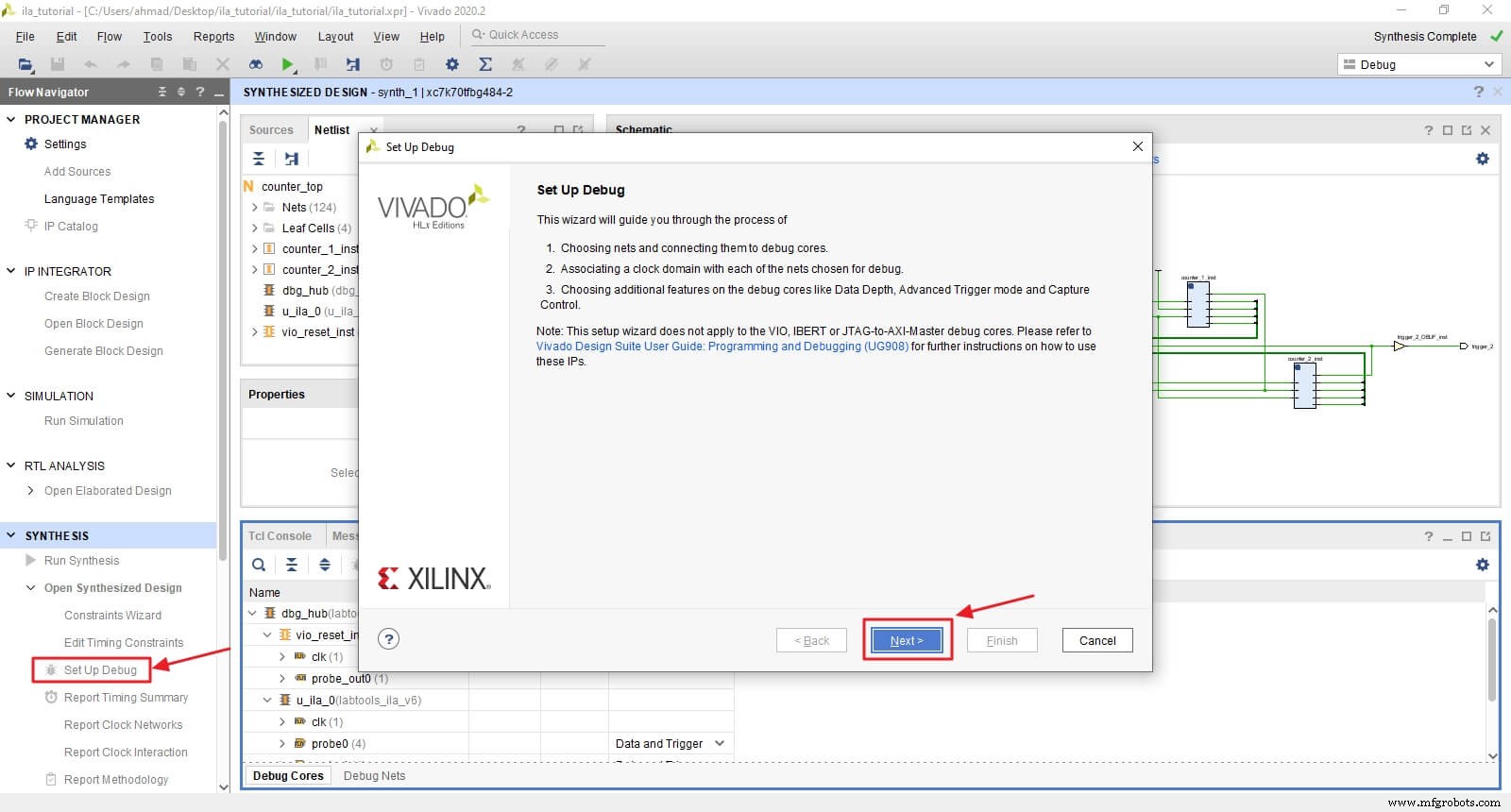

이제 ILA 디버그 코어를 만들 차례입니다. 분석하려는 각 신호에 대한 프로브를 생성해야 합니다. 가장 쉬운 방법은 Vivado 마법사 디버그 설정을 활용하는 것입니다. .

디버그 설정을 클릭합니다. 다음을 클릭합니다. .

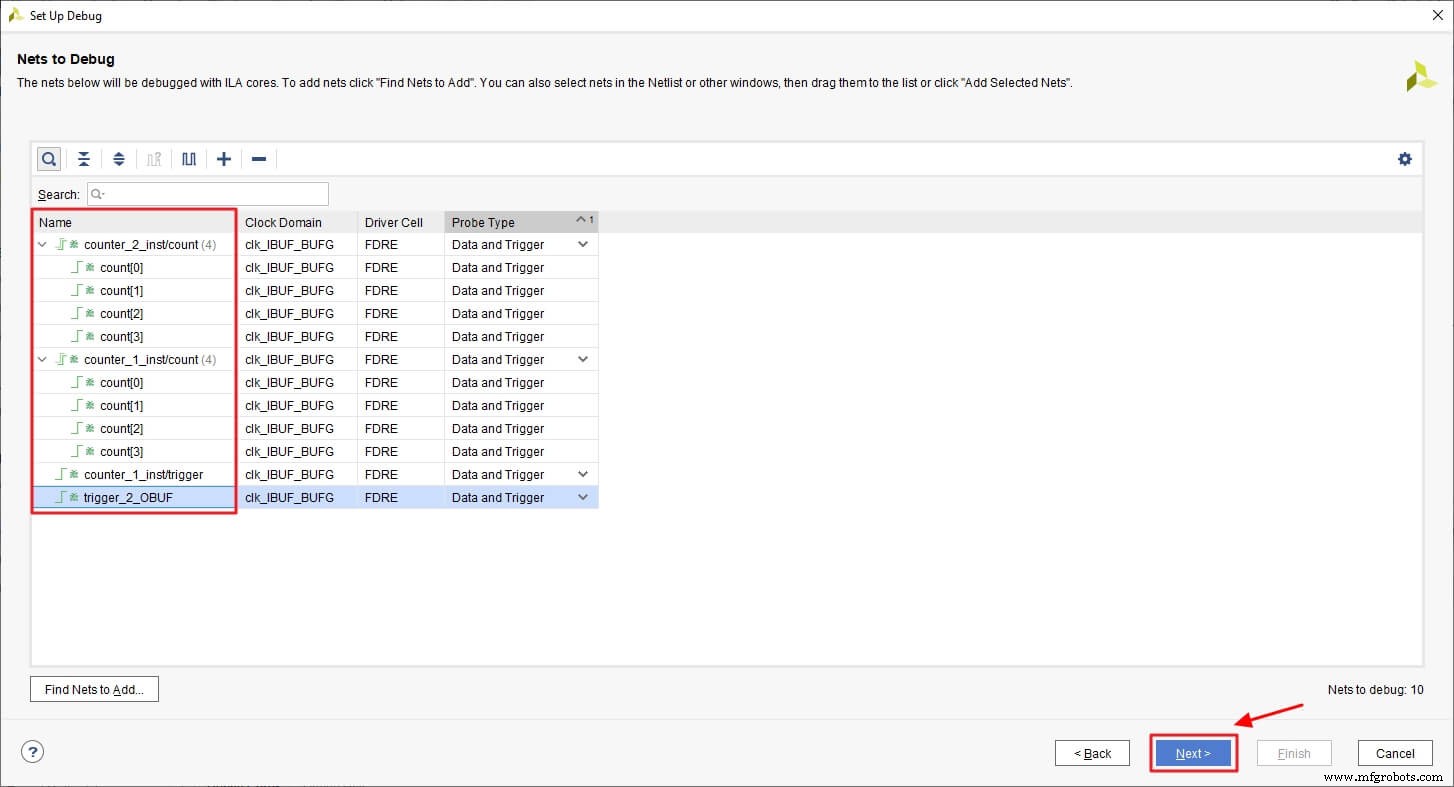

Vivado는 모든 디버그 신호를 나열하고 자동으로 클럭 도메인을 캡처합니다. 여기에서 4개의 신호가 나열되어 있음을 알 수 있습니다. 관심이 없는 신호를 제거하거나 추가 신호를 추가할 수 있지만 모두 사용합니다.

참고: 디버그로 표시한 모든 신호를 사용할 필요는 없습니다.

다음을 클릭합니다. .

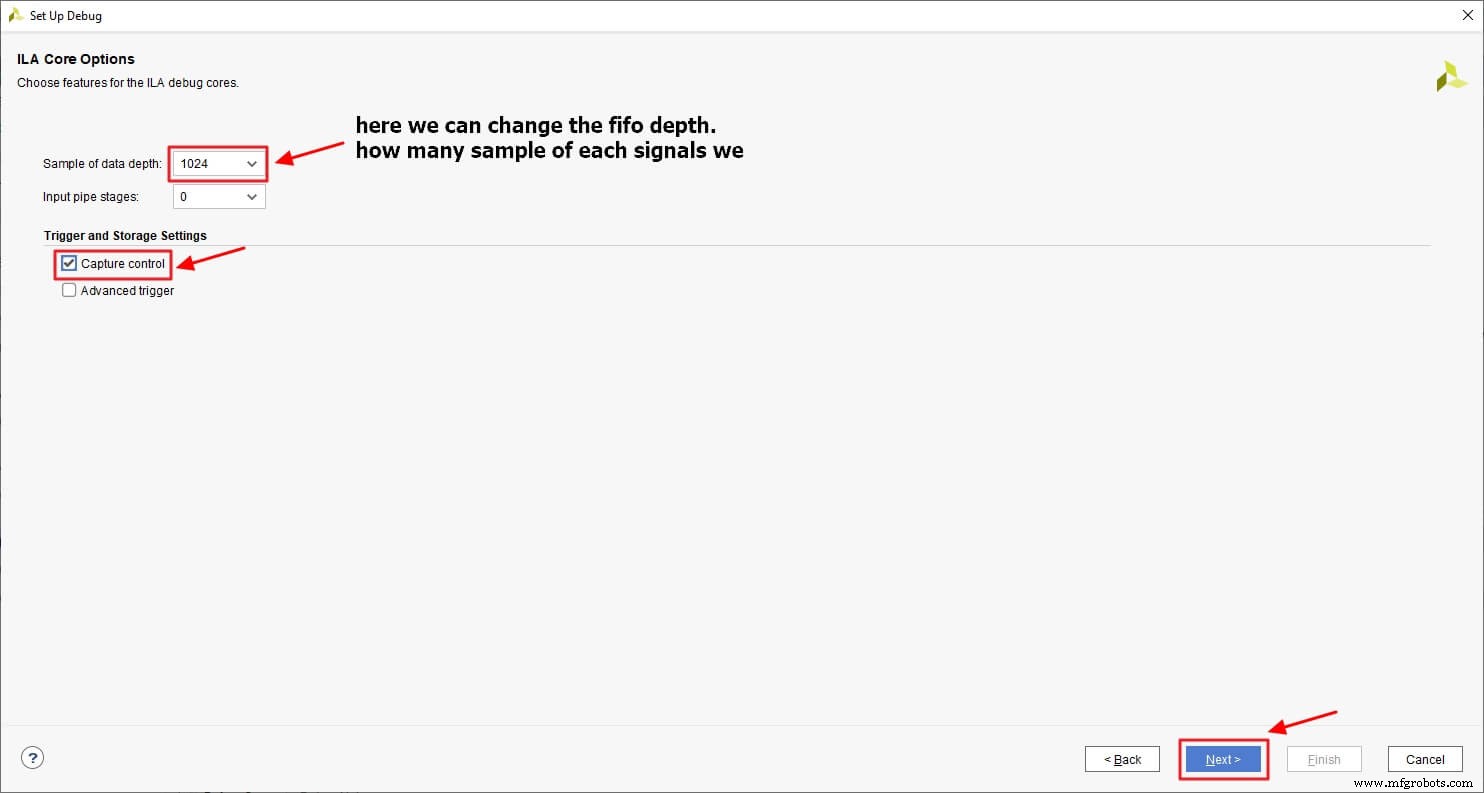

이제 FIFO 깊이를 선택하여 ILA를 구성합니다. 캡처 제어 확인 . FIFO는 이 예에서 충분한 깊이이므로 1024로 둘 수 있습니다.

다음을 클릭합니다. .

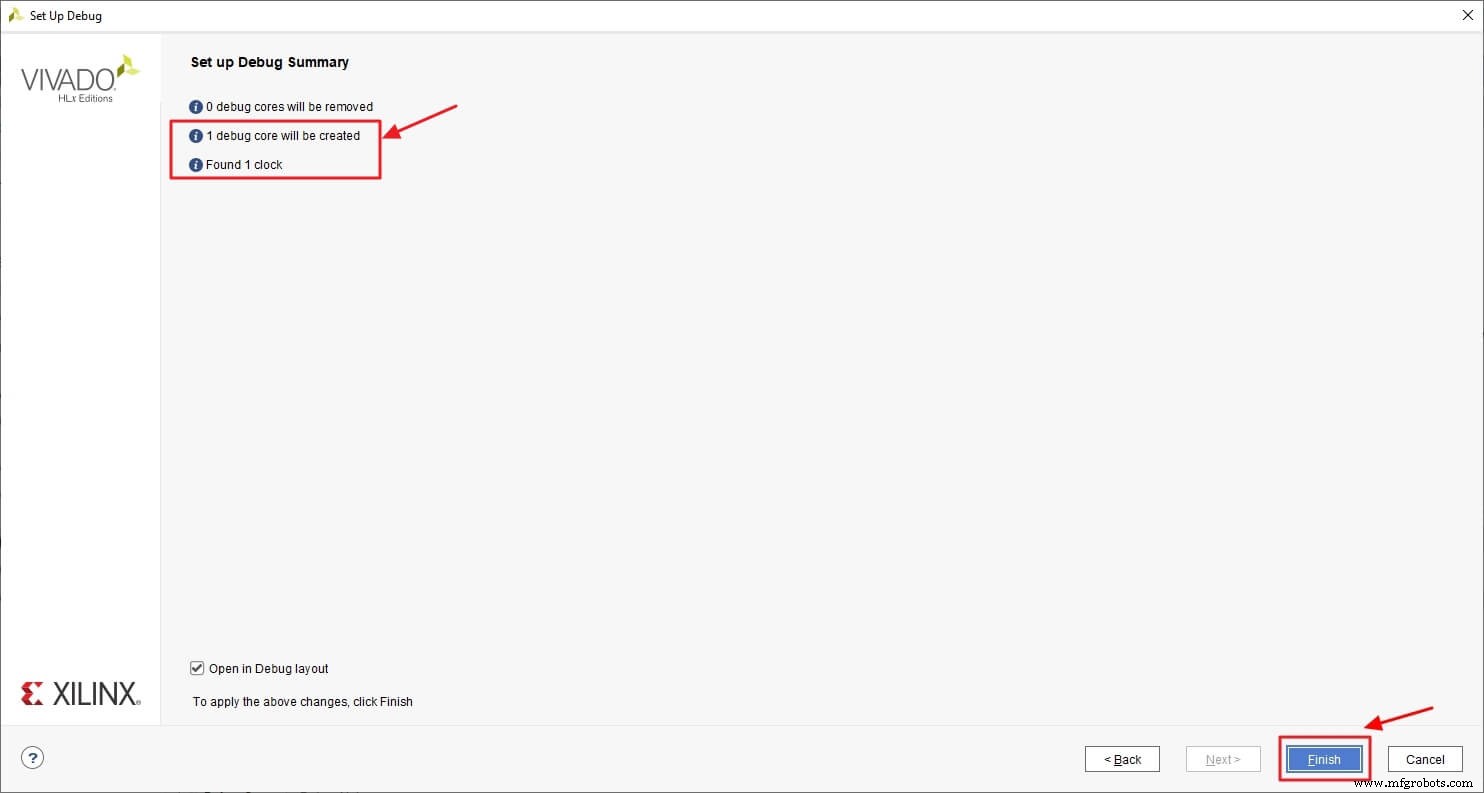

이제 우리는 Vivado가 하나의 클럭을 찾았고 하나의 디버그 코어를 생성한다는 것을 알았습니다.

마침을 클릭합니다. .

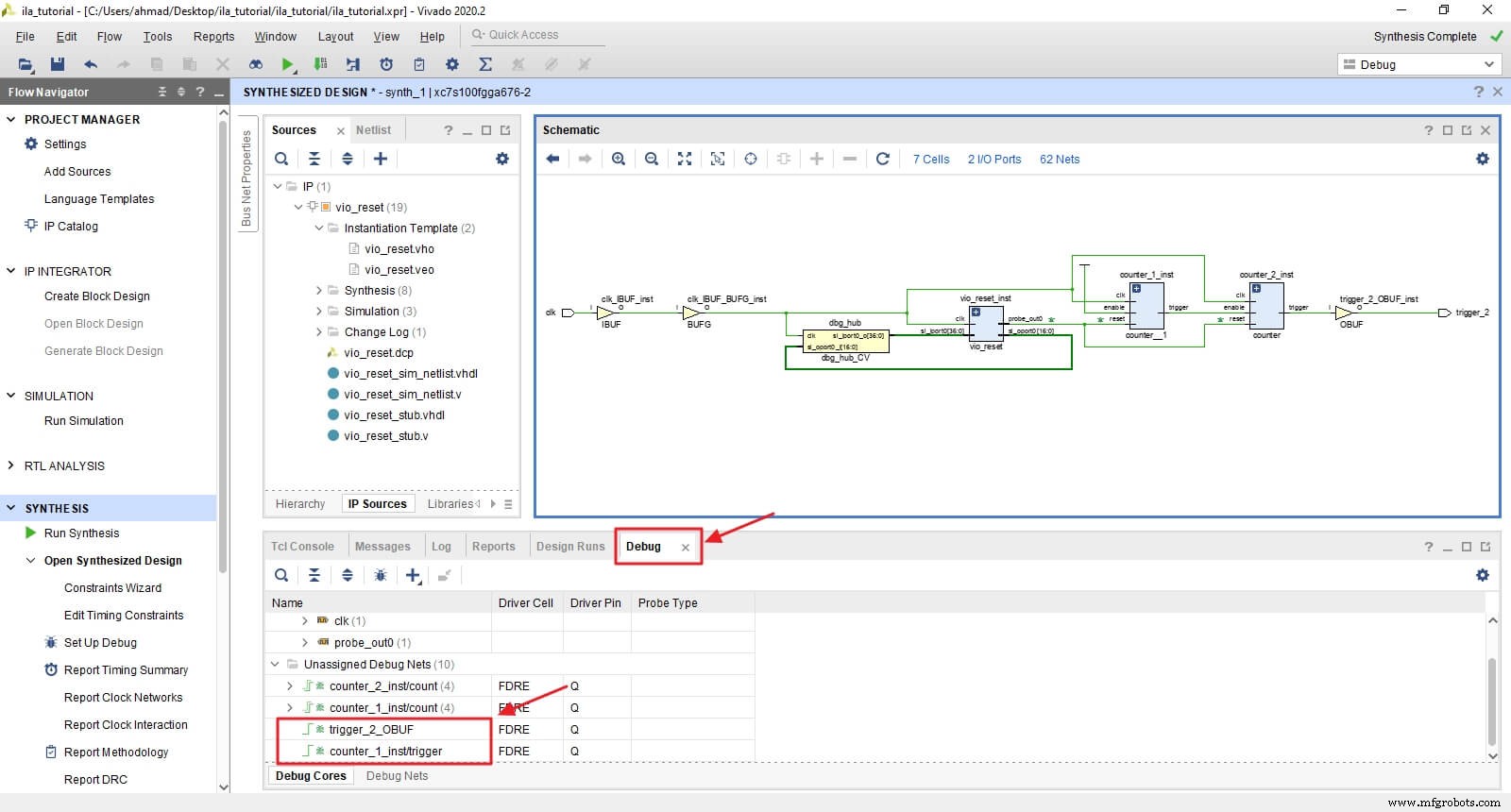

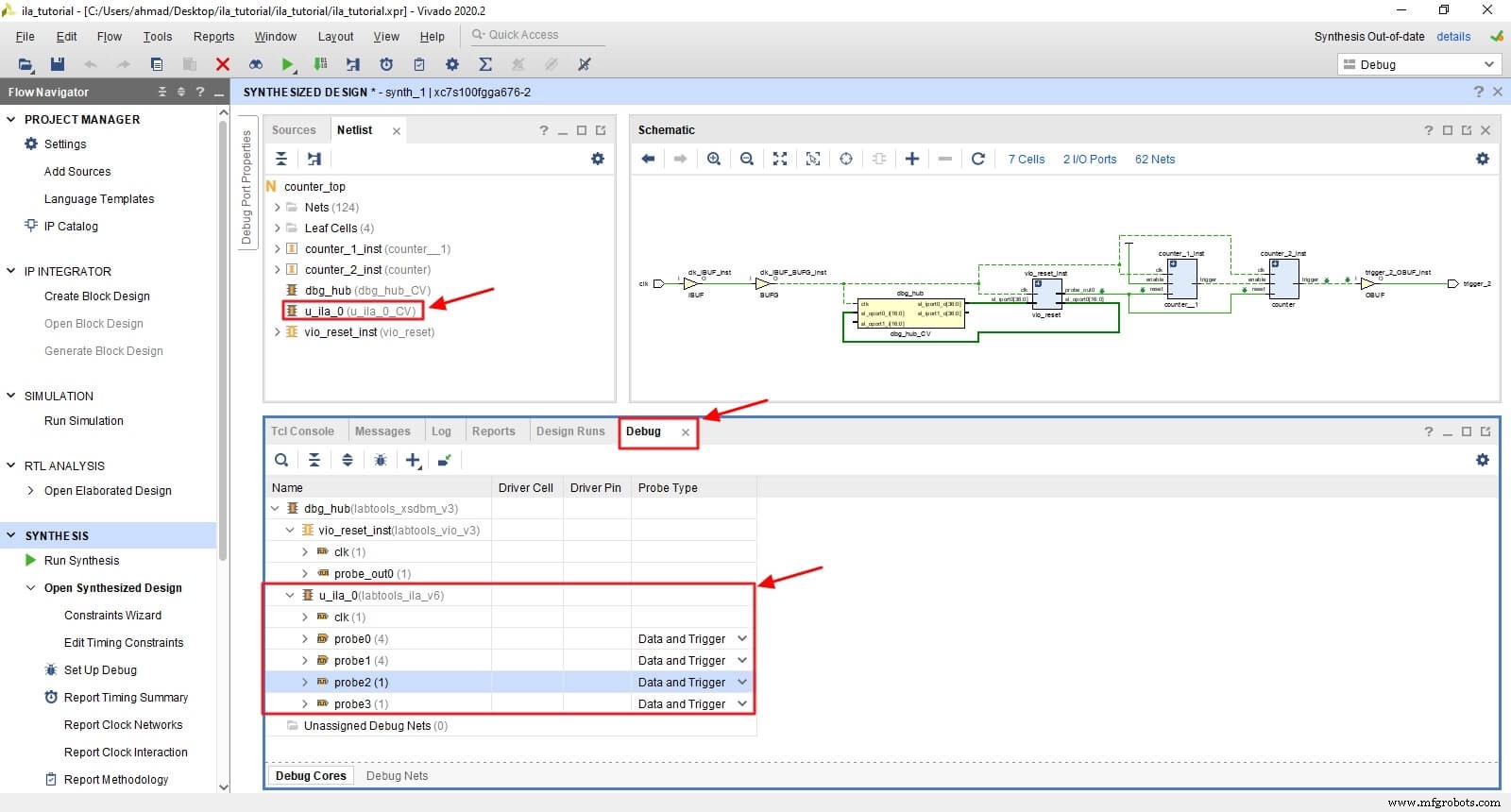

이제 디버그 탭에 4개의 프로브가 추가된 ILA 디버그 코어를 볼 수 있습니다. 및 넷리스트 창 .

중요: 이 단계에서 제약 조건을 저장하여 디자인에 추가할 수 있도록 하는 것이 매우 중요합니다. 그렇지 않으면 ILA 코어를 잃을 위험이 있습니다.

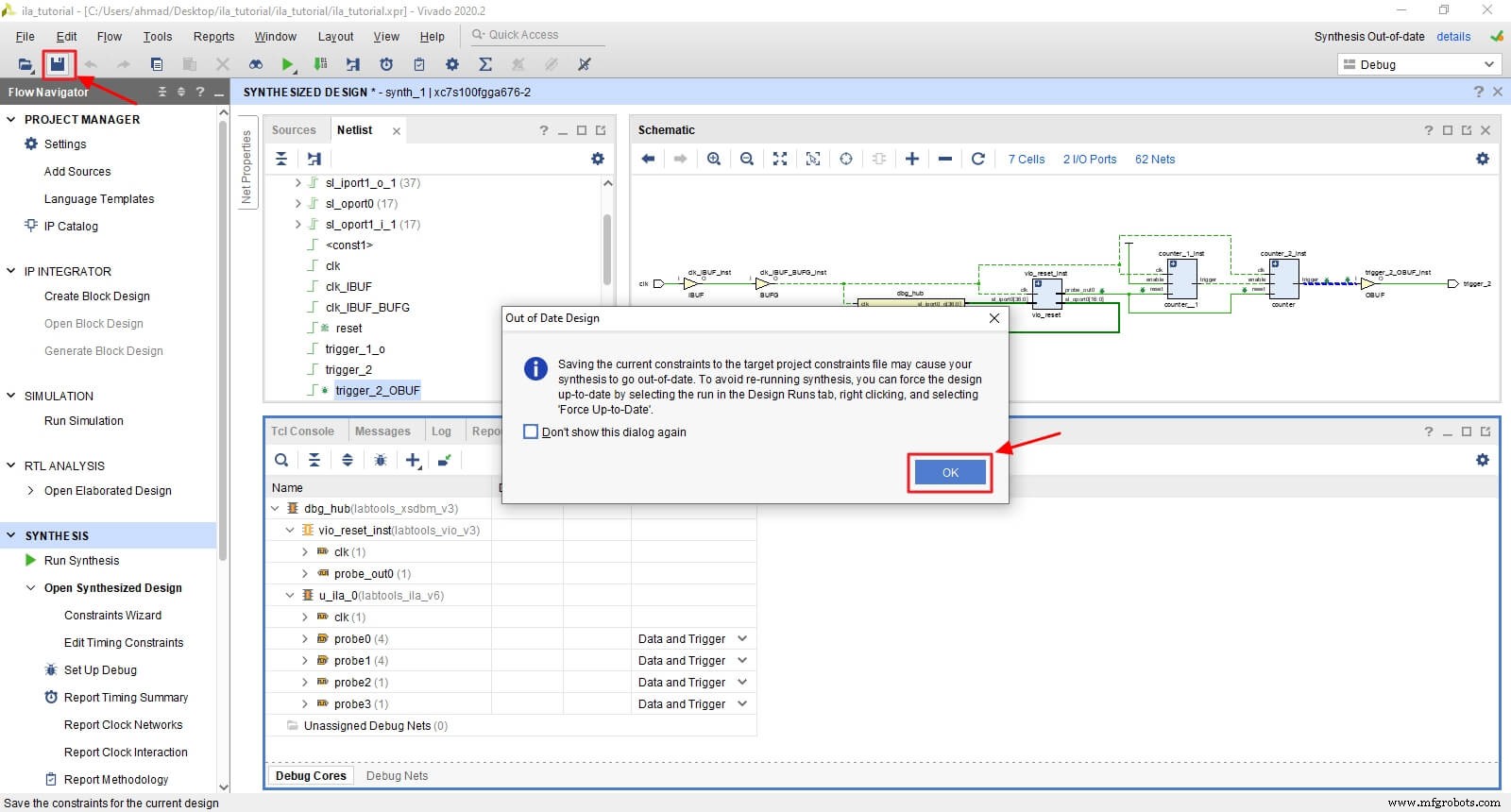

저장을 클릭합니다. 아이콘을 누르거나 Ctrl+S를 누르세요.

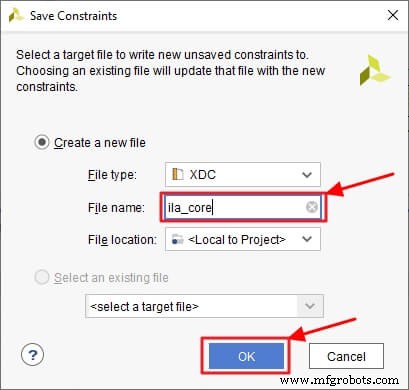

파일 이름을 ila_core로 지정 확인을 클릭합니다. .

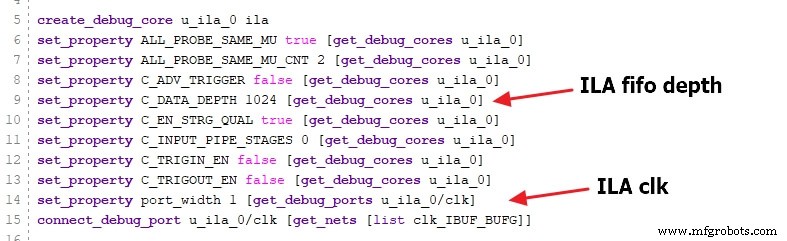

ila_core.xdc 파일이 제약 조건에 추가되고 여기에는 ILA에 대한 코드와 설정이 포함됩니다.

파일 내용을 살펴보자. 소스 창 → 제약 조건 폴더 확장 → constr_1 확장으로 이동하여 파일을 열 수 있습니다. .

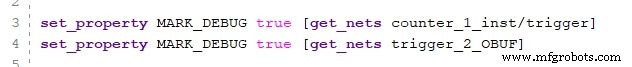

먼저, 파일이 Netlist 삽입을 사용하여 디버그로 표시한 신호에 디버그 속성을 추가하는 것을 봅니다.

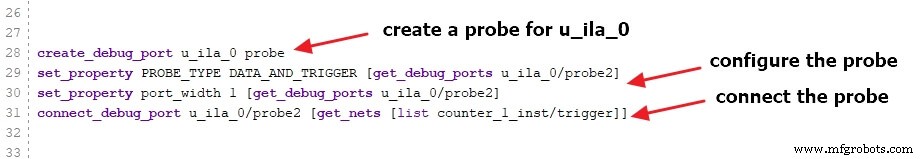

다음으로 ILA 코어의 생성 및 구성을 봅니다.

다음으로 각 프로브에 대한 생성, 구성 및 연결을 봅니다.

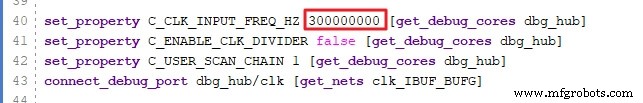

다음으로 디버그 허브(dbg_hub ).

디버그 허브는 비바도 IDE와 디버그 코어(ILA 및 VIO) 간의 통신을 담당합니다. 클럭 주파수를 정의하는 것을 볼 수 있습니다(기본값은 300MHz). 클럭 주파수와 일치하도록 해당 클럭을 변경하고 파일을 저장해야 합니다.

참고: ILA 및 Debug_hub에 연결된 시계는 자유 실행 시계여야 합니다.

이제 ILA가 완료되고 저장됩니다. 합성된 디자인에 ILA를 추가할 수 있도록 합성을 다시 실행해야 합니다.

합성 실행을 클릭합니다. 그런 다음 확인에서 .

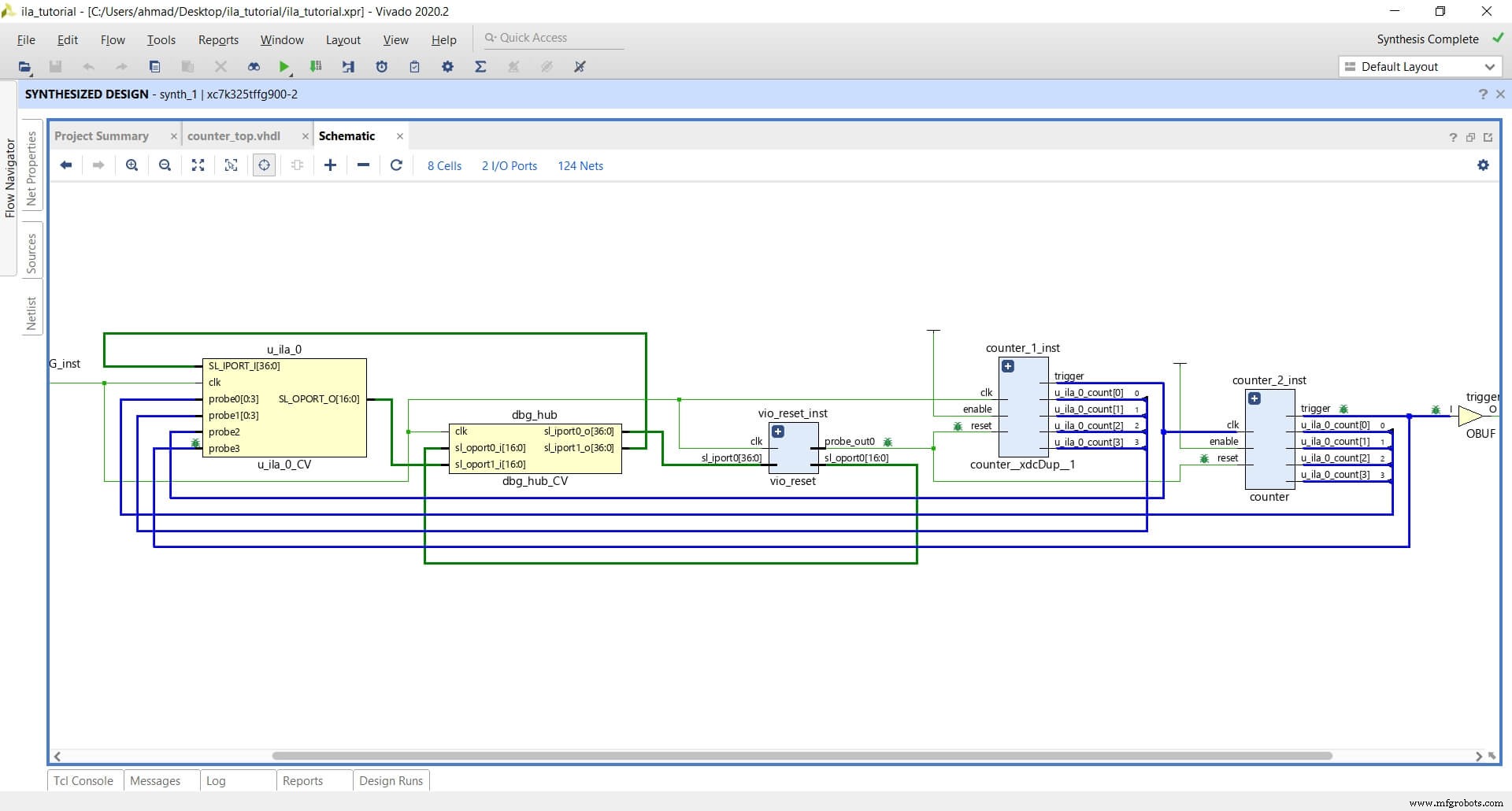

Vivado가 합성 실행을 마치면 합성된 디자인 열기를 클릭합니다. 그런 다음 도식 .

이제 Vivado가 설계에 ILA 및 Debug_Hub를 추가하고 디버그 신호를 ILA 프로브에 연결했음을 알 수 있습니다.

이제 디자인을 구현하고 비트스트림을 생성하여 디자인을 테스트할 준비가 되었습니다.

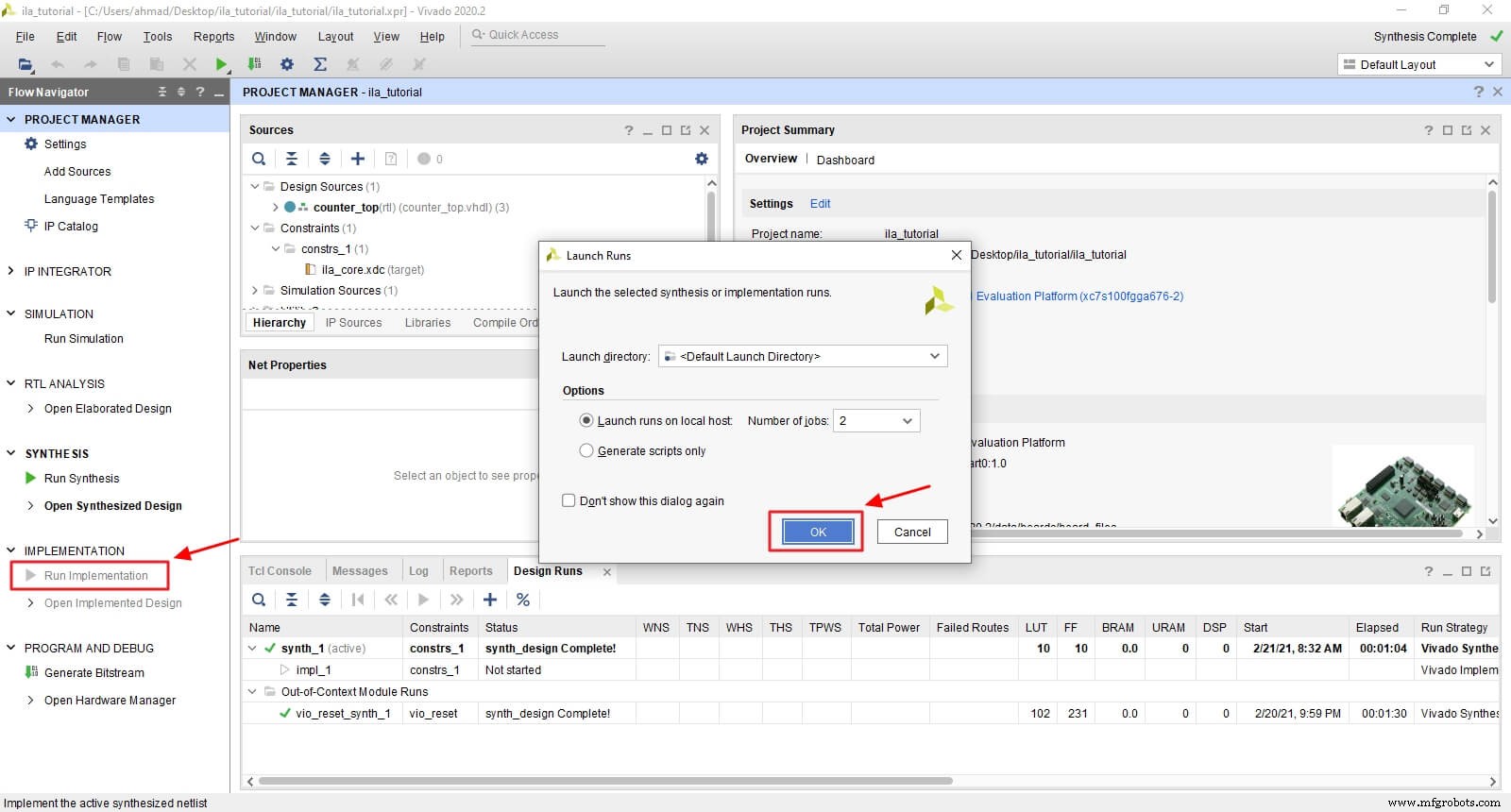

구현 실행 을 클릭하십시오. 그런 다음 확인에서 .

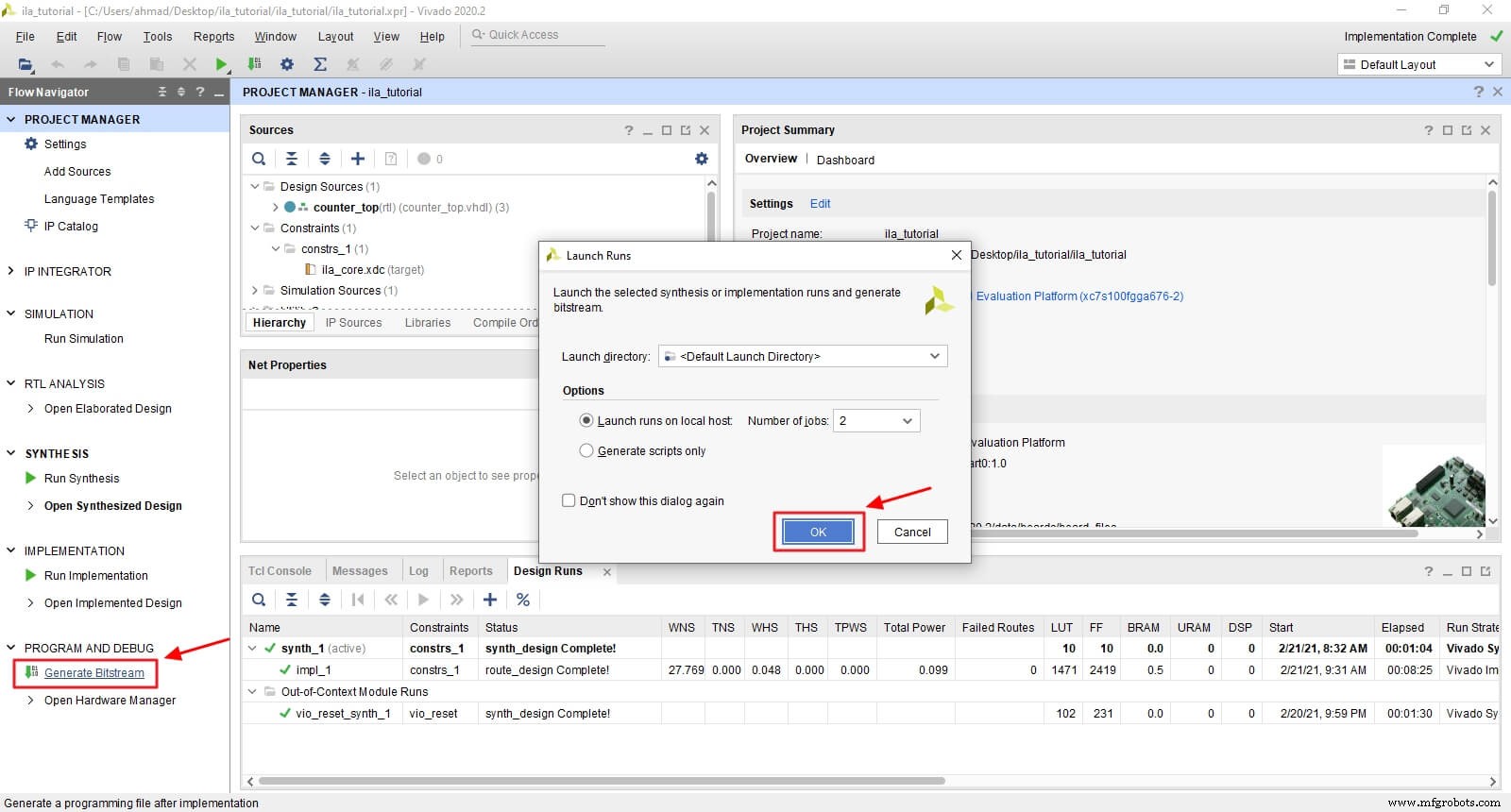

Vivado가 구현 실행을 완료한 후 비트스트림 생성을 클릭합니다. 그런 다음 확인에서 .

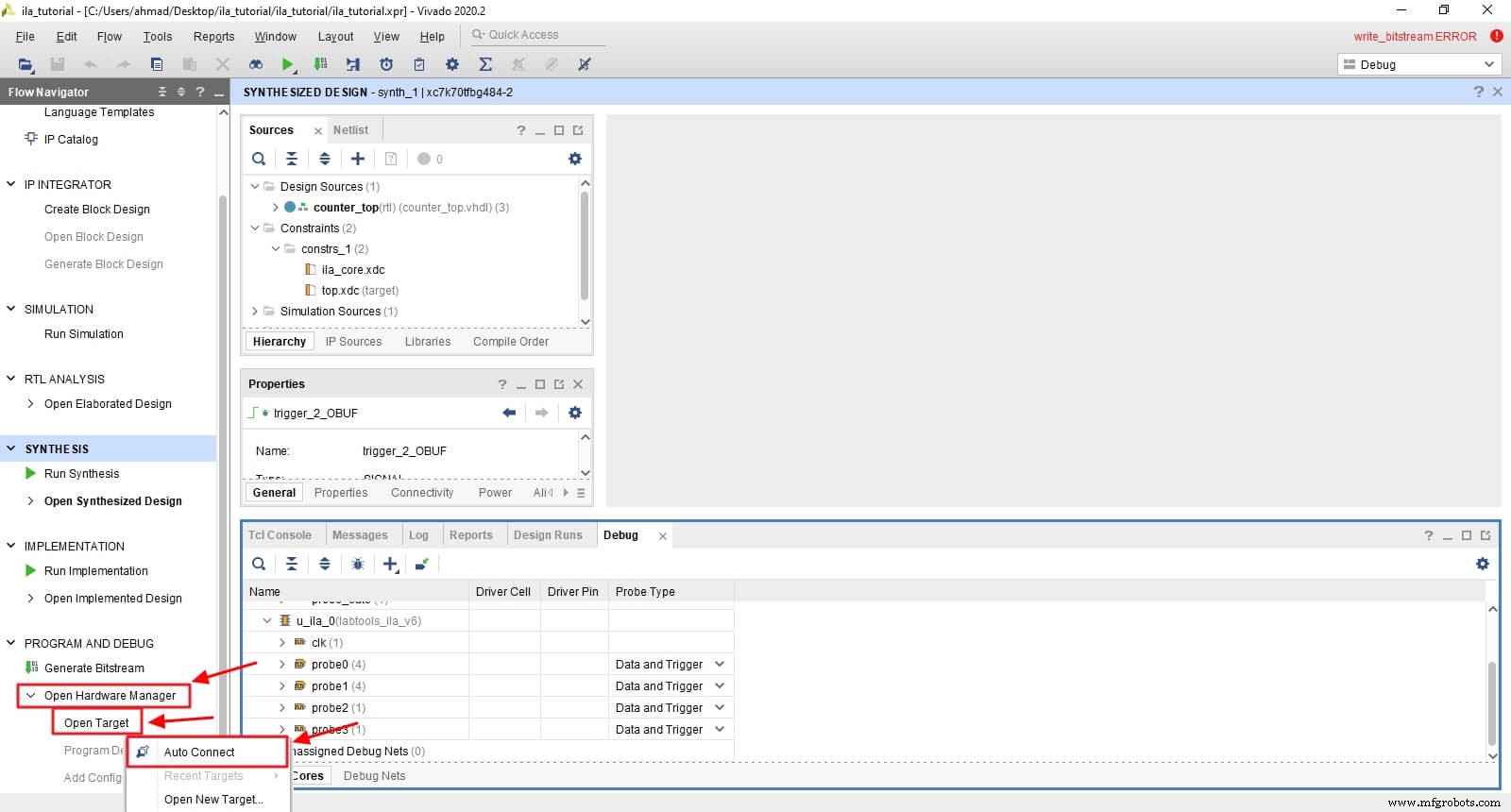

Vivado가 비트스트림 생성을 완료한 후 하드웨어 관리자 열기를 클릭합니다. 그런 다음 Open Target 에서 마지막으로 자동 연결에서 .

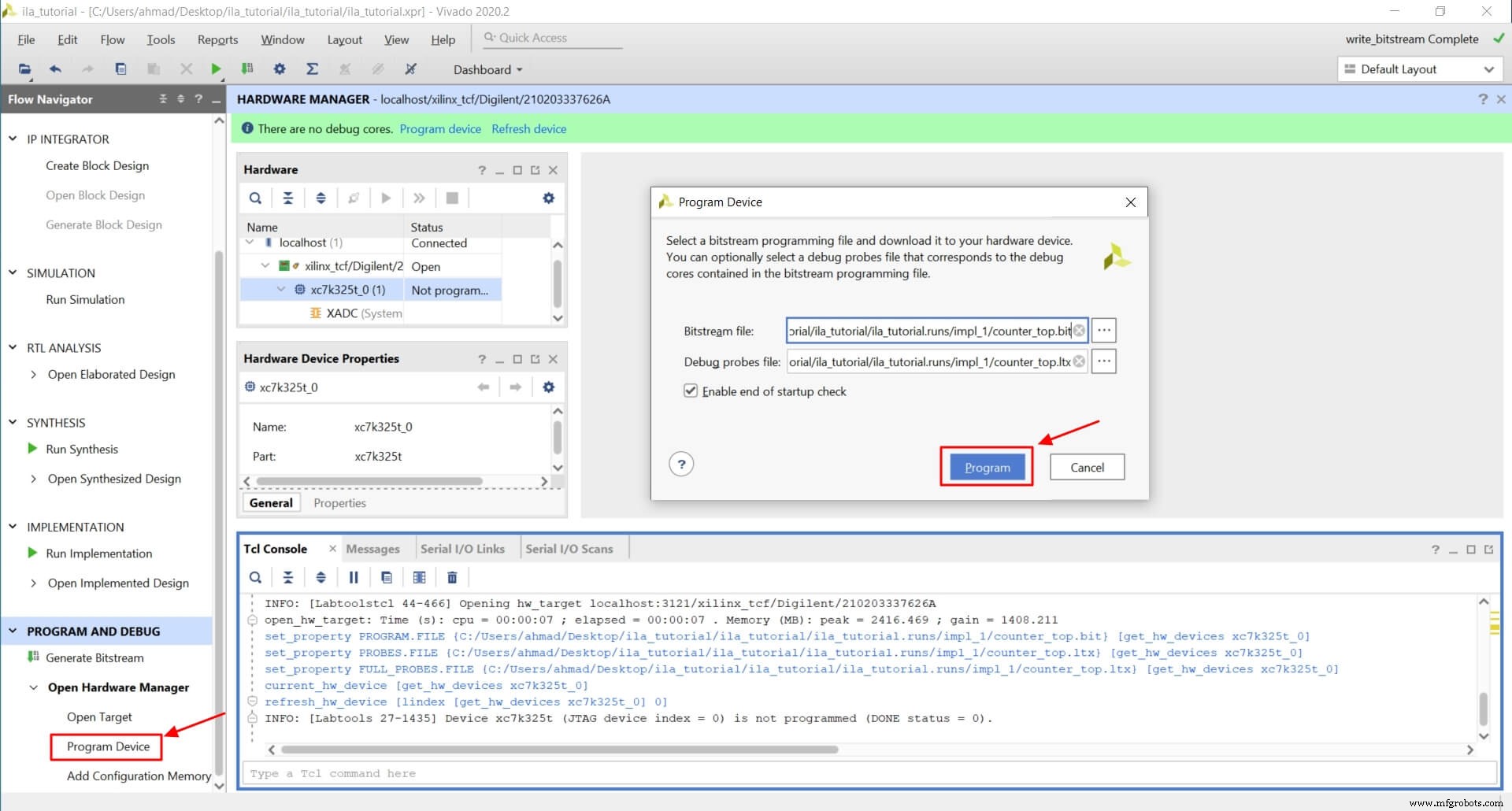

다음으로 비트 파일(*.bit)과 디버그 프로브 파일(*.ltx)로 FPGA를 프로그래밍해야 합니다. Vivado가 자동으로 찾아줍니다.

프로그램 기기를 클릭합니다. 그런 다음 프로그램에서 .

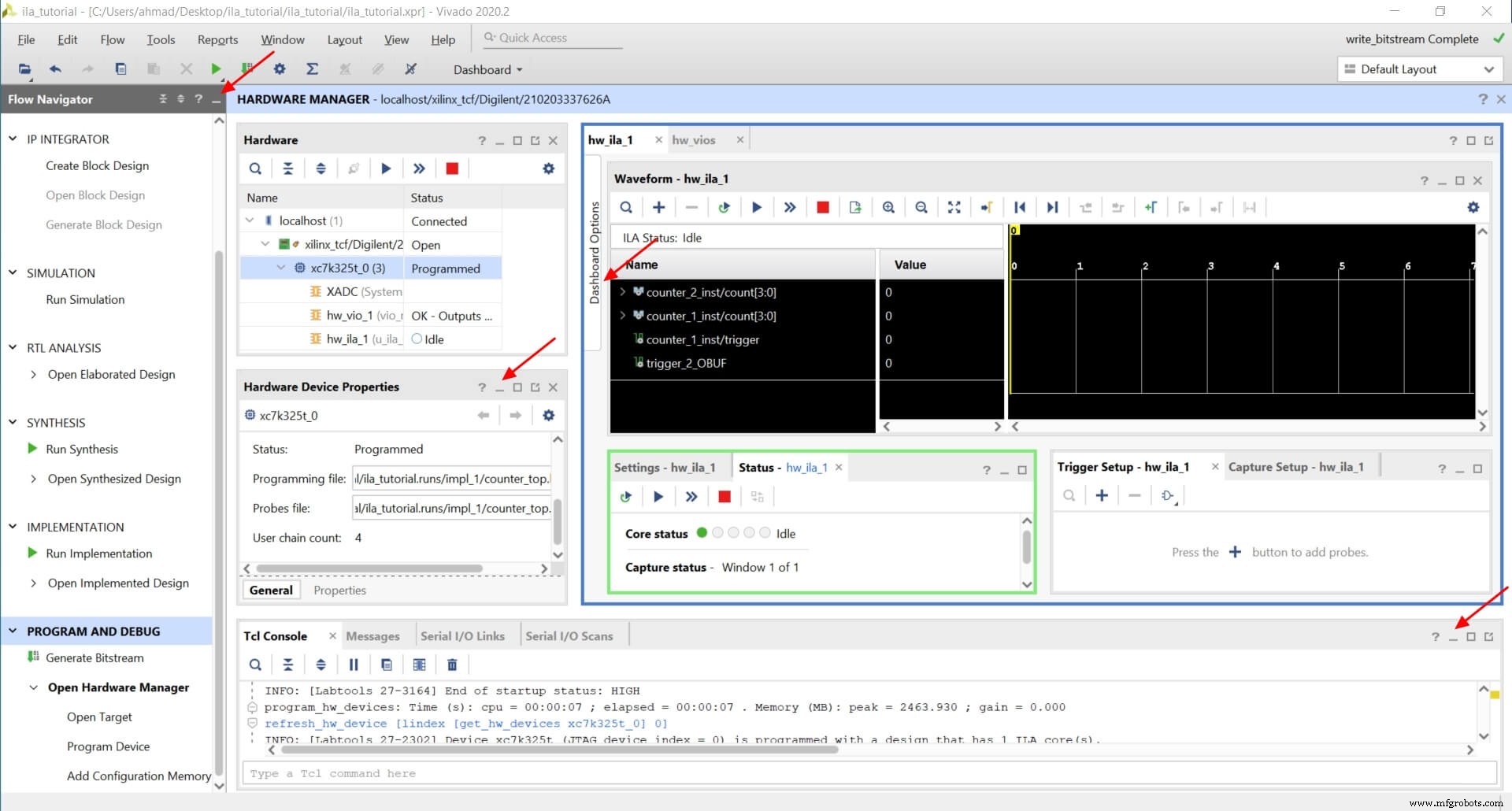

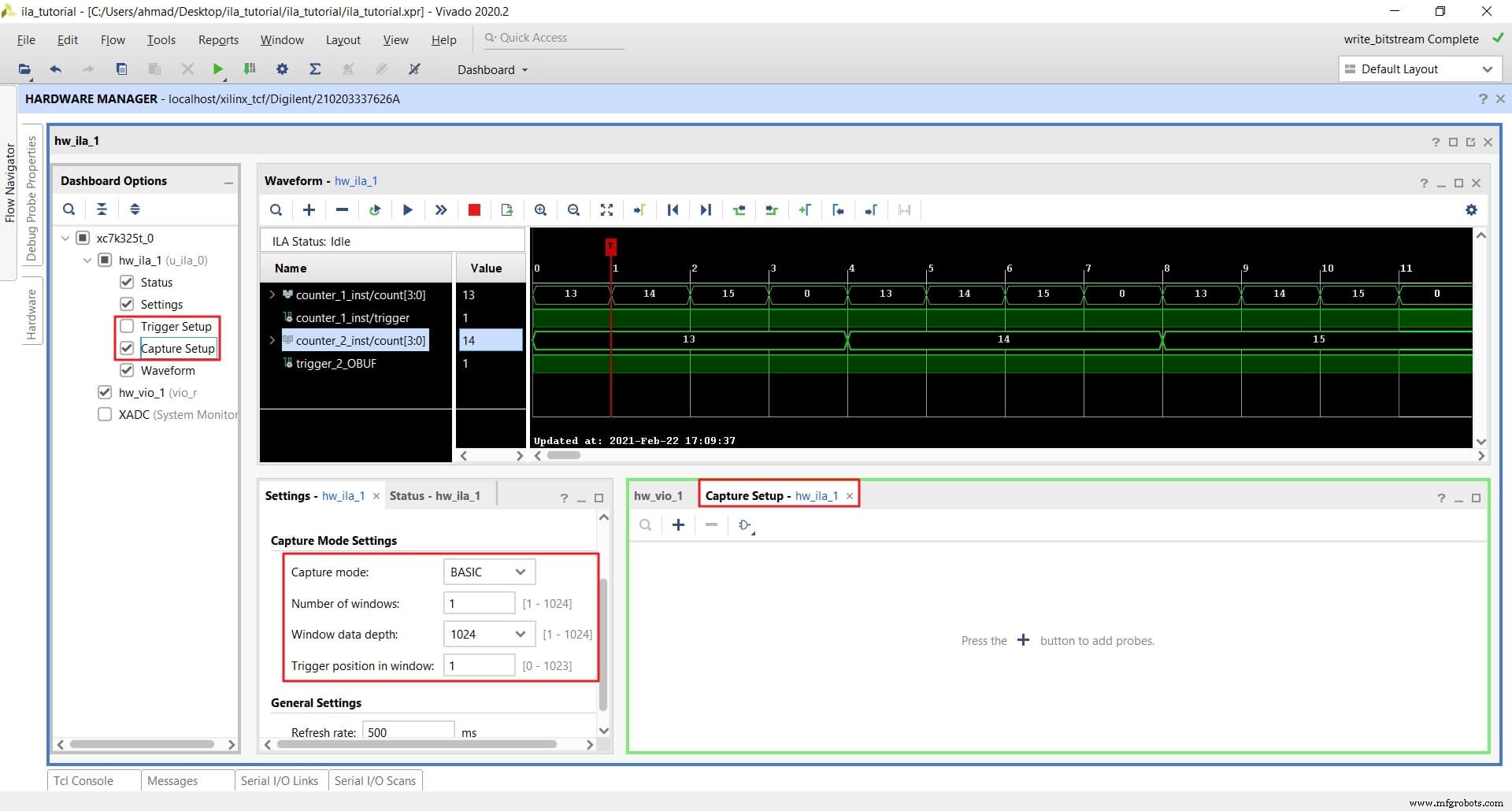

기기를 프로그래밍한 후 Vivado의 GUI 레이아웃이 변경되었으며 새로운 hw_ila_1 여러 창이 포함된 대시보드가 열렸습니다.

필요하지 않은 일부 창은 최소화하여 편안하게 작업할 수 있도록 하겠습니다.

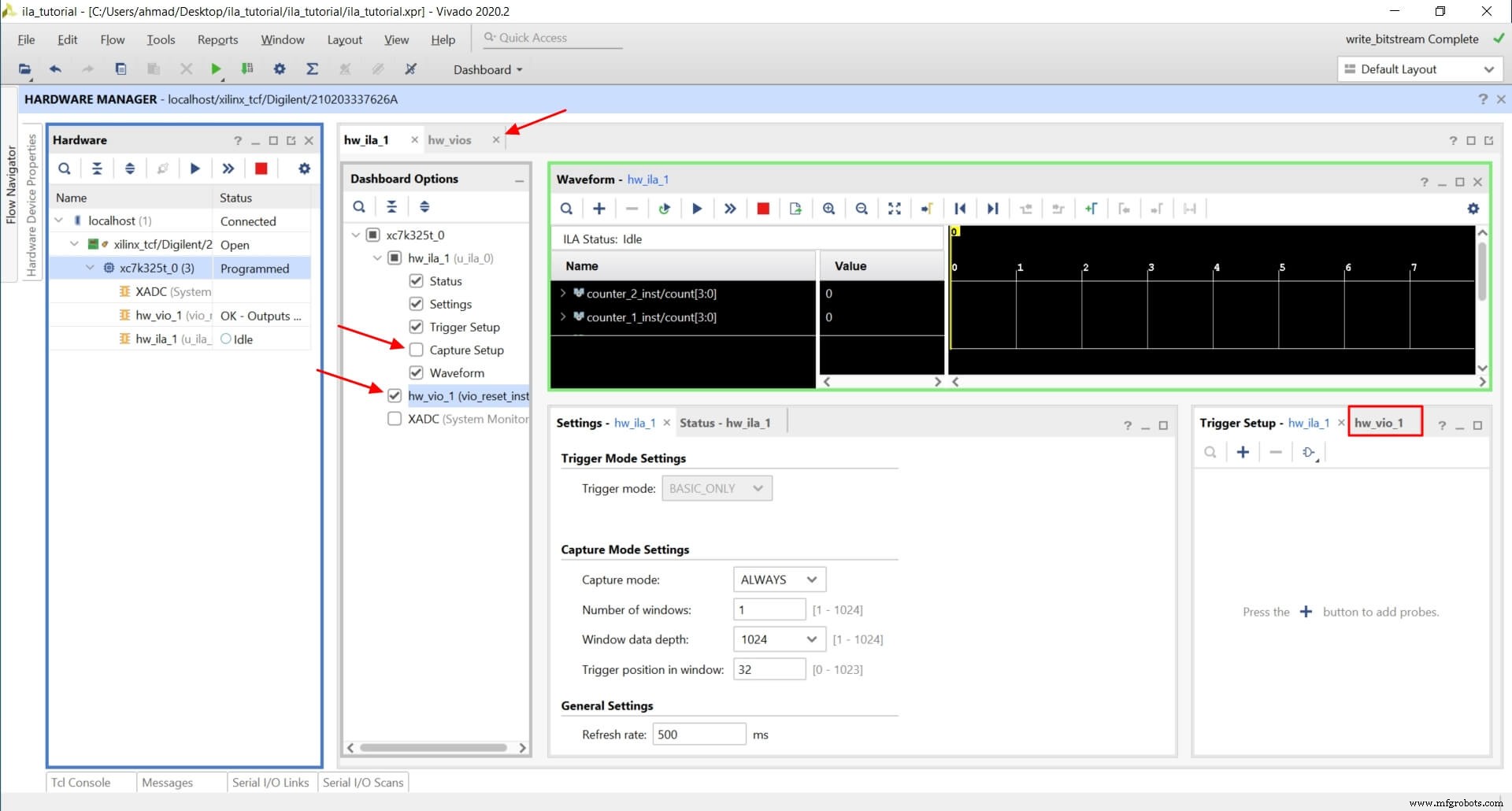

대시보드 옵션에서 hw_vio_1을 확인합니다. 캡처 설정을 선택 취소합니다. .

또한 hw_vios를 닫습니다. hw_vio_1을 확인했기 때문에 탭 , 트리거 설정에 추가되었습니다. 창.

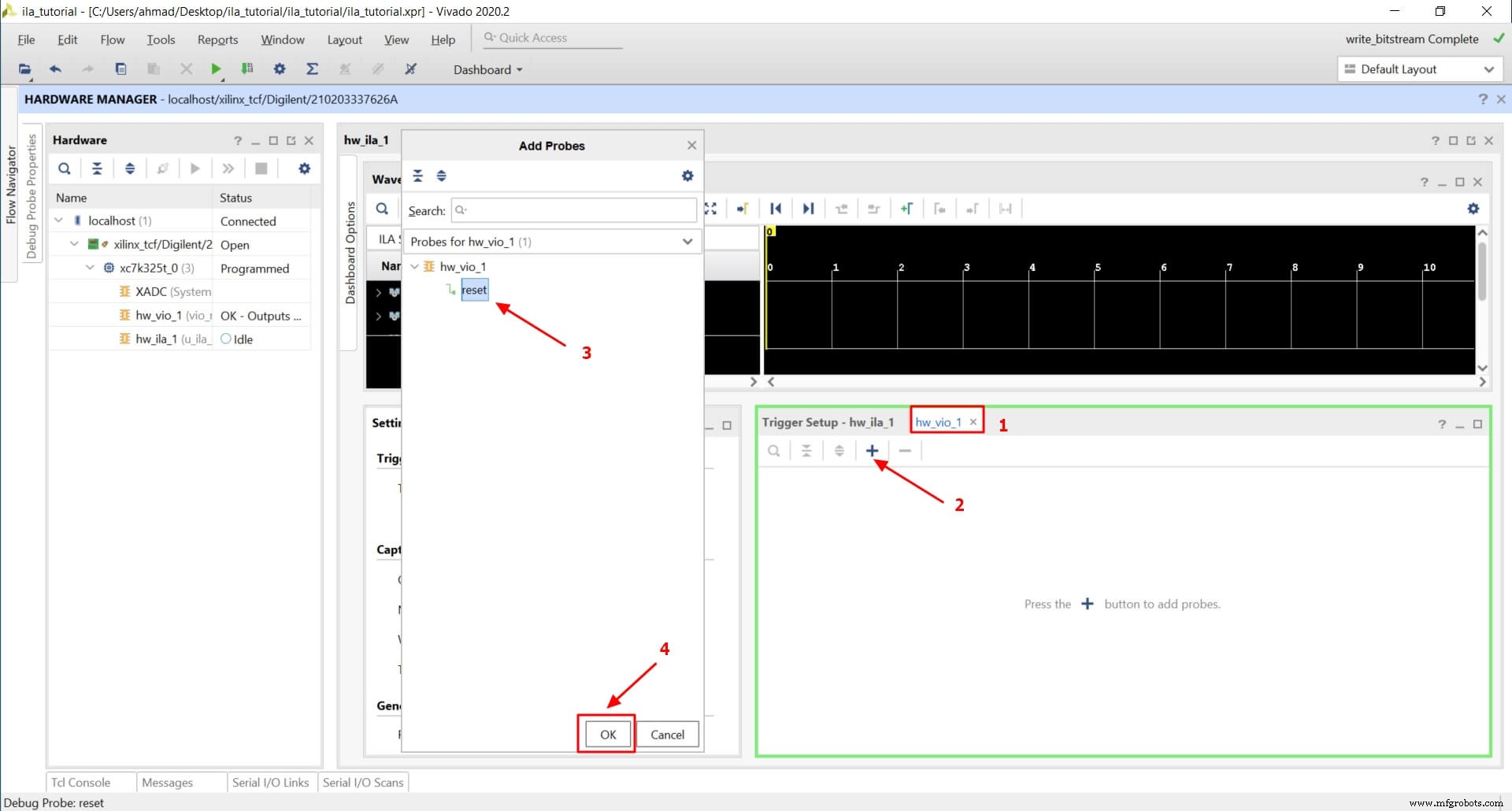

이제 재설정을 추가해야 합니다. 버튼을 VIO에 연결하여 재설정을 제어할 수 있습니다. .

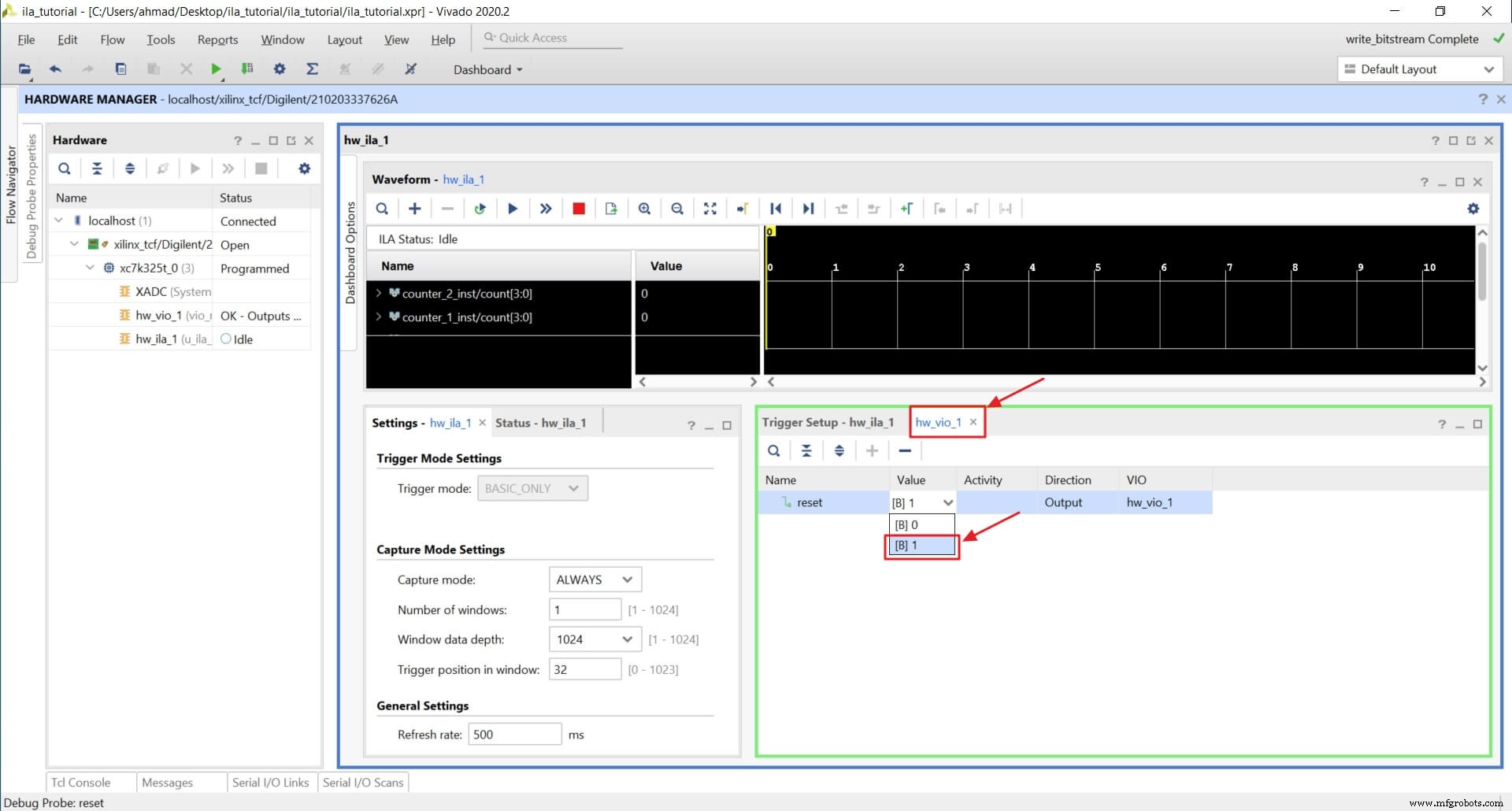

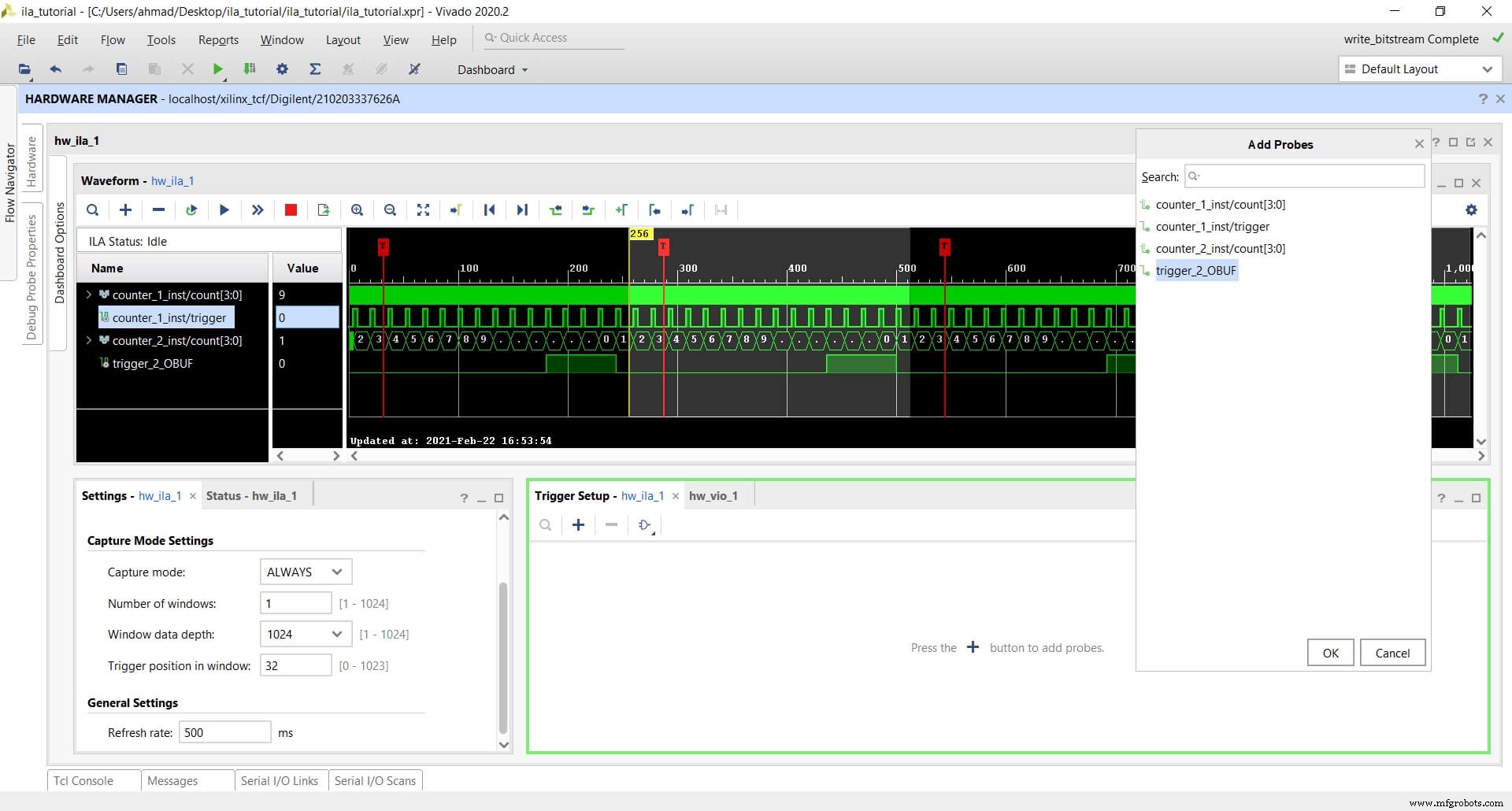

hw_vio_1 을 클릭하십시오. 그런 다음 재설정을 추가하세요. 아래 그림과 같이

hw_vio_1 이제 재설정이 포함됩니다. 조사.

재설정 값 변경 1이 아닌 경우 vio_reset을 1로 설정합니다.

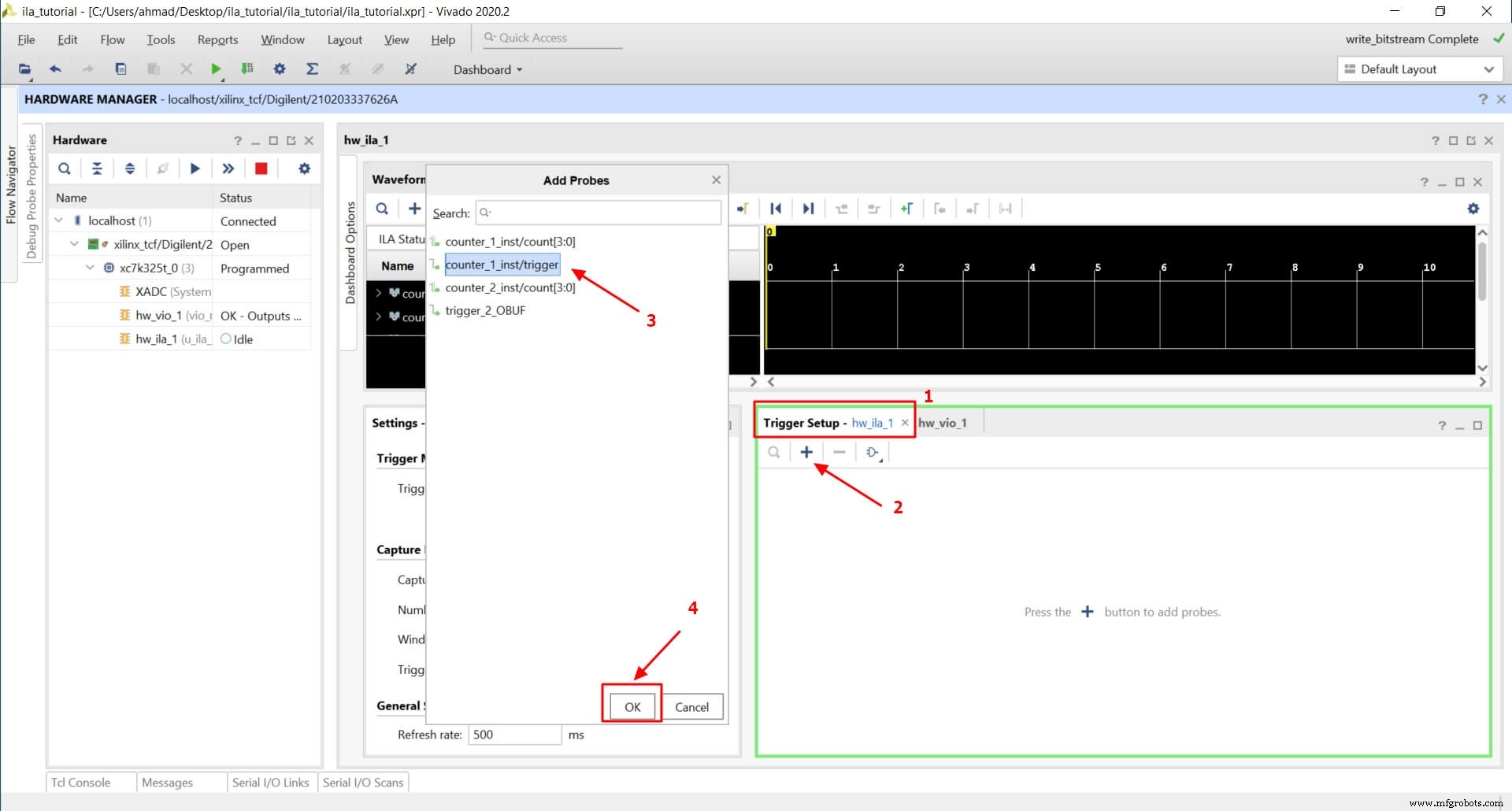

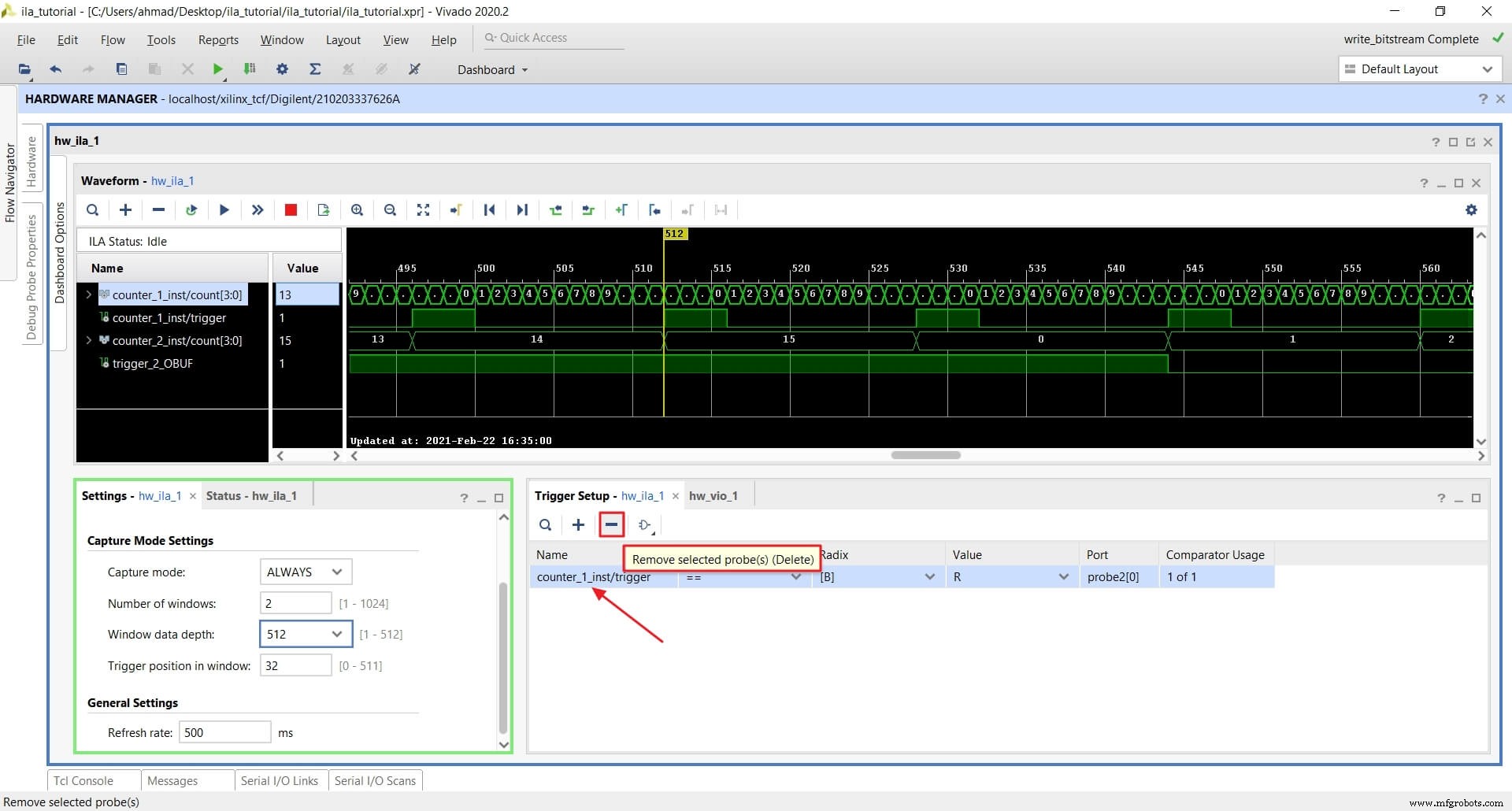

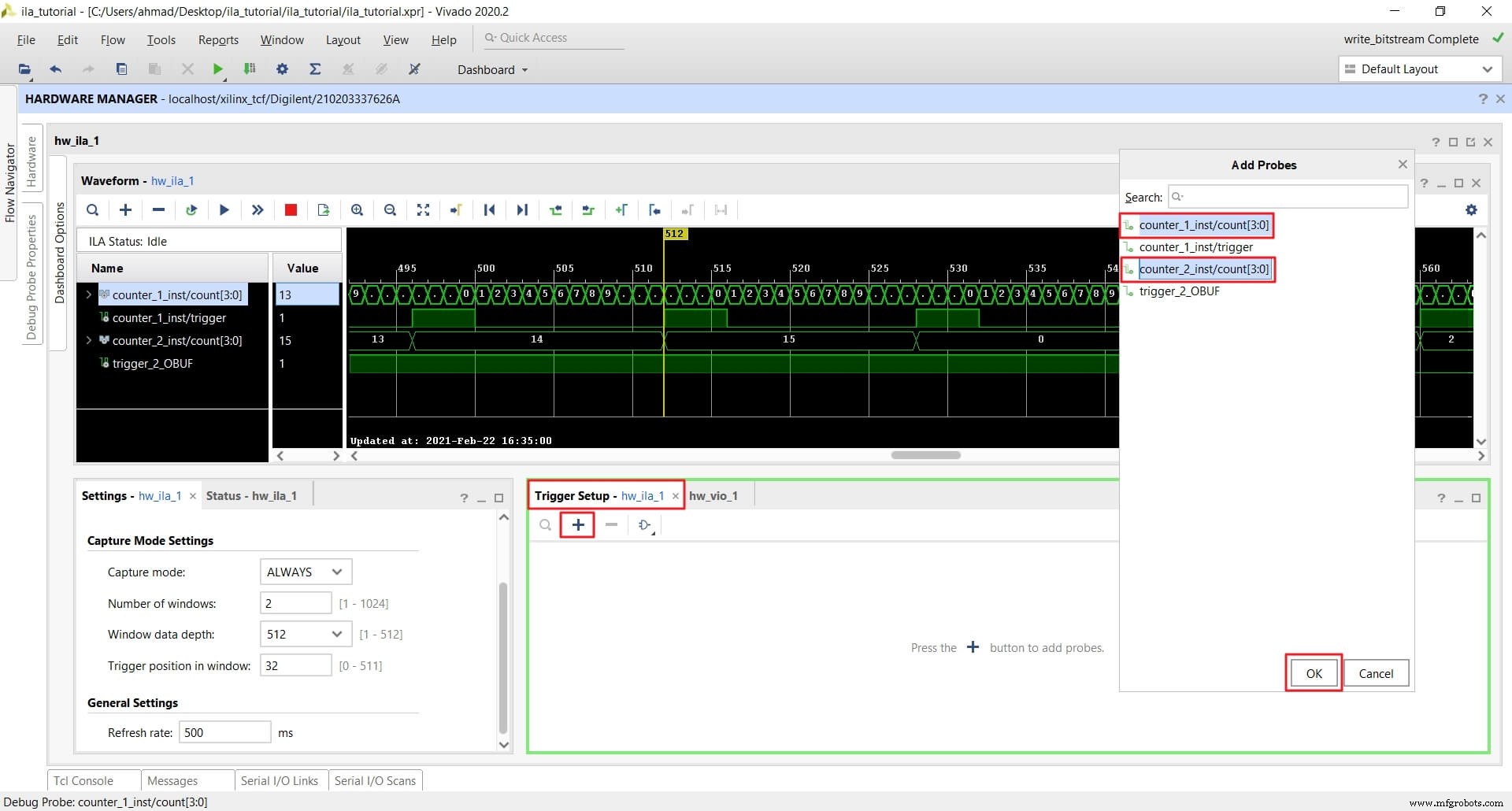

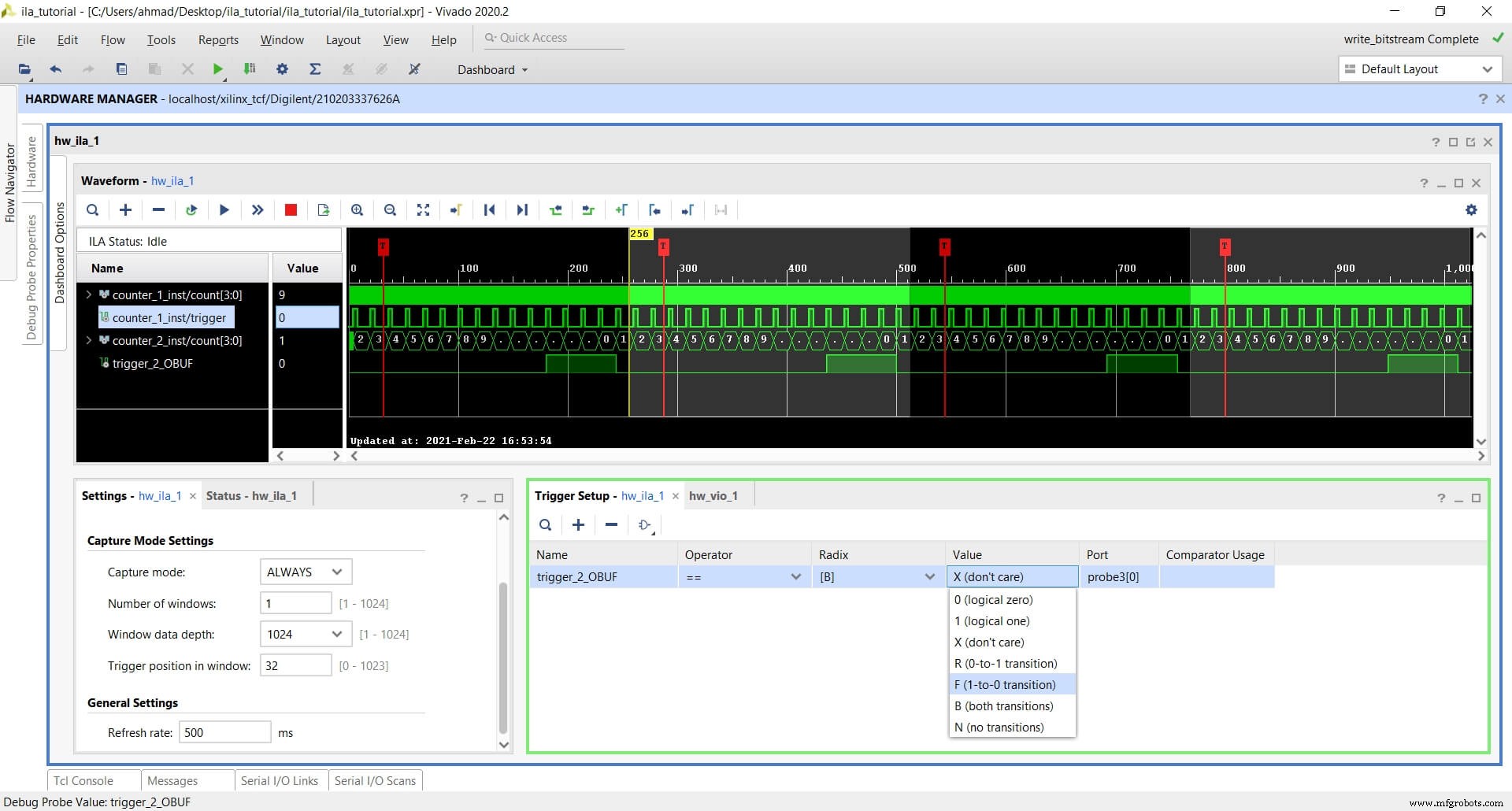

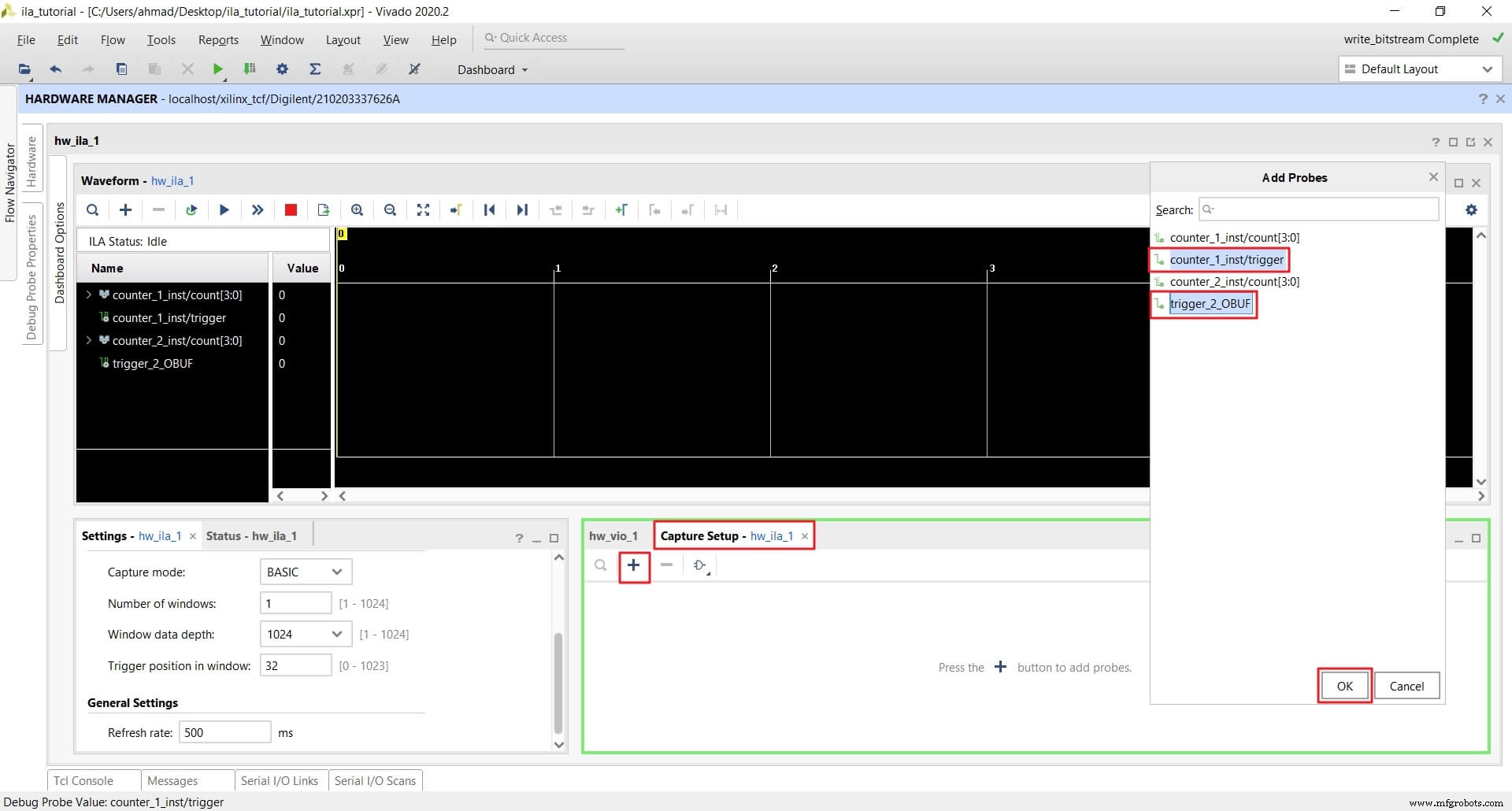

이제 사용할 트리거를 추가합니다. 트리거 신호의 값이 변경되면 ILA가 프로브된 신호를 기록하기 시작합니다.

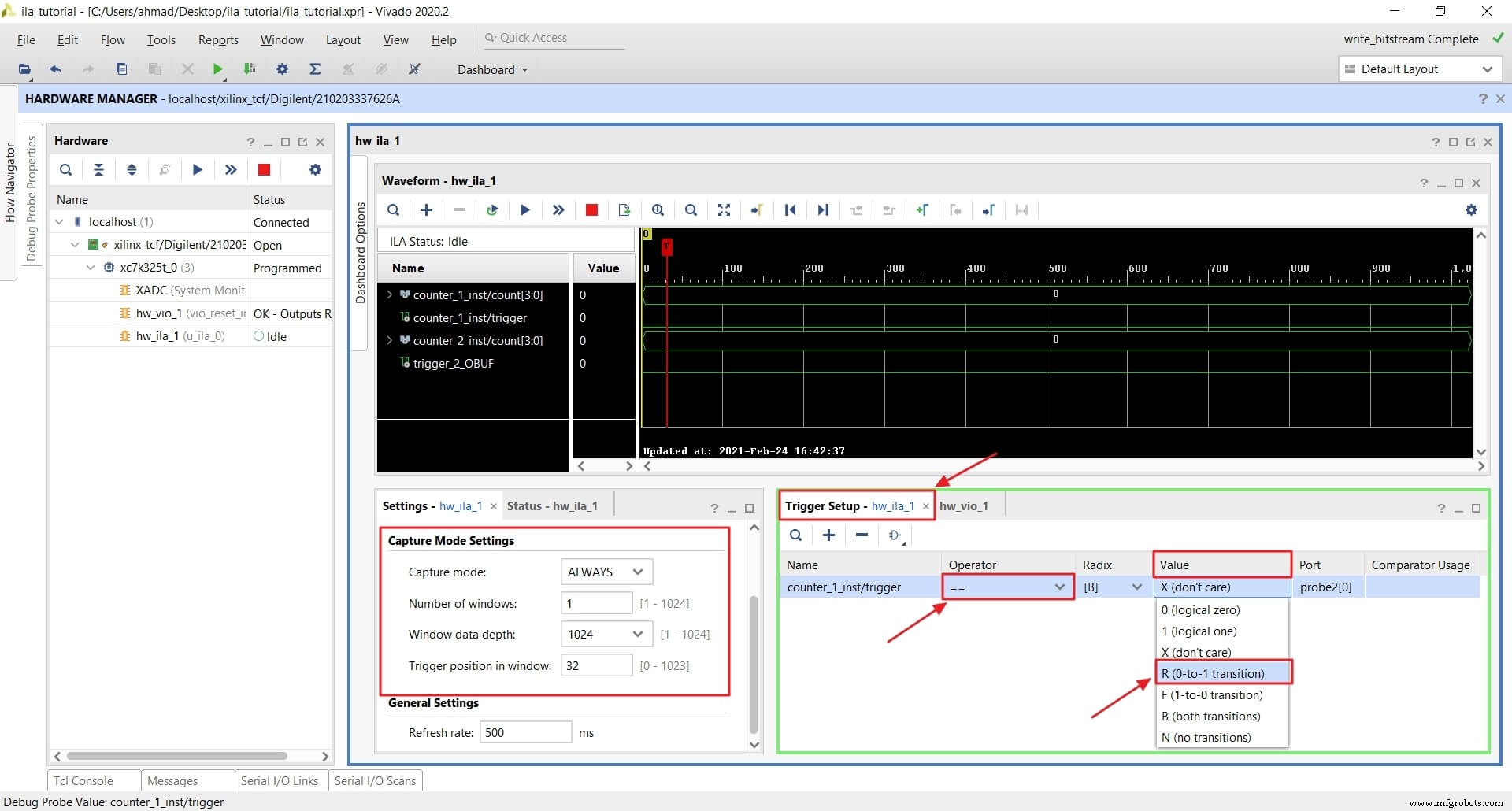

출력 포트 트리거의 상승 에지에서 트리거(녹화 시작)하고 싶다고 가정해 보겠습니다. counter_1_inst의 . 그렇게 하려면 다음 단계를 따르세요.

또한 트리거 위치를 32로 변경합니다. 즉, 트리거 이벤트 이후에 추가로 트리거 이벤트 전에 32개의 샘플을 기록합니다.

이제 방아쇠가 설정되었고 무장할 준비가 되었습니다.

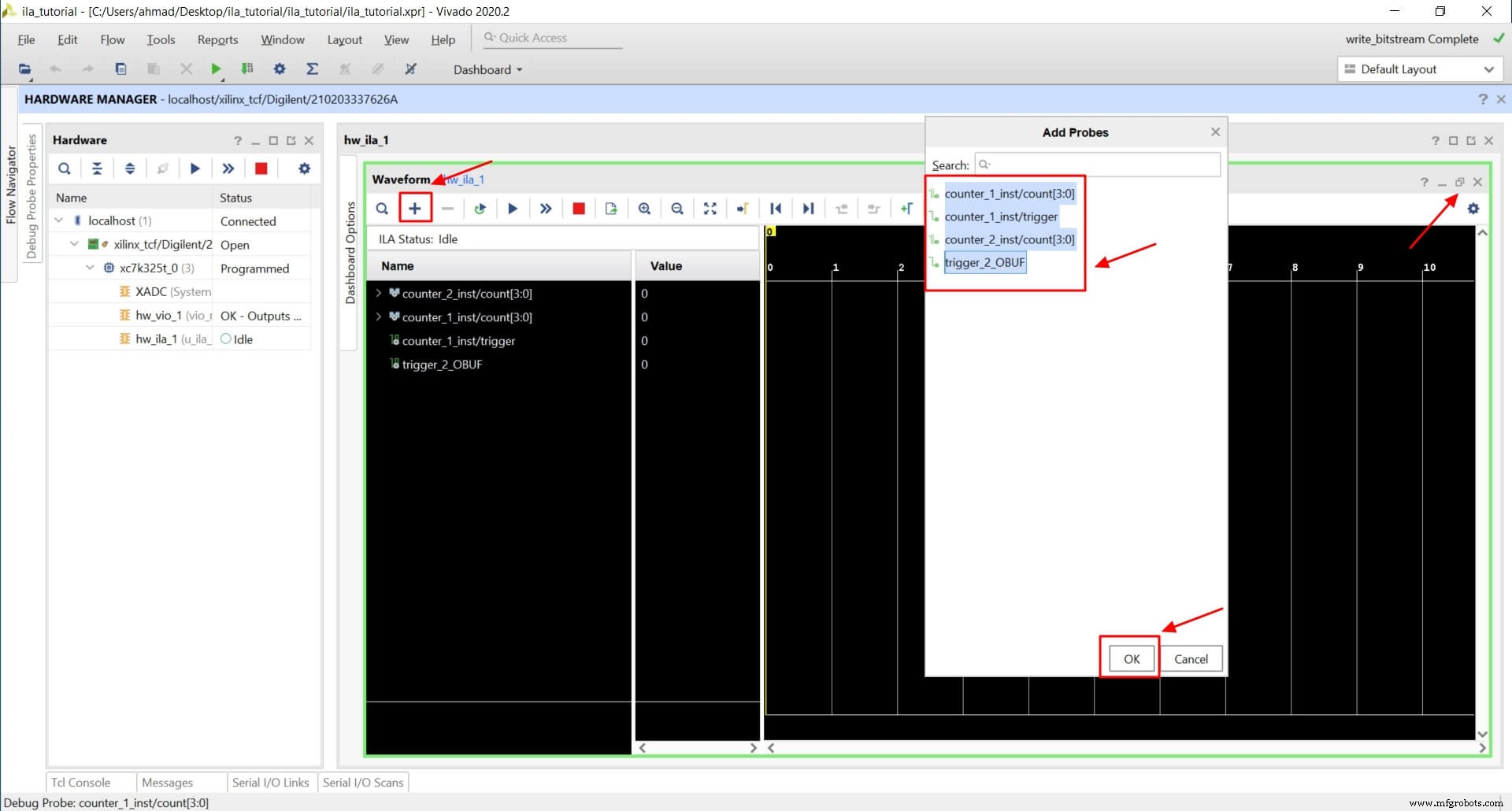

이제 파형 창으로 이동합니다. 보고 싶은 신호를 추가합니다. 먼저 내부 창을 최대화하여 더 잘 볼 수 있도록 합시다.

둘째, 프로브에 누락된 신호를 추가해야 합니다. Vivado는 일반적으로 할당된 모든 신호를 자동으로 추가하지만 이 경우에는 그렇지 않습니다.

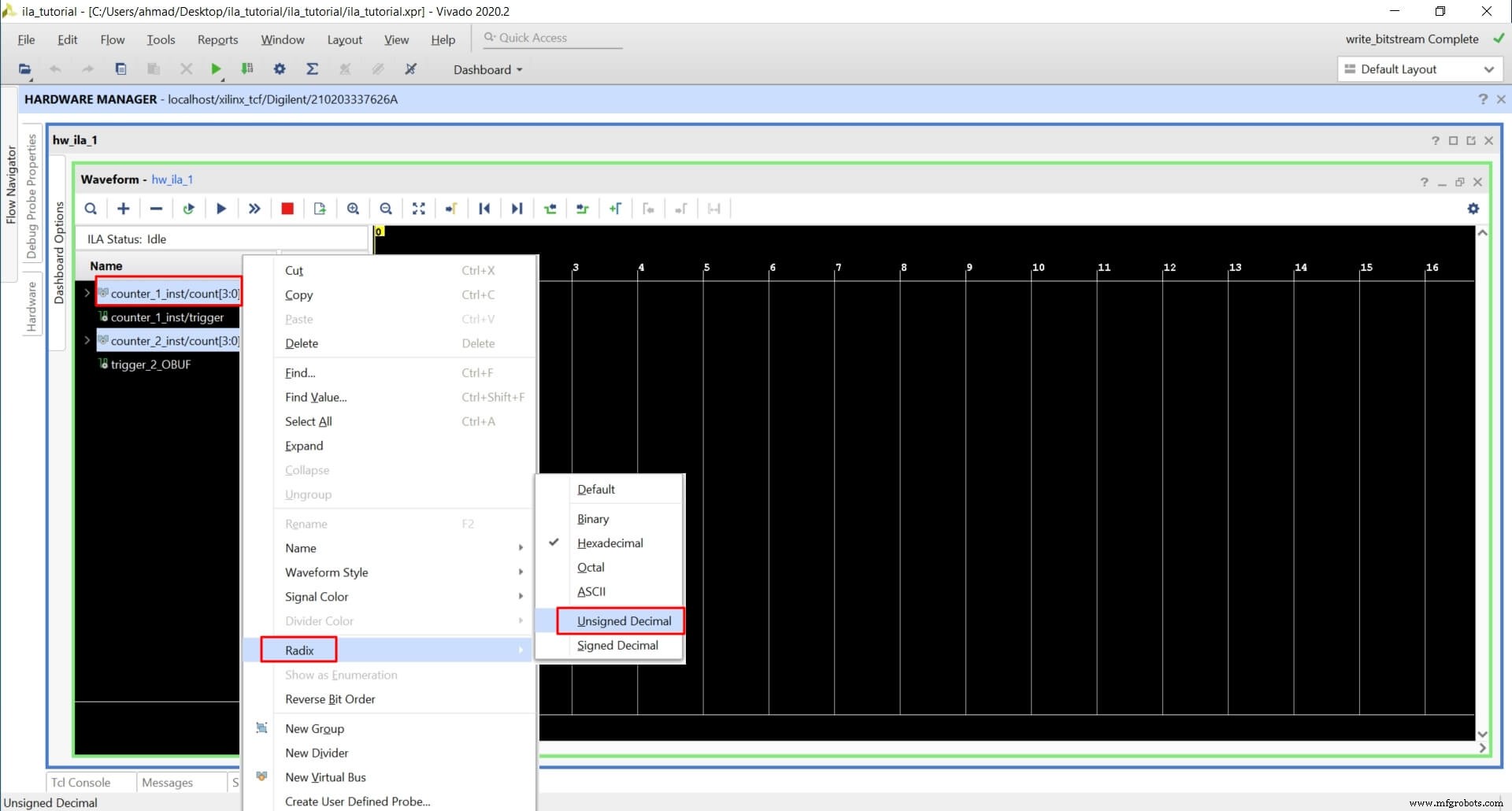

이제 count의 기수를 변경합니다. 따르기 쉽기 때문에 Unsigned에 신호를 보냅니다.

개수를 마우스 오른쪽 버튼으로 클릭합니다. 신호 이름을 선택한 다음 기수 를 선택하십시오. 그런 다음 서명되지 않음 .

이제 ILA 구성 및 사용자 지정을 완료했으며 실행할 준비가 되었습니다.

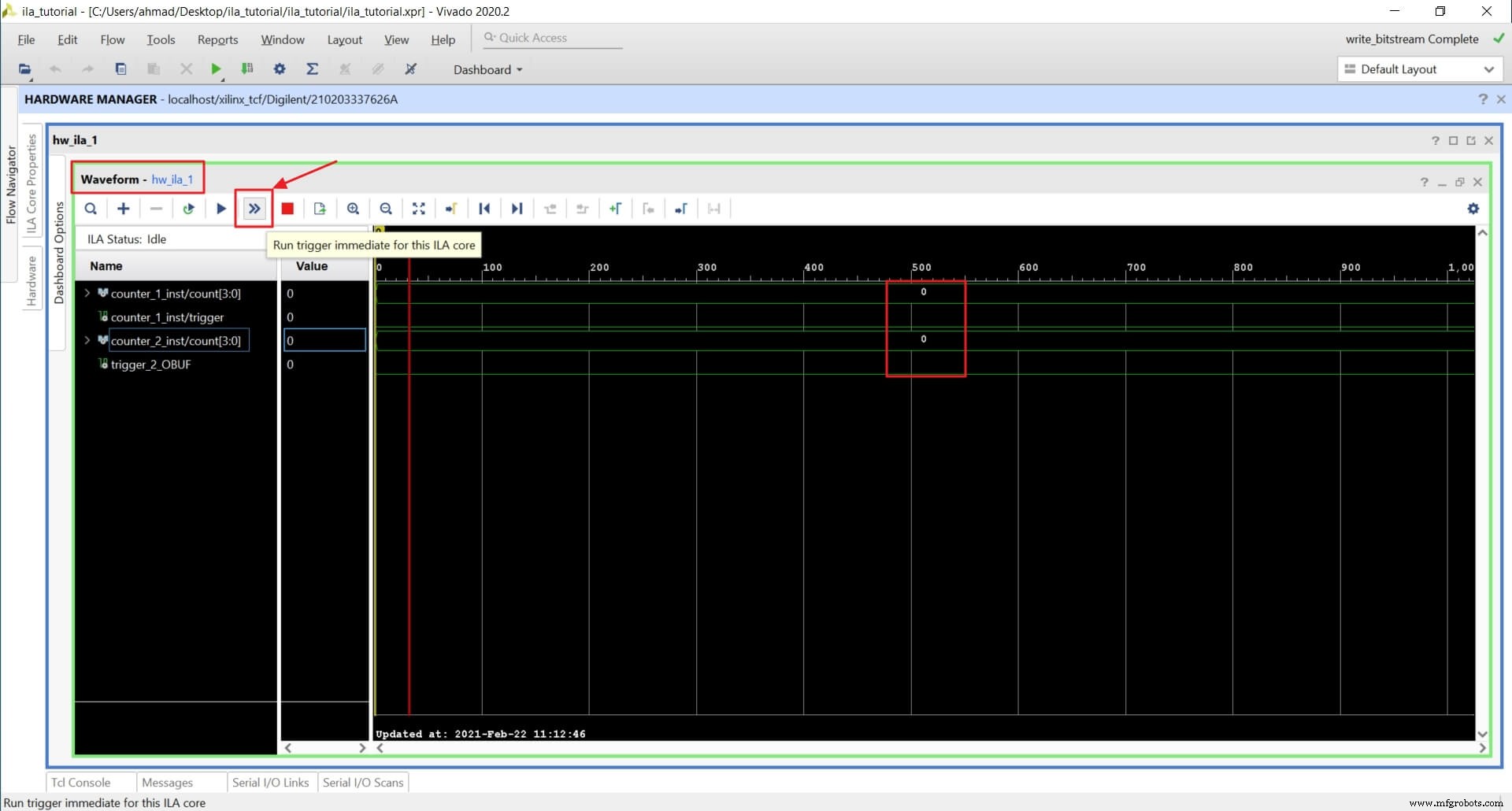

ILA에는 두 가지 실행 모드가 있습니다. 즉시 및 트리거 .

Immediate 모드는 ILA를 즉시 트리거하고 FIFO가 가득 찰 때까지 샘플을 직접 녹음하기 시작합니다.

즉시 트리거 실행을 클릭합니다. 버튼.

이제 파형 창에서 기록된 샘플을 볼 수 있습니다. 둘 다 카운트합니다. 신호는 0,입니다. 및 둘 다 트리거 신호가 낮음 '0'입니다. 재설정 하기 때문에 활성 상태입니다.

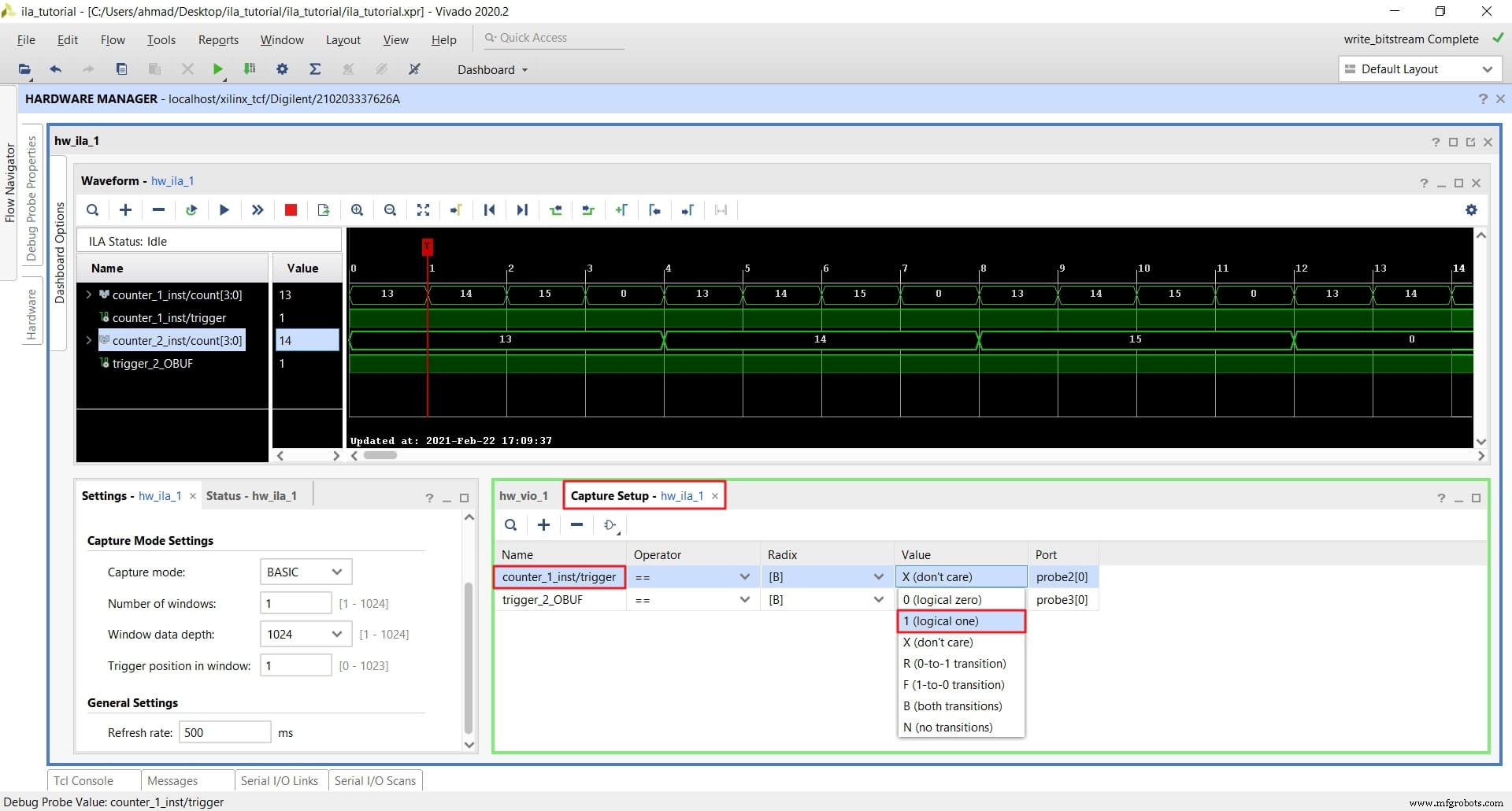

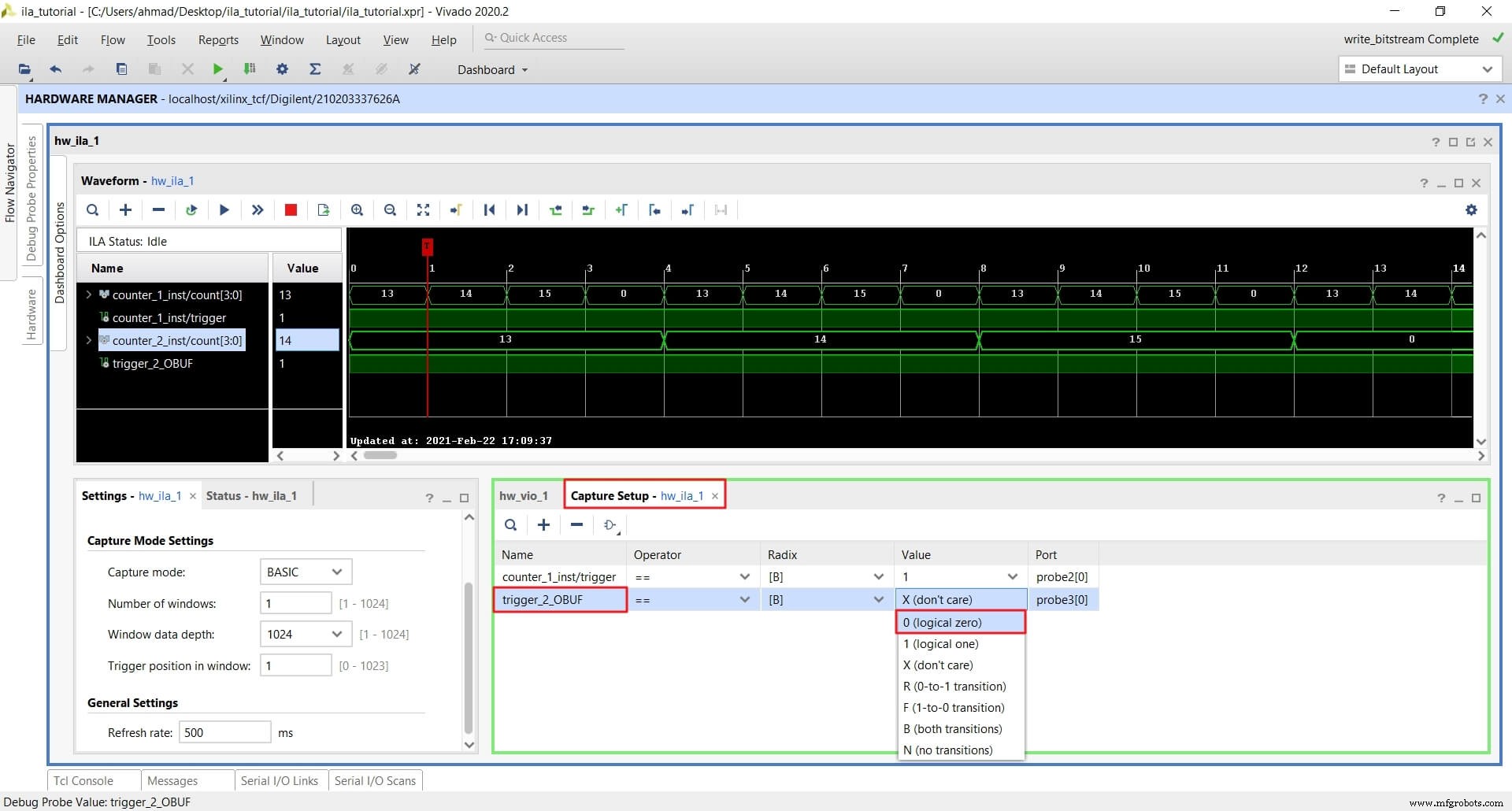

트리거 모드를 사용하려면 하나 이상의 트리거에 대한 조건을 설정하고 준비해야 합니다. ILA는 무장된 트리거의 조건이 true가 될 때까지 계속 기다린 다음 FIFO가 가득 찰 때까지 샘플을 직접 기록하기 시작합니다.

이미 트리거를 추가했으며 R(0에서 1로의 전환)으로 설정했습니다. .

재설정 변경 1로 돌아가기 vio_reset에서 .

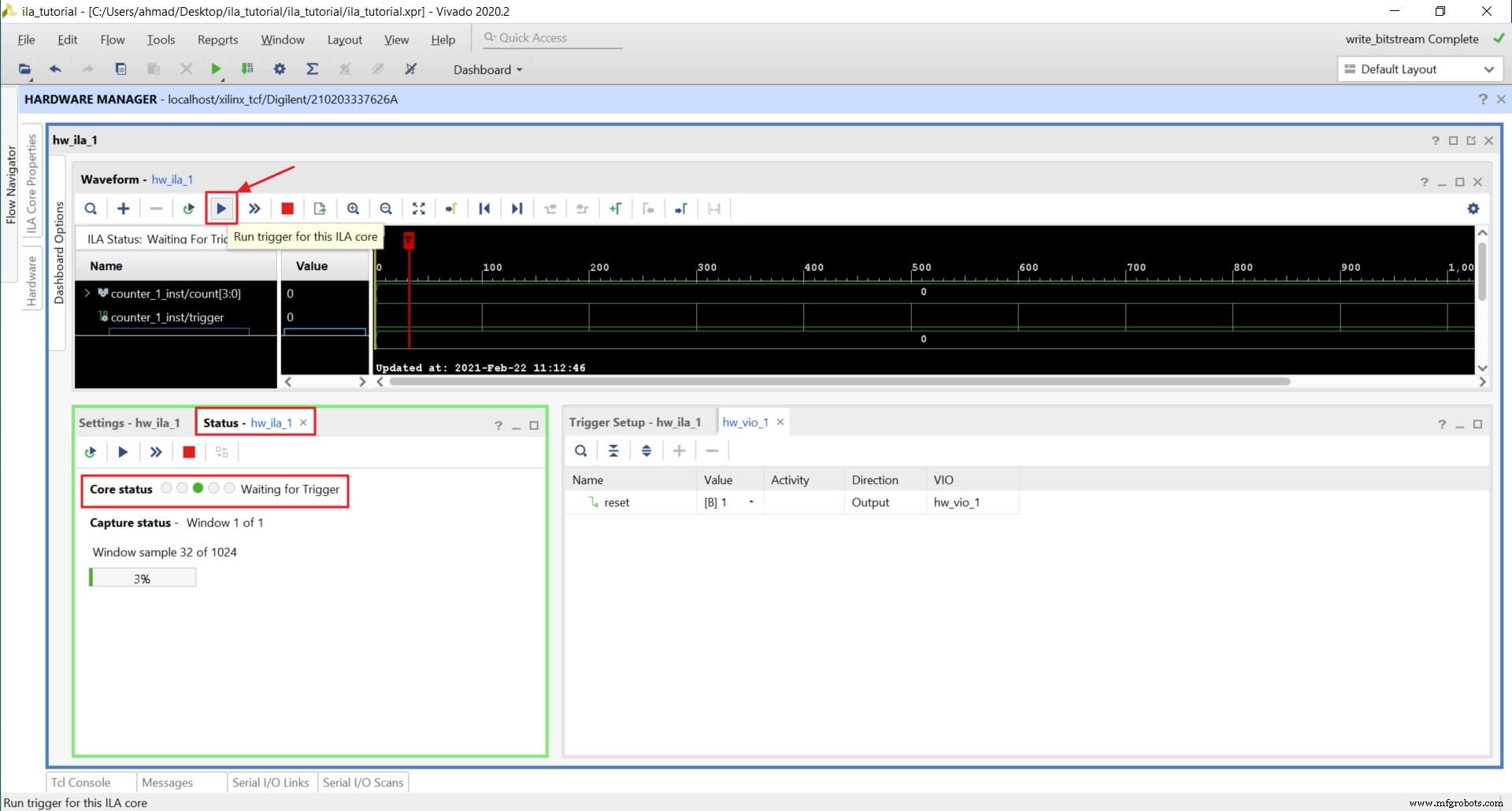

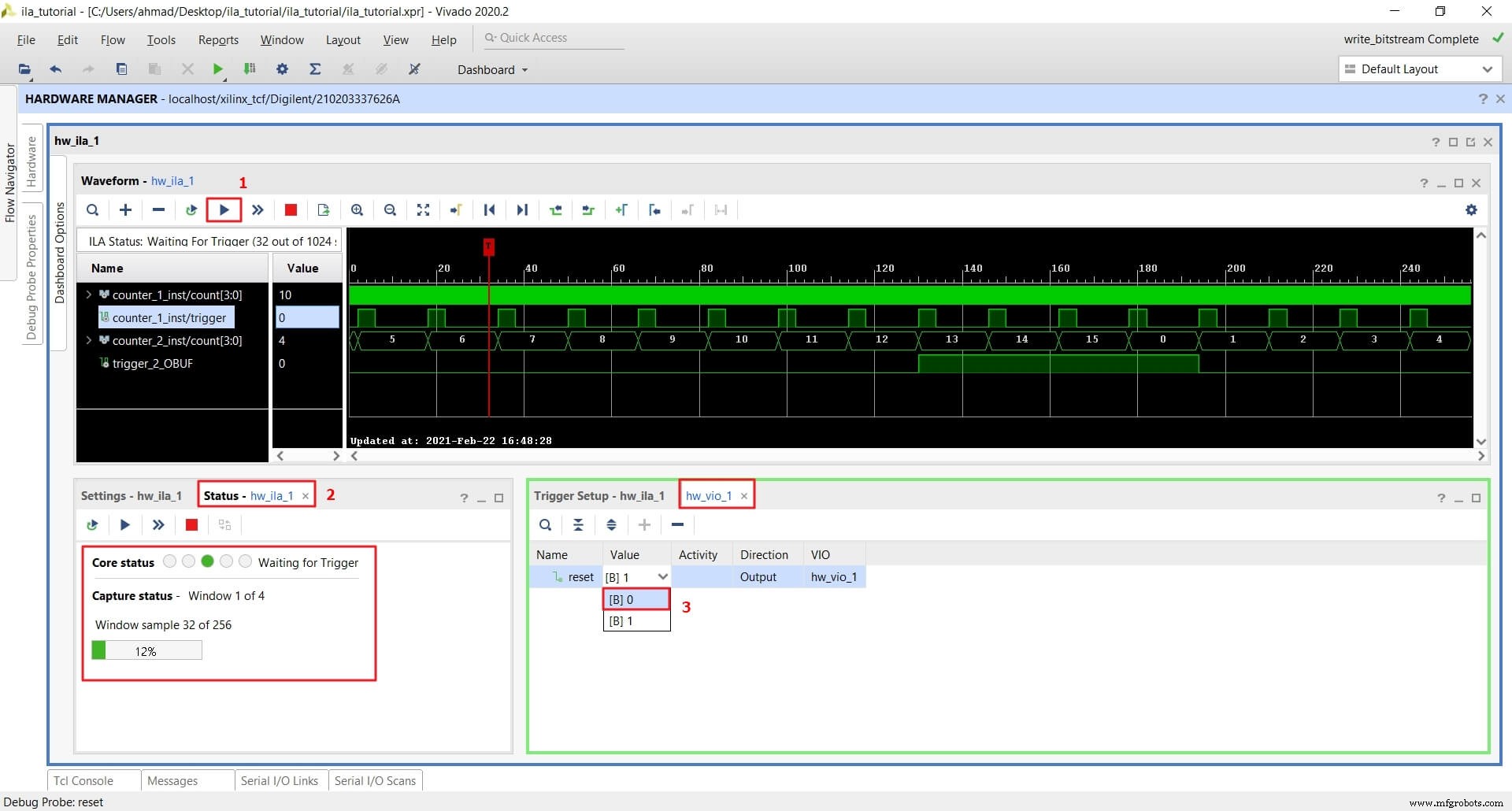

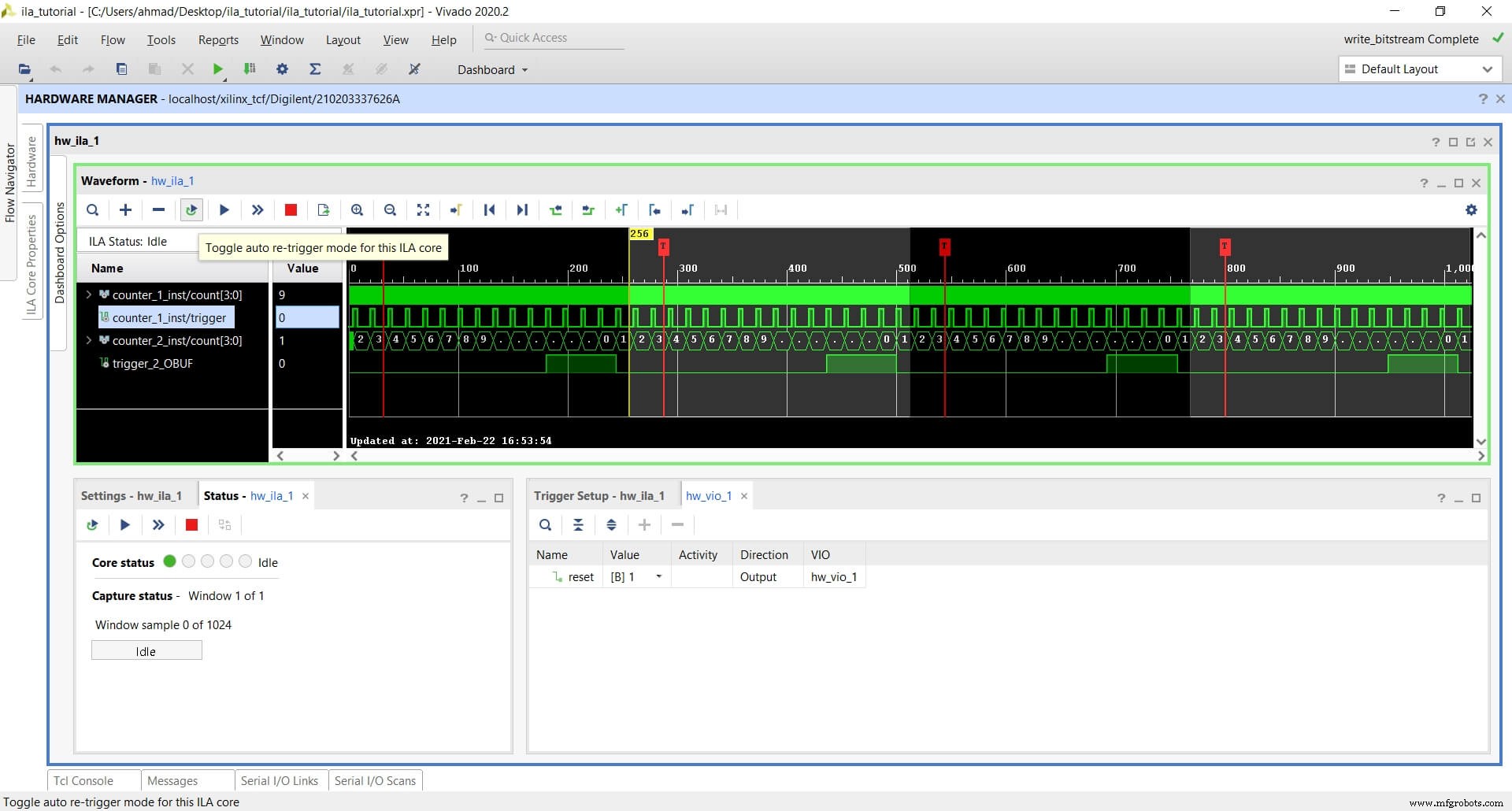

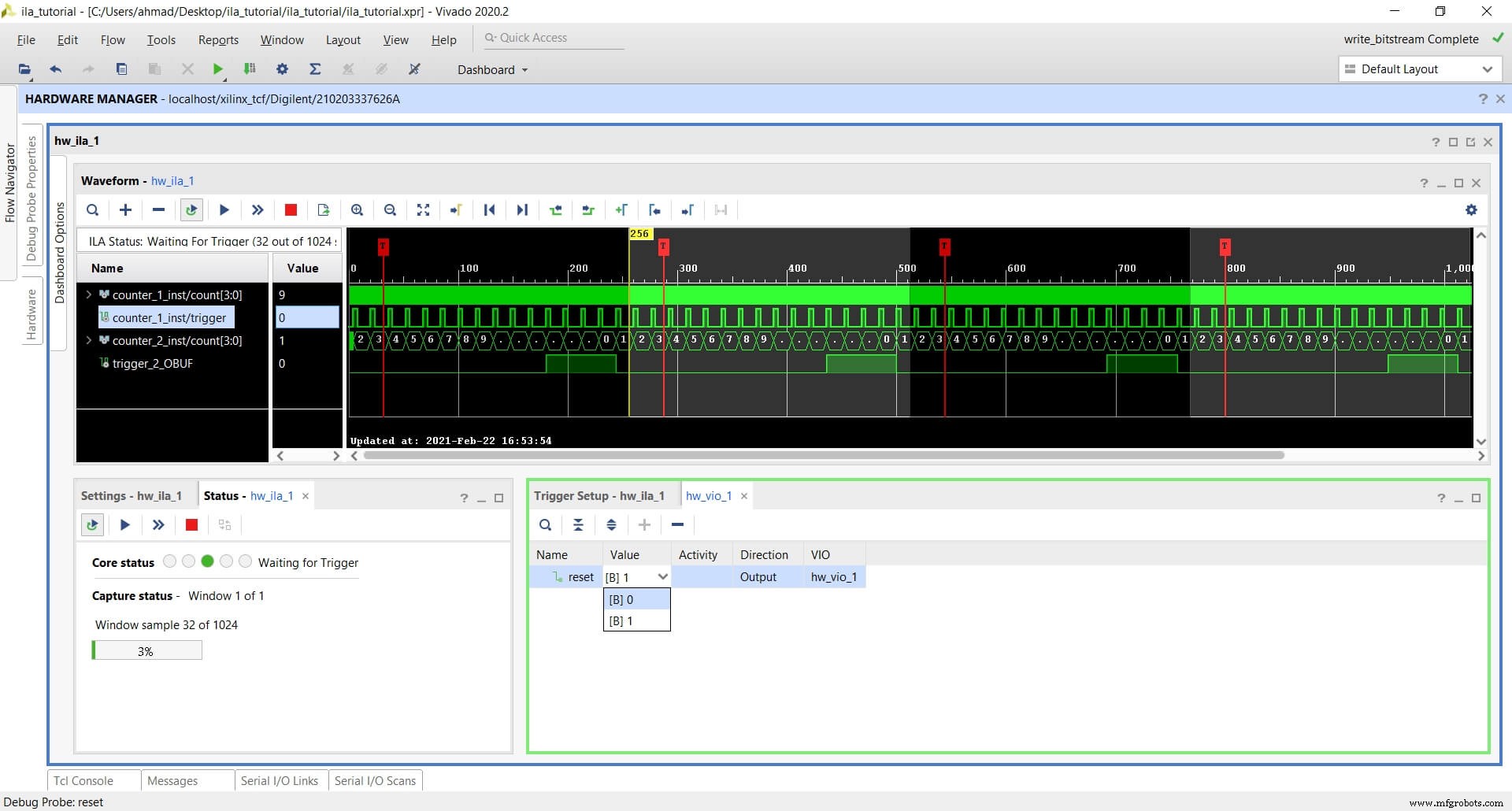

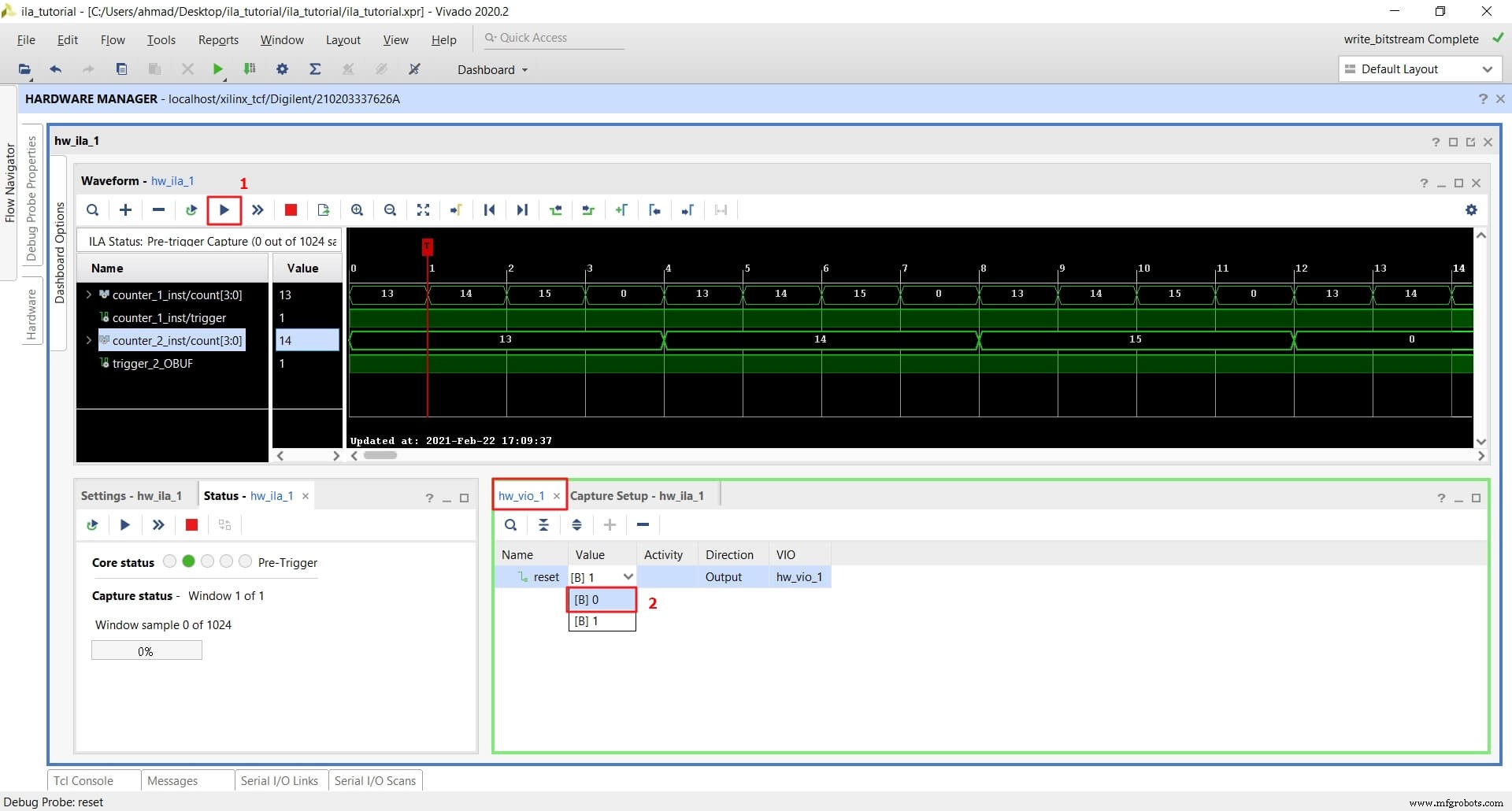

상태 hw_ila_1 창을 클릭합니다. . 핵심 상태가 유휴임을 알 수 있습니다. 무장한 방아쇠가 없기 때문입니다. 트리거 실행을 클릭합니다. 버튼을 누르면 트리거가 작동합니다.

이제 핵심 상태가 트리거 대기 중으로 변경되었음을 알 수 있습니다. . 재설정으로 높음, 트리거 신호(포트 트리거)에 대한 활동이 없습니다. counter_1_inst의 ), ILA가 기다리고 있습니다.

이제 재설정 을 변경해 보겠습니다. 0으로 카운터가 작동하도록 합니다.

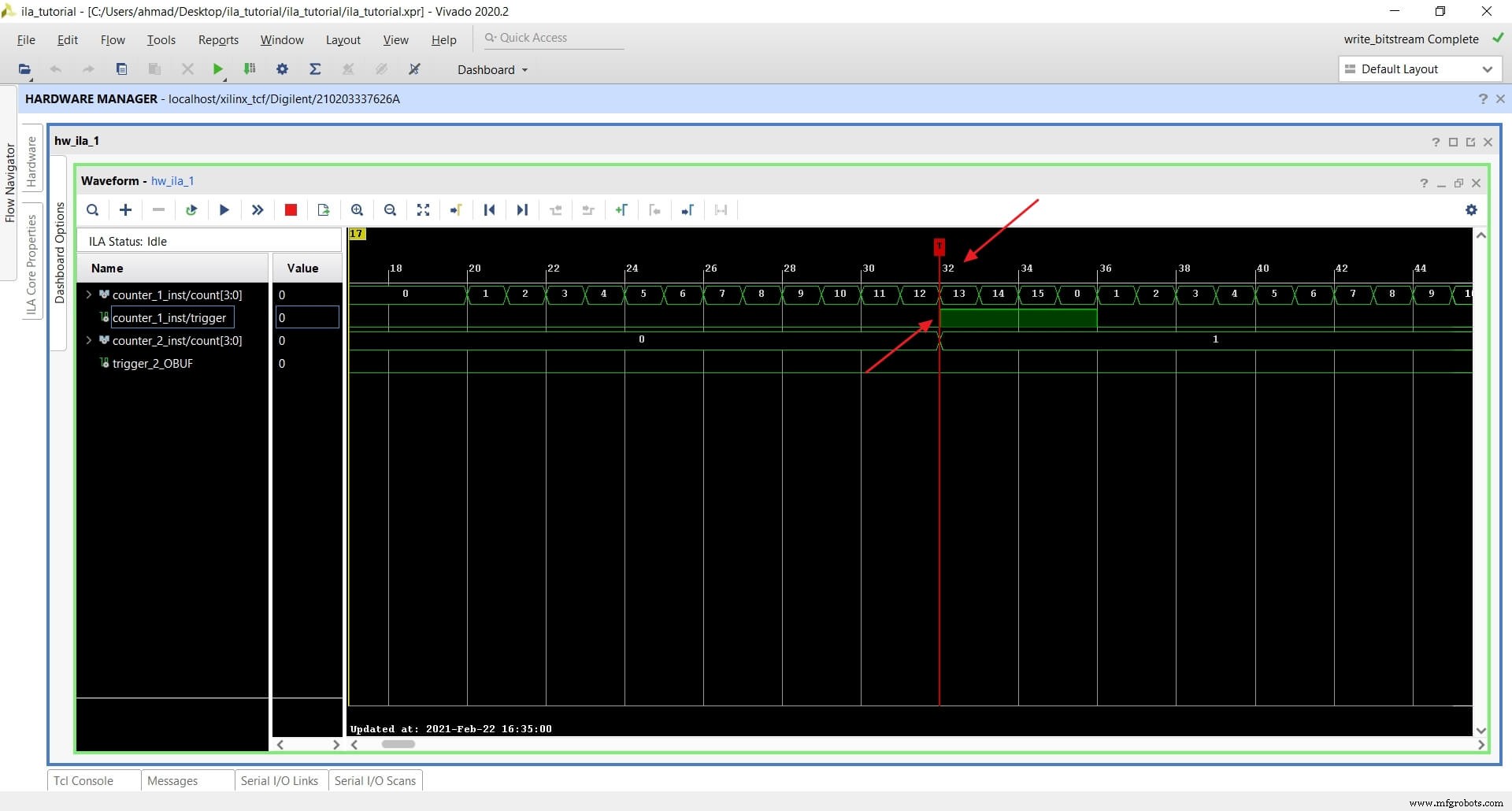

이제 ILA가 트리거되어 샘플을 기록했으며 핵심 상태가 다시 유휴로 변경되었음을 알 수 있습니다. .

트리거 신호의 상승 에지(포트 trigger counter_1_inst의 ) 및 위치 32에 있습니다. . 또한 신호가 카운트 올바르게 작동하고 신호 counter_1_inst/trigger 12와 15 사이의 4개 클럭 사이클 동안 하이입니다(출력은 1클럭 사이클만큼 지연됨).

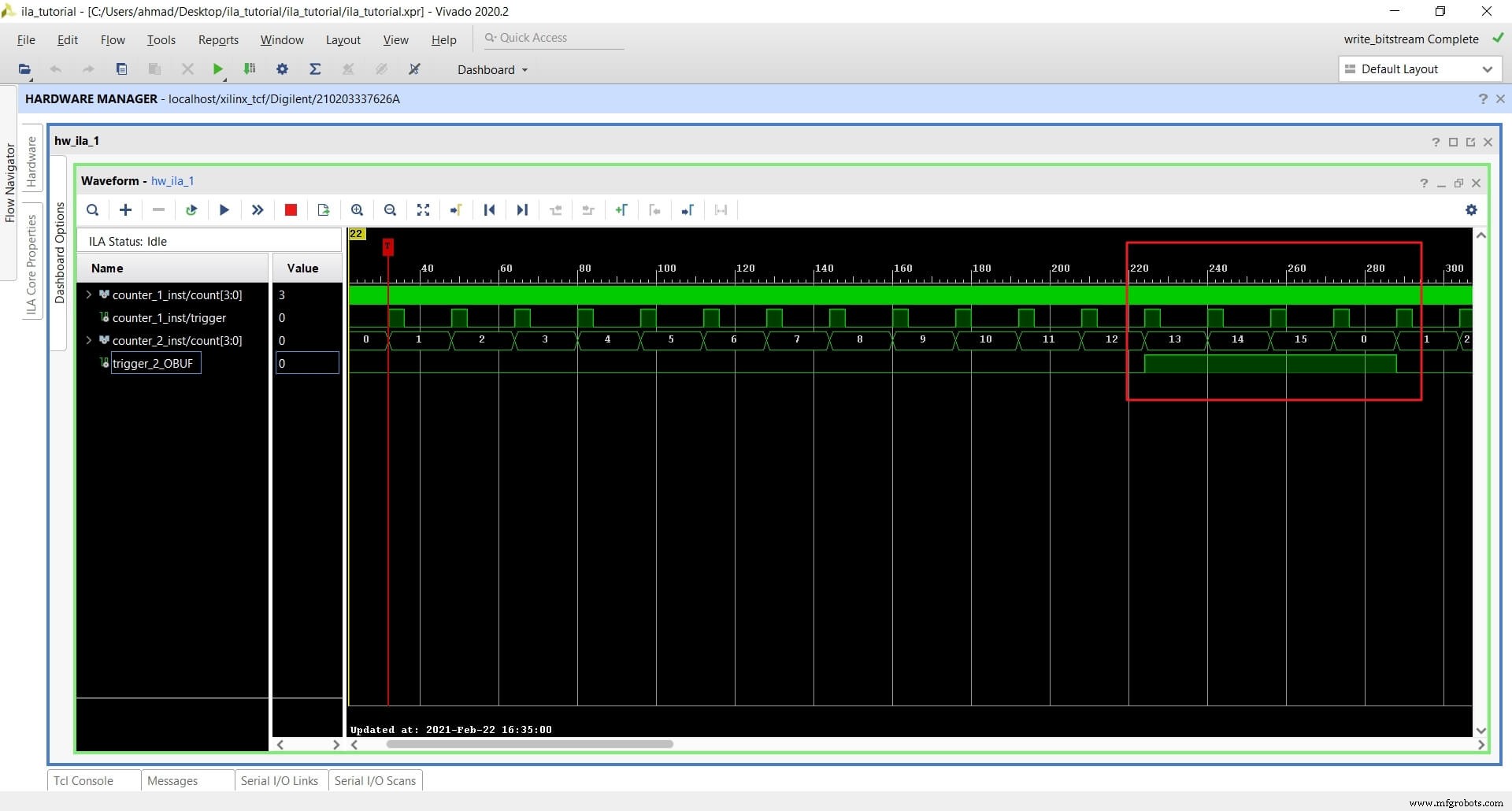

약간 축소하면 count 동작도 확인할 수 있습니다. 및 트리거 counter_2_inst 신호 .

복잡하거나 고급 상태에 대한 트리거 조합을 사용할 수 있습니다. 동일한 파형에서 여러 개의 분리된 시간 프레임을 캡처하기 위해 반복적으로 실행되는 여러 트리거를 사용할 수 있습니다.

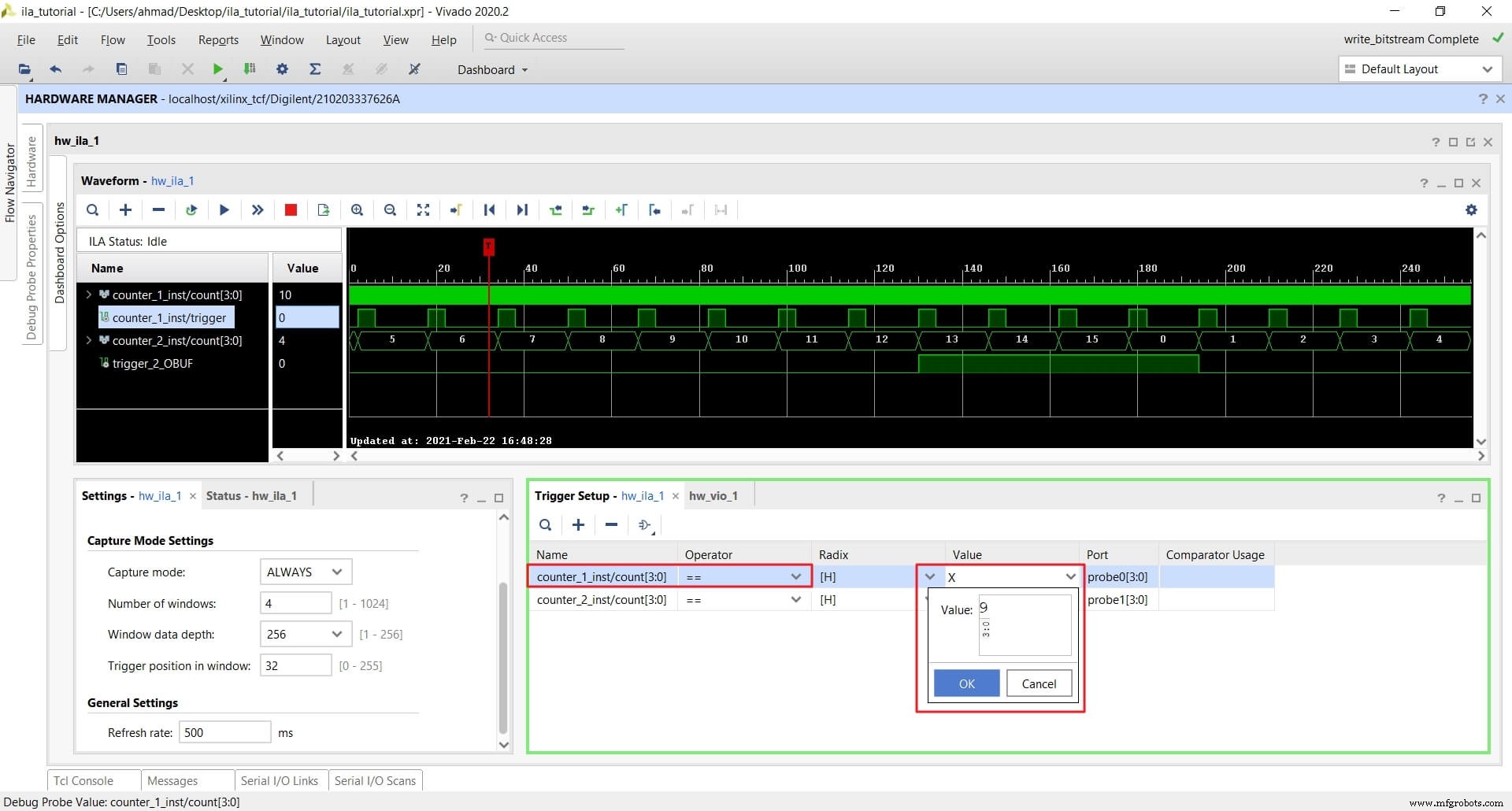

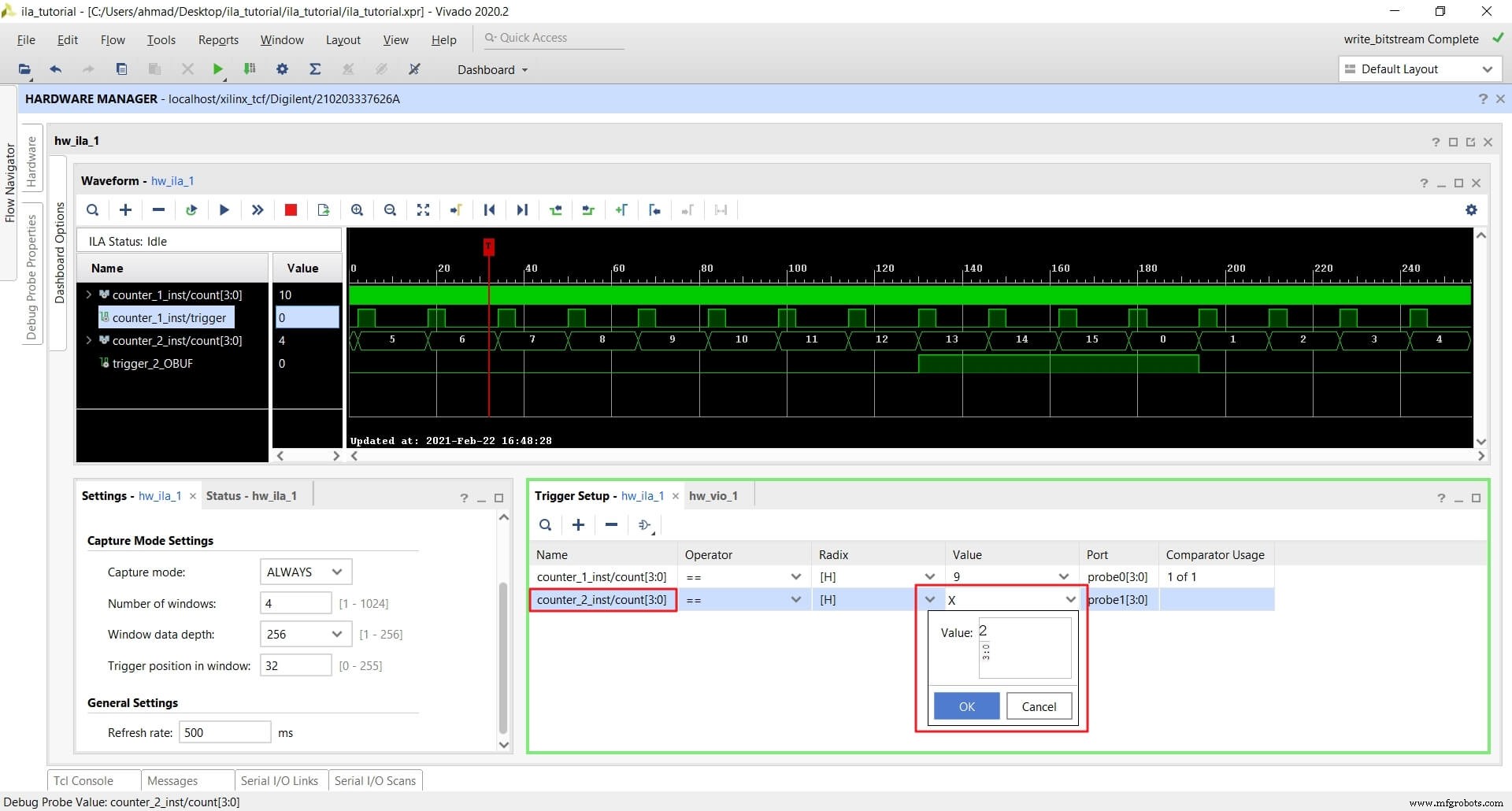

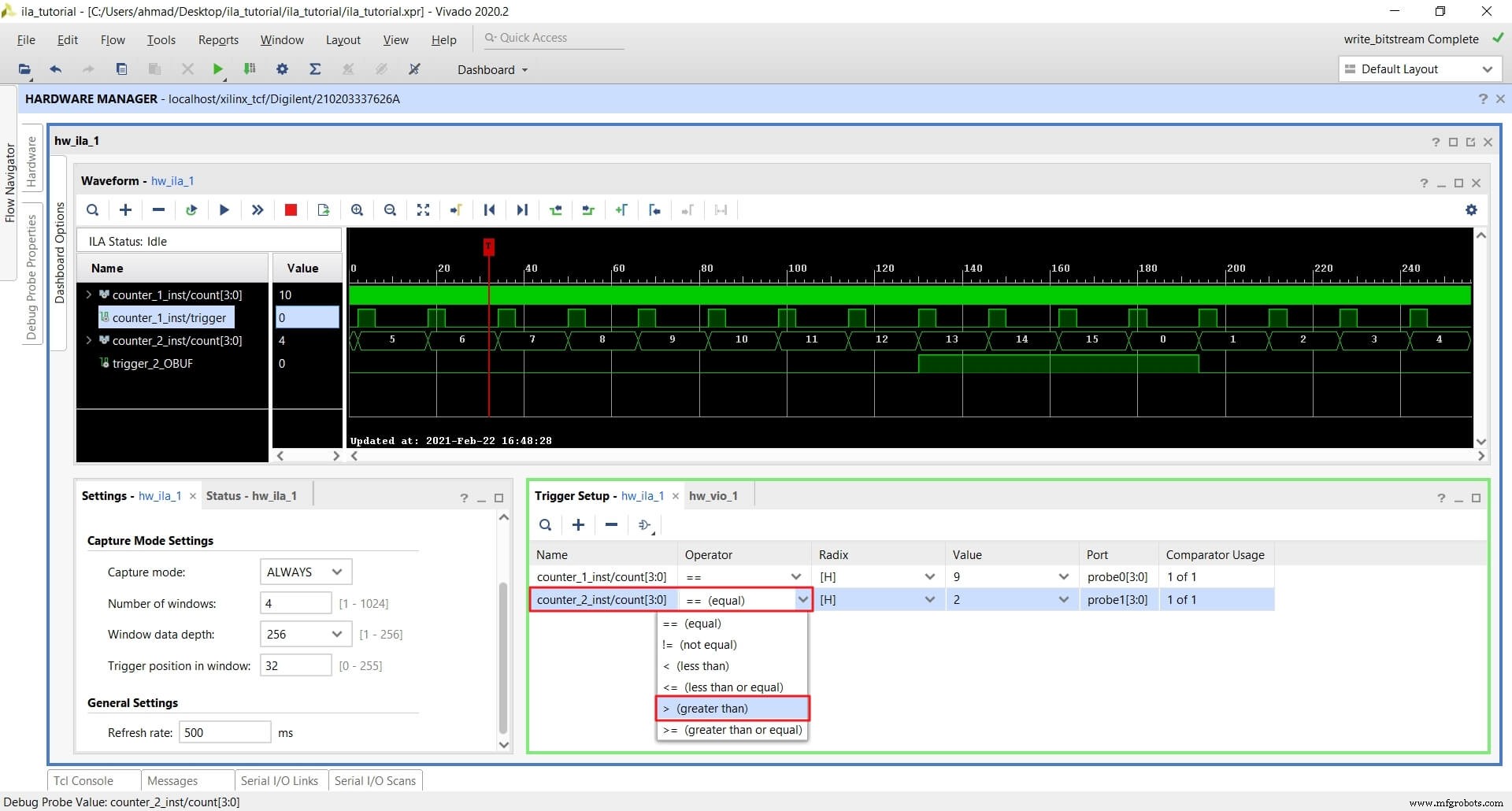

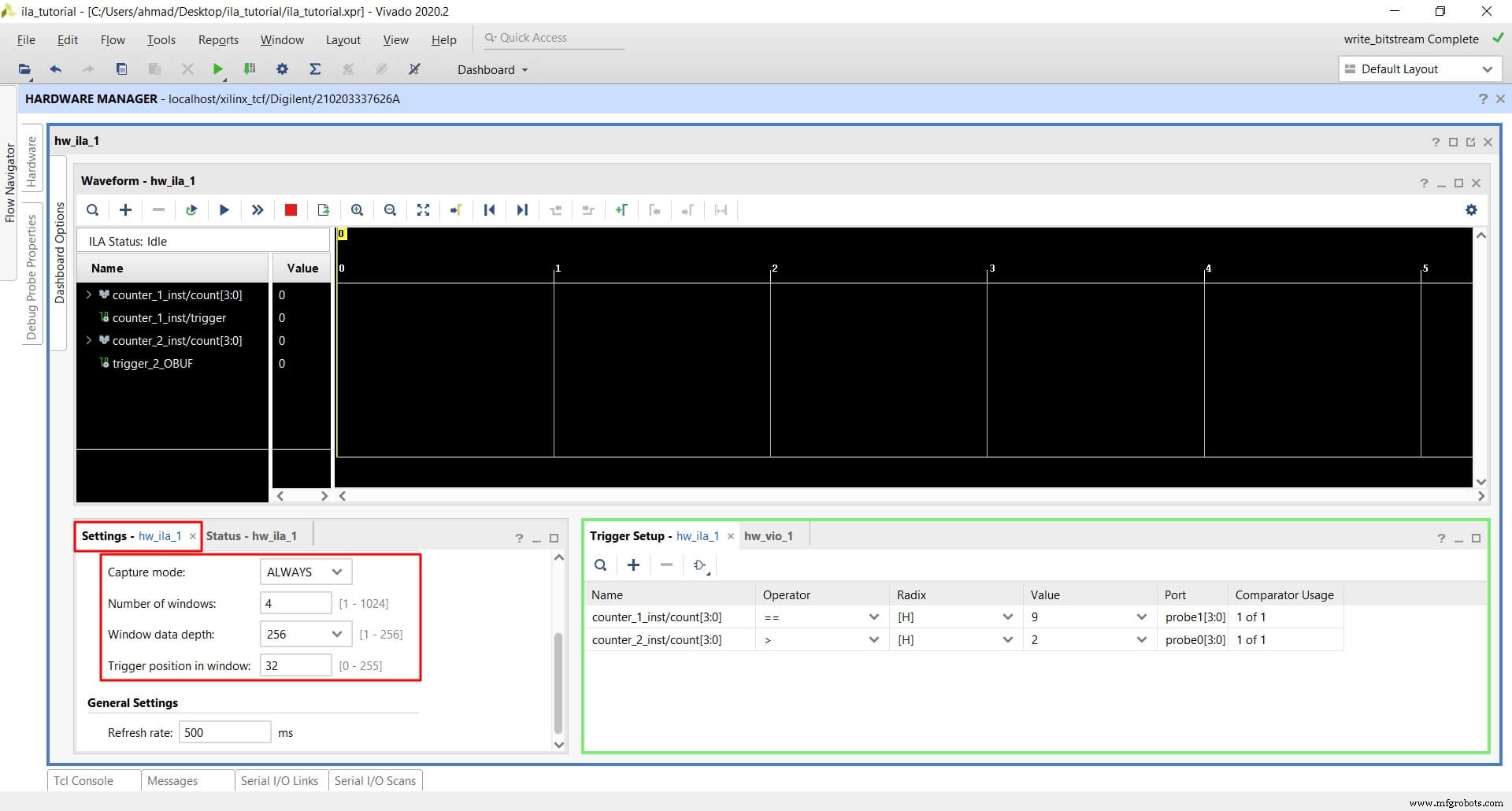

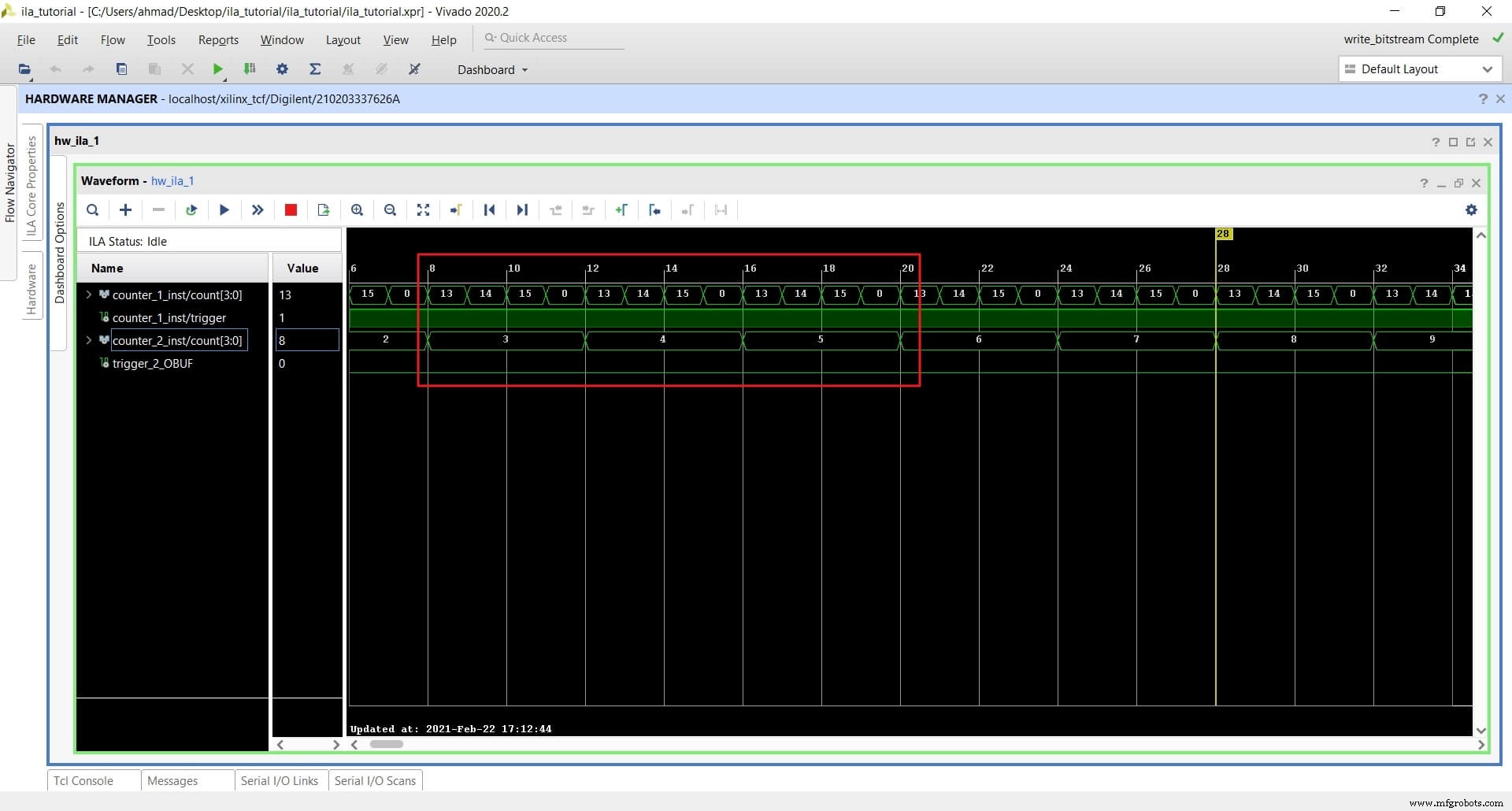

예를 들어 카운트 counter_1_inst의 신호 9(count ==9)이고 count 일 때 counter_2_inst의 신호 2보다 큽니다(개수> 2). 그렇게 하고 FIFO를 4개의 시간 창으로 분할하려면 다음 단계를 따르십시오.

재설정 변경 0으로 돌아가기 vio_reset에서 .

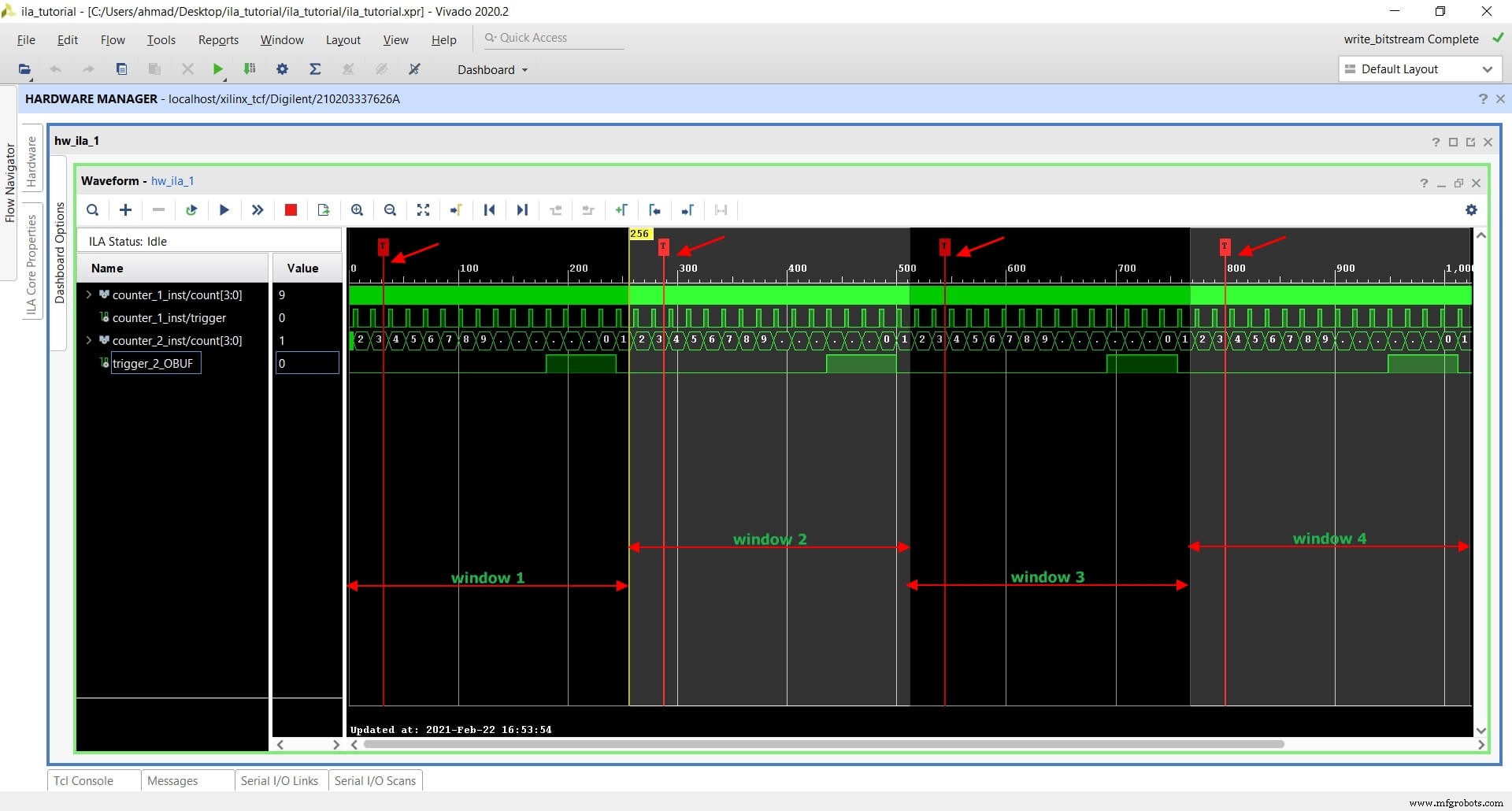

파형 창을 최대화합니다. We see now that we have four windows and a trigger associated with each window. Notice that these windows are independent and not continuous.

The ILA waits for the trigger event to happen, and when it does, the ILA uses the first window to record 256 samples. It then immediately waits for the next trigger until all the windows are full.

ILA has a nice feature called Auto re-trigger that will automatically arm the trigger after it gets triggered. It is useful when monitoring events that occur seldom and you want to run a test overnight. Or you can use it when the trigger happens so often and fast that you cannot arm the trigger manually to capture the samples repeatedly.

Let us assume that the output port trigger of counter_2_inst gets asserted every 3 hours, and you want to record the data each time it happens. To use the Auto trigger, follow these steps:

We can see now that the waveform window is getting refreshed and updated as the trigger happen. It is fast, but the behavior is noticeable.

Click on Stop trigger and toggle Auto re-trigger .

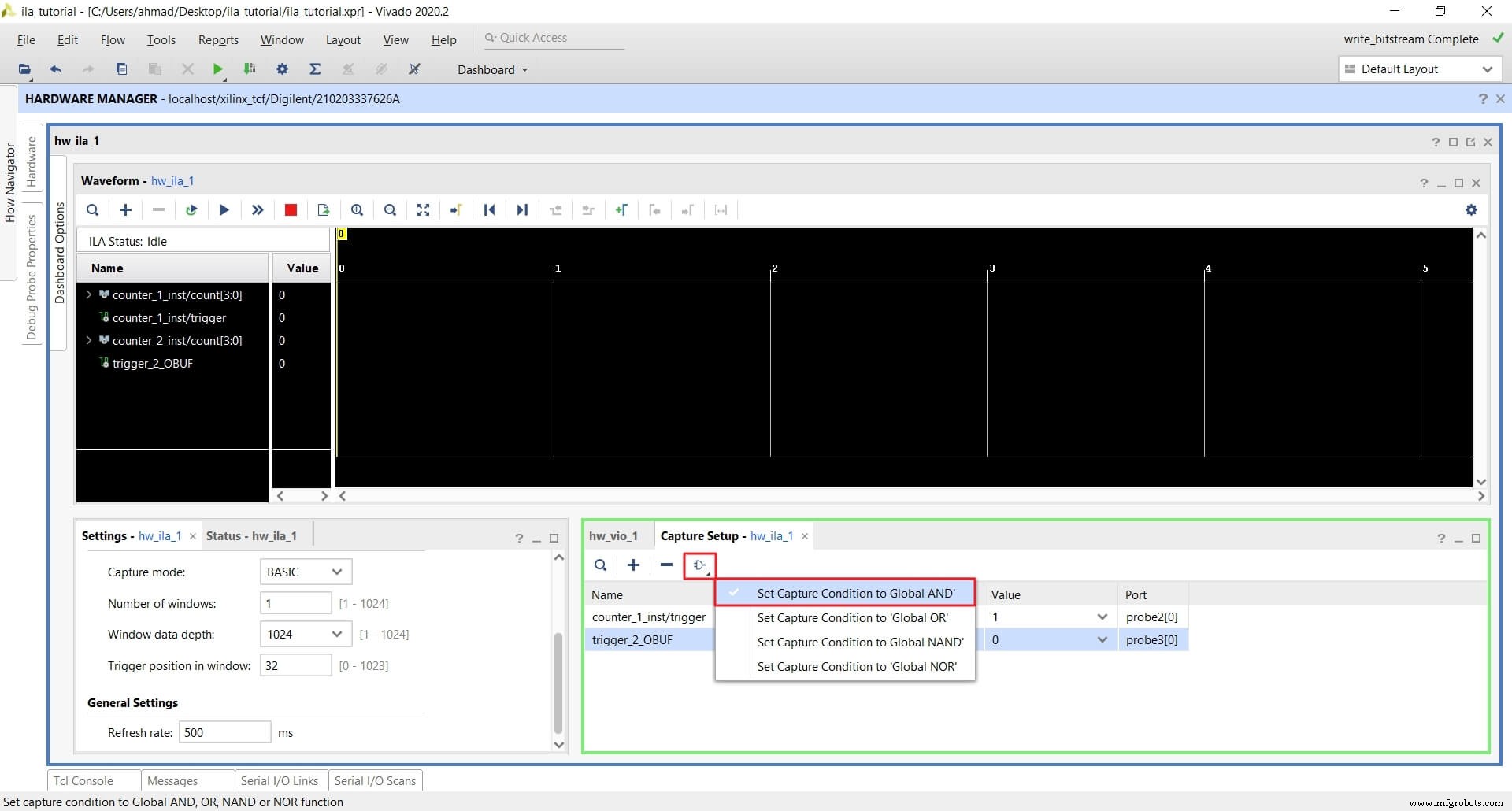

Another feature of ILA is the Capture mode . In some cases, you are not interested in recording all the data but rather capture a specific sample. Capture mode helps you filter out data and record only the samples you are interested in.

Let’s say we are only interested in sampling when the output port trigger of counter_1_inst is ‘1’ AND the output port trigger of counter_2_inst is ‘0’.

To use Capture mode to achieve this, follow these steps:

As we can see from the image below, the waveform has only recorded data when counter_1_inst’s count signal is 13, 14, 15, or 0. Any other counts are filtered out because counter_1_inst/trigger is high on these counts only.

In this tutorial, we learned about ILA and VIO and different use-cases for them. ILA and VIO are excellent options for on-chip debugging. They are free, easy to use, flexible, scalable, and simple yet offer advanced features. The use of multiple triggers and Capture mode helps you achieve a complex debugging scheme.

VHDL

노트북, 휴대폰, 냉장고, 텔레비전, 컴퓨터 등 우리가 일상적으로 사용하는 거의 모든 전자 제품은 모두 복잡하거나 단순한 회로로 제조됩니다. 우리가 사용하는 전자 회로는 서로 연결된 여러 전자 및 전기 부품으로 구성됩니다. 이러한 연결은 전선을 연결하여 커패시터, 저항기, 트랜지스터, 다이오드, 인덕터, 다이오드 등에 전류가 흐르도록 함으로써 이루어집니다. 회로는 연결, 제조 공정, 크기 및 신호와 같은 특정 기준에 따라 여러 유형으로 분류할 수 있습니다. 사용. 이 기사는 회로에서 사용되는 신호에 초점을 맞추고 디지털 집적 회로

RoboDK의 Raspberry Pi 버전은 산업용 로봇과 교육용 로봇 사용자 모두에게 놀라운 애플리케이션을 제공합니다! Raspberry Pi는 놀라운 도구입니다. 이전에 Raspberry Pi에 대해 들어본 적이 없다면 기본적으로 임베디드 애플리케이션을 개발하는 데 사용할 수 있는 작은 컴퓨터입니다. 지난 7년 동안 많은 취미 애호가와 교육 기술 사용자가 즐겨 찾는 개발 보드가 되었습니다. 그러나 라즈베리파이는 교육만을 위한 것이 아닙니다. 2019년 모델(3B+) 출시 이후 산업용 애플리케이션에도 진출하고 있다. 이제 누