VHDL

VHDL의 generate 문은 동일한 신호, 프로세스 및 인스턴스가 있는 클로저에 코드 블록을 자동으로 복제할 수 있습니다. 연결된 프로세스 또는 모듈 인스턴스를 생성할 수 있는 아키텍처 영역에 대한 for 루프입니다.

프로세스나 하위 프로그램에만 존재할 수 있는 일반적인 for 루프와 달리 생성 문은 VHDL 파일의 아키텍처 영역에 직접 배치됩니다. 제네릭과 함께 사용하면 설계 전반에 걸쳐 재사용이 가능한 맞춤형 VHDL 모듈을 설계하기 위한 강력한 도구가 됩니다.

생성 문의 구문은 다음과 같습니다.

[label :] for <constant_name> in <range> generate

[declarations_local_to_each_loop_iteration]

[begin]

<processes_and_instantiations>

end generate [label];

대괄호로 묶인 부분은 선택 사항입니다. 따라서 선언적 영역과 begin을 생략할 수 있습니다. 로컬 객체를 선언하지 않으려면 키워드를 사용하세요. <범위> 자리 표시자는 to을 사용하여 표준 정수 범위를 나타냅니다. 또는 downto .

생성 문을 시작하기 전에 이 기사 전체에서 예제로 사용할 간단한 모듈을 제시하겠습니다. 단일 스위치 입력을 디바운싱할 수 있는 디바운서입니다.

모든 클록 속도에서 사용할 수 있도록 timeout_cycles라는 일반 입력을 추가했습니다. . 이 상수는 스위치 입력이 변경된 후 타임아웃이 몇 클럭 사이클이 될 것인지를 지정합니다. 디바운서는 타임아웃 기간 동안 스위치 값의 추가 변경을 무시합니다.

아래 목록은 debouncer의 엔티티를 보여줍니다. 기준 치수. 탄력 있는 스위치가 있습니다. 입력하고 깨끗한 switch_debounced가 있습니다. 출력.

entity debouncer is

generic (

timeout_cycles : positive

);

port (

clk : in std_logic;

rst : in std_logic;

switch : in std_logic;

switch_debounced : out std_logic

);

end debouncer;

디바운서 모듈은 시간 초과 기간을 달성하기 위해 정수 카운터에 의존합니다. 카운터의 길이 신호는 일반 상수를 따릅니다. 이것이 인스턴스화 중에 지정된 시간 초과 기간이 하는 일입니다.

switch_debounced 값을 읽어야 하기 때문에 내부적으로 출력할 때 debounced라는 이름의 섀도우 신호를 선언했습니다. , 우리는 그 자리에 사용할 것입니다. inout를 설정하는 다른 옵션보다 더 깨끗한 솔루션입니다. switch_debounce 모드 엔티티에서.

마지막으로 아래 코드와 같이 단일 프로세스에서 디바운싱 동작을 구현합니다.

architecture rtl of debouncer is

signal debounced : std_logic;

signal counter : integer range 0 to timeout_cycles - 1;

begin

-- Copy internal signal to output

switch_debounced <= debounced;

DEBOUNCE_PROC : process(clk)

begin

if rising_edge(clk) then

if rst = '1' then

counter <= 0;

debounced <= switch;

else

if counter < timeout_cycles - 1 then

counter <= counter + 1;

elsif switch /= debounced then

counter <= 0;

debounced <= switch;

end if;

end if;

end if;

end process;

end architecture;

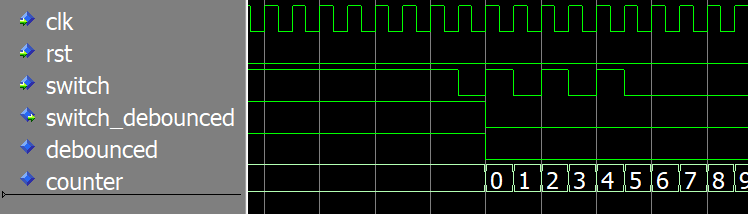

아래 파형은 디바운스 시뮬레이션을 보여줍니다. ModelSim의 모듈. switch_debounced 출력은 스위치를 따릅니다. 입력하지만 첫 번째 변경 후 즉각적인 튀는 동작을 무시합니다. 신호를 디바운스합니다.

아래 양식을 사용하여 이 기사에서 VHDL 코드를 다운로드하십시오. 이메일 주소를 입력하면 테스트벤치와 빠른 실행 스크립트가 포함된 전체 ModelSim 프로젝트가 포함된 Zip 파일을 받게 됩니다. VHDLwhiz에서 향후 업데이트를 받게 되며 언제든지 구독을 취소할 수 있습니다.

스위치 배열에 대한 디바운서를 만들기 위해 생성 문을 사용하여 1비트 디바운서 모듈의 여러 인스턴스를 만들 것입니다.

아래 목록은 새로운 어레이 또는 벡터 디바운서 모듈의 엔티티를 보여줍니다. 1비트 디바운서와 유사하지만 추가 일반 입력이 있습니다. switch_count . 생성할 디바운서 모듈의 인스턴스 수를 지정합니다. 각 스위치마다 하나씩 있어야 합니다.

또한 스위치 입력 및 출력의 이름을 복수 버전으로 변경했으며 이제 단일 비트가 아닌 벡터입니다.

entity debouncer_gen_inst is

generic (

switch_count : positive;

timeout_cycles : positive

);

port (

clk : in std_logic;

rst : in std_logic;

switches : in std_logic_vector(switch_count - 1 downto 0);

switches_debounced : out std_logic_vector(switch_count - 1 downto 0)

);

end debouncer_gen_inst;

아키텍처에서는 이제 generate 문을 사용할 차례입니다. "루프"라는 단어를 "생성"이라는 단어로만 대체하여 일반 for 루프처럼 작동합니다. 그러나 일반 for 루프와 달리 모듈 인스턴스화를 포함할 수 있습니다.

for 루프는 컴파일 시간에 실행되고 각 반복마다 debouncer 모듈의 인스턴스 하나를 생성합니다. 그러나 "i" 상수는 각 반복마다 다르기 때문에 아래와 같이 디바운서의 입력 및 출력을 스위치 벡터의 개별 비트에 매핑하는 데 사용할 수 있습니다.

architecture rtl of debouncer_gen_inst is

begin

MY_GEN : for i in 0 to switch_count - 1 generate

DEBOUNCER : entity work.debouncer(rtl)

generic map (

timeout_cycles => timeout_cycles

)

port map (

clk => clk,

rst => rst,

switch => switches(i),

switch_debounced => switches_debounced(i)

);

end generate;

end architecture;

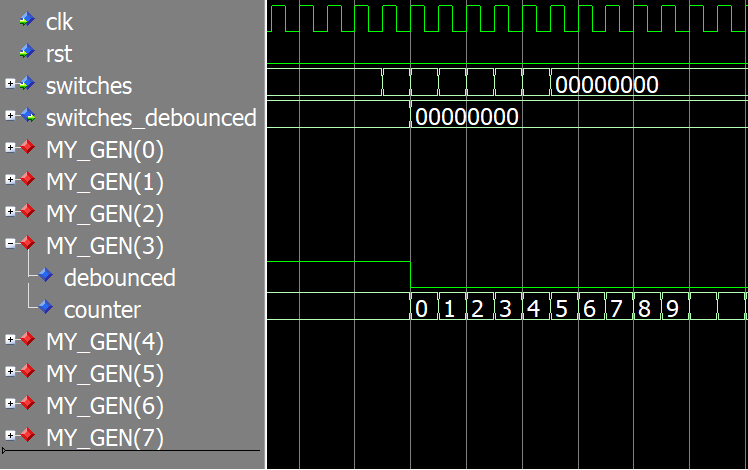

생성 문에 레이블을 지정하는 것은 선택 사항이지만 그렇게 하는 것이 현명할 수 있습니다. 레이블은 시뮬레이터 계층 구조와 합성 로그에 표시되어 디버깅 시 특정 인스턴스를 더 쉽게 식별할 수 있습니다.

아래 파형은 벡터 디바운서의 시뮬레이션을 보여줍니다. 여기에서 "MY_GEN" 레이블이 다시 나타나고 8개의 디바운서 인스턴스 각각에 대해 인덱스가 추가된 것을 볼 수 있습니다.

이 테스트벤치는 스위치 번호 3 입력만 변경합니다. 이것이 파형에서 볼 수 있는 것이며 제가 MY_GEN(3) 그룹만 확장한 이유입니다.

ModelSim이 설치된 경우 컴퓨터에서 이 예제를 빠르게 실행할 수 있습니다. 아래 양식을 사용하여 소스 코드와 ModelSim 프로젝트를 다운로드하세요!

이 기사의 마지막 예에서 우리는 생성 문을 사용하여 일련의 동일한 프로세스를 만들 것입니다. 1비트 디바운서 모듈의 인스턴스를 만드는 대신 VHDL 코드를 가져왔습니다. 엔티티는 이전 예와 동일하고 동작도 동일하지만 구현이 다릅니다.

생성 문 내에서 DEBOUNCE_PROC 프로세스를 이동하고 아래 코드에서 약간 변경한 것을 볼 수 있습니다. 이번에는 generate 문 내에서 두 개의 로컬 신호를 선언합니다. debounced 및 카운터 .

for 루프를 반복할 때마다 신호와 프로세스의 추가 복사본이 생성됩니다. 프로세스 내에서 이러한 신호 이름을 사용하면 해당 특정 루프 반복의 인클로저로 범위가 지정된 것을 참조합니다.

마지막으로 디바운스된 std_logic switches_debounced의 올바른 비트에 신호 프로세스 위의 동시 명령문을 사용하여 모듈 출력.

architecture rtl of debouncer_gen_proc is

begin

MY_GEN : for i in 0 to switch_count - 1 generate

signal debounced : std_logic;

signal counter : integer range 0 to timeout_cycles - 1;

begin

switches_debounced(i) <= debounced;

DEBOUNCE_PROC : process(clk)

begin

if rising_edge(clk) then

if rst = '1' then

counter <= 0;

debounced <= switches(i);

else

if counter < timeout_cycles - 1 then

counter <= counter + 1;

elsif switches(i) /= debounced then

counter <= 0;

debounced <= switches(i);

end if;

end if;

end if;

end process;

end generate;

end architecture;

시뮬레이션 파형은 모듈 인스턴스화를 사용한 이전 예제와 정확히 동일하기 때문에 생략했습니다. 동작은 동일합니다.

아래 양식을 사용하여 모든 코드를 다운로드할 수 있습니다. 이메일 주소를 입력하면 VHDLwhiz의 업데이트를 구독하게 됩니다. 하지만 걱정하지 마세요. 제가 보내는 모든 이메일에는 수신 거부 링크가 있습니다.

공유할 문 생성에 유용한 또 다른 응용 프로그램이 있으면 아래에 의견을 남겨주세요! ?

VHDL

Python에서 조건문이란 무엇입니까? Python의 조건문은 특정 부울 제약 조건이 true 또는 false로 평가되는지 여부에 따라 다른 계산 또는 작업을 수행합니다. 조건문은 Python에서 IF 문으로 처리됩니다. 이 자습서에서는 Python에서 조건문을 적용하는 방법을 살펴봅니다. If 문이란 무엇입니까? 사용 방법? if 조건이 충족되지 않으면 어떻게 되나요? else 조건 사용 방법 else 조건이 작동하지 않는 경우 elif 조건 사용 방법 최소한의 코드로 조건문을 실행하는 방법 파이썬 중첩 if 문

스위치 및 콘센트 콤보 장치 배선 다이어그램 및 설치 콤보 스위치/콘센트 장치란 무엇이며 어떻게 연결합니까? 콤보 장치는 동일한 인클로저 상자에 있는 스위치와 콘센트의 조합입니다. 내장 스위치를 배선하여 인클로저 상자의 콘센트를 제어할 수 있습니다. 스위치는 스위치가 조명 지점과 같은 추가 부하 지점을 제어하는 점퍼 와이어를 통해 연결할 수도 있습니다. 콤보 장치를 배선 설치하기 전에 콤보 GFCI와 콤보 스위치 콘센트의 기본적인 차이점을 알아야 합니다. 일반 콤보 스위치와 콘센트의 라인 단자에는 파손되지 않은 핀 탭이 있지만