VHDL

VHDL의 변수는 C의 변수와 유사하게 작동합니다. 해당 값은 변수가 수정되는 코드의 정확한 위치에서 유효합니다. 따라서 신호가 before 변수의 값을 사용하는 경우 할당하면 이전 변수 값을 갖게 됩니다. 신호가 after 변수의 값을 사용하는 경우 할당은 새 변수 값을 갖습니다.

변수 규칙:

가장 중요한 것은 변수가 할당된 값을 즉시 취한다는 것입니다. 다음은 변수를 사용하는 한 가지 유용한 방법을 보여주는 예입니다. 임시 사용을 위한 데이터 저장 . case 문과 앰퍼샌드(&) 연결 연산자를 사용합니다.

VAR_CASE : process (i_clk)

variable v_Choices : std_logic_vector(1 downto 0);

begin

v_Choices := i_select_1 & i_select_2; -- concatenation

case v_Choices is

when "00" =>

o_data <= "0001";

when "01" =>

o_data <= "0010";

-- ETC

이전 예에서 두 신호를 연결하여 case 문에서 사용할 수 있도록 했습니다. 변수 v_Choices는 할당되자마자 즉시 사용할 수 있었습니다. 다른 예를 살펴보겠습니다. 아래 예는 더 포괄적이며 변수가 할당 값을 즉시 취하는 방법을 보여줍니다. r_Var_Copy1 및 r_Var_Copy2 신호는 동일한 것으로 보이지만 r_Var_Copy2는 재설정되기 전에 5에 도달할 수 없습니다.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_ex is

port (

i_clk : in std_logic;

o_done : out std_logic

);

end variable_ex;

architecture rtl of variable_ex is

signal r_Done : std_logic := '0';

signal r_Var_Copy1 : natural range 0 to 5 := 0;

signal r_Var_Copy2 : natural range 0 to 5 := 0;

begin

EX_VAR : process (i_clk)

variable v_Count : natural range 0 to 5 := 0;

begin

if rising_edge(i_clk) then

v_Count := v_Count + 1;

r_Var_Copy1 <= v_Count;

if v_Count = 5 then

r_Done <= '1';

v_Count := 0;

else

r_Done <= '0';

end if;

r_Var_Copy2 <= v_Count;

end if;

end process EX_VAR;

o_done <= r_Done;

end rtl;

설계를 시뮬레이션하려면 테스트벤치를 만들어야 합니다. 또한 변수는 시뮬레이션에 표시하기가 약간 까다로울 수 있습니다. Modelsim을 사용하는 경우 Modelsim의 파형 창에서 변수를 보는 방법에 대해 자세히 알아보세요.

테스트벤치:

library ieee;

use ieee.std_logic_1164.all;

entity variable_ex_tb is

end variable_ex_tb;

architecture behave of variable_ex_tb is

component variable_ex

port (

i_clk : in std_logic;

o_done : out std_logic

);

end component variable_ex;

constant c_CLK_PERIOD : time := 10 ns;

signal r_CLK : std_logic := '0';

signal w_DONE : std_logic;

begin

UUT : variable_ex

port map (

i_clk => r_CLK,

o_done => w_DONE

);

r_CLK <= not r_CLK after c_CLK_PERIOD/2;

end behave;

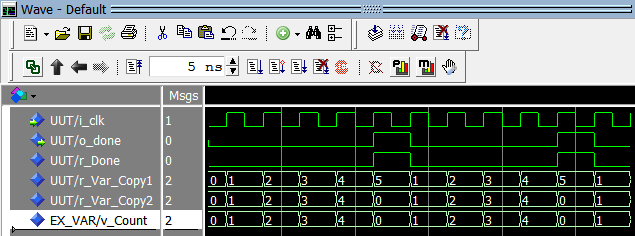

변수 예제 테스트 벤치 파형

변수 예제 테스트 벤치 파형 위의 예는 변수가 신호와 어떻게 다르게 작동하는지 보여줍니다. r_Var_Copy1 및 r_Var_Copy2 신호는 동일한 것으로 보이지만 r_Var_Copy2는 재설정되기 전에 5에 도달할 수 없습니다.

VHDL

파이썬에서 변수란 무엇입니까? Python 변수는 값을 저장하기 위해 예약된 메모리 위치입니다. 즉, 파이썬 프로그램의 변수는 처리를 위해 컴퓨터에 데이터를 제공합니다. Python 변수 유형 Python의 모든 값에는 데이터 유형이 있습니다. Python의 다양한 데이터 유형은 Numbers, List, Tuple, Strings, Dictionary 등입니다. Python의 변수는 어떤 이름이나 a, aa, abc 등과 같은 알파벳으로도 선언할 수 있습니다. 이 튜토리얼에서는 다음을 배울 것입니다. 변수 선언 및 사용 방

사용자 정의 매크로는 FANUC가 시스템 변수라고 부르는 것을 통해 많은 CNC 관련 기능에 대한 액세스를 제공합니다. 이 데이터에는 다음이 포함됩니다. 입력/출력 신호(외부 장치와 통신) 오프셋(오프셋 레지스터에 대한 읽기 및 쓰기) 알람 및 메시지 표시(프로그램이 오류를 감지하면 CNC 알람 생성) 조작자 패널 기능에 대한 액세스(단일 블록, 이송 보류 및 이송 속도 오버라이드 활성화/비활성화) 시간/날짜 및 시계 타이머(시간 이벤트) 액세스 현재 모달 상태에 대한 액세스(모드 결정/변경) 현재 축 위치에 대한 액세스(프로브