임베디드

Cadence Design Systems는 10억 게이트 SoC(System-on-Chip) 설계 검증을 위한 가장 빠르고 최고 성능의 실리콘 이전 하드웨어 디버그 및 소프트웨어 검증을 제공하는 차세대 에뮬레이션 및 프로토타이핑 시스템을 출시했습니다.

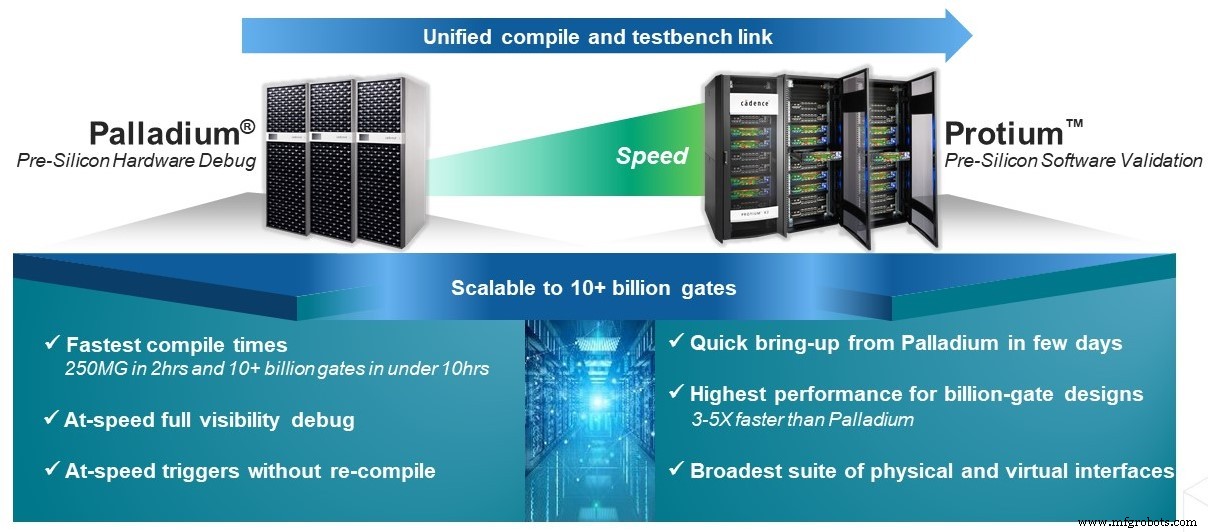

통합 컴파일러 인터페이스와 공통 디버그 인터페이스 및 테스트벤치 콘텐츠를 통해 새로운 Palladium Z2 엔터프라이즈 에뮬레이션 및 Protium X2 엔터프라이즈 프로토타이핑 시스템은 고객에게 이전 제품에 비해 2배 용량 및 1.5배 향상된 성능을 제공하여 더 큰 칩에서 더 많은 검증 주기를 실행할 수 있도록 합니다. 더 적은 시간에. Cadence는 두 시스템 모두 Palladium Z2 시스템에서는 10시간 이내에, Protium X2 시스템에서는 24시간 이내에 100억 개의 게이트를 컴파일할 수 있는 획기적인 모듈식 컴파일 기술도 제공한다고 말했습니다.

스마트 검증 애플리케이션을 포함한 광범위한 Cadence 검증 제품군의 일부인 Palladium Z2 / Protium X2 조합의 핵심은 통합 컴파일러 인터페이스입니다. 원활하게 통합된 흐름, 통합 디버그, 공통 가상 및 물리적 인터페이스, 시스템 전반에 걸친 테스트벤치 콘텐츠를 통해 두 시스템은 에뮬레이션에서 프로토타이핑에 이르기까지 신속한 설계 마이그레이션 및 테스트를 제공합니다. 확장 가능한 용량은 모바일, 소비자 및 하이퍼스케일 컴퓨팅 설계를 포함하여 가장 진보된 애플리케이션을 위해 설계하는 사람들이 직면한 문제를 해결하도록 설계되었음을 의미합니다.

케이던스의 폴 커닝햄(Paul Cunningham)은 “고급 SoC 설계에 대한 사전 실리콘 검증을 위해서는 최고의 성능과 신속한 예측 가능한 디버그를 모두 제공하는 수십억 게이트 용량의 솔루션이 필요하다”고 말했다. 시스템 및 검증 그룹의 수석 부사장 겸 제너럴 매니저는 “우리의 새로운 동적 듀오는 두 개의 긴밀하게 통합된 시스템, 즉 신속하게 예측 가능한 하드웨어 디버그에 최적화된 Palladium Z2 에뮬레이션과 수십억 달러의 최고 성능을 위해 최적화된 Protium X2 프로토타이핑을 통해 이러한 요구 사항을 충족합니다. 게이트 소프트웨어 검증. 우리는 고객의 강한 관심에 흥분하고 있으며 고객과 협력하여 이러한 새로운 시스템을 활용하여 설계에서 최고의 검증 처리량을 달성할 수 있기를 기대합니다.”

초기 고객은 공통 프런트 엔드 검증 처리량의 이점에 대해 언급했습니다. Nvidia의 하드웨어 엔지니어링 수석 이사인 Narendra Konda는 다음과 같이 말했습니다. Cadence Palladium Z2 및 Protium X2 시스템의 공통 프론트 엔드 흐름을 사용하여 검증, 검증 및 사전 실리콘 소프트웨어 가동 간의 작업 부하 분산을 최적화하고 있습니다. 2배의 가용 용량, 50% 더 높은 처리량, 더 빠른 모듈식 컴파일러 턴어라운드를 통해 우리는 가장 정교한 GPU 및 SoC 설계를 일정에 따라 종합적으로 검증할 수 있습니다."

한편 Arm의 디자인 서비스 수석 이사인 Tran Nguyen은 “동급 최고의 에뮬레이션이 우리 성공의 열쇠이며 Arm은 Arm 기반 서버의 시뮬레이션과 함께 에뮬레이션을 광범위하게 사용하여 최고의 검증 처리량을 달성합니다. 새로운 Cadence Palladium Z2 시스템을 통해 우리는 최신 설계에 대해 성능이 최대 50% 향상되고 용량이 2배 향상되어 차세대 IP 및 제품을 검증하는 데 필요한 강력한 사전 실리콘 기능을 제공하게 되었습니다.”

이전 제품과 마찬가지로 Palladium Z2 및 Protium X2는 표준 랙 구성으로 제작되었으며 데이터 센터 내부에 설치되고 엔지니어 데스크에서 액세스할 수 있습니다. 개별 설계에 실제로 필요한 용량에 따라 둘 다 동시에 많은 설계를 처리할 수 있습니다. 공유할 수 있는 세분성은 시스템 내부의 개별 칩에 있으며 두 시스템 모두 확장되어 각 개별 칩을 다른 설계에 병렬로 사용할 수 있습니다.

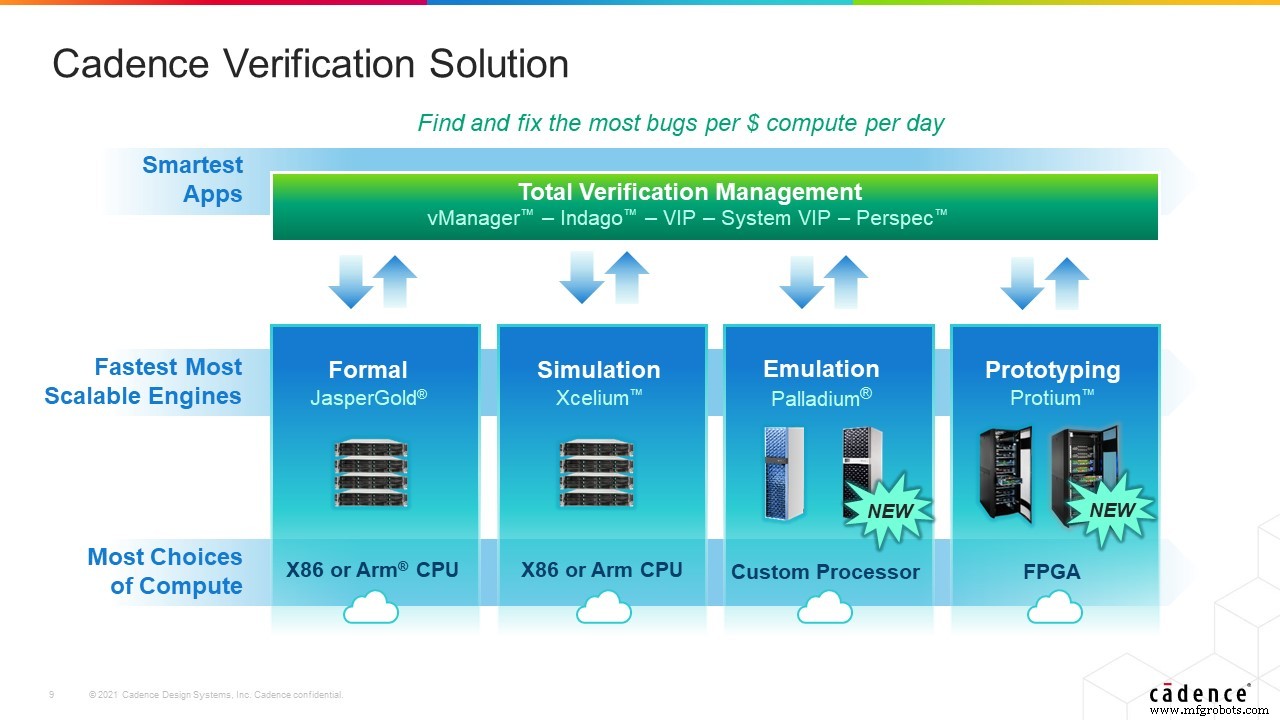

<울>회사에 따르면 Palladium Z2 에뮬레이션, Protium X2 프로토타이핑, Xcelium 로직 시뮬레이션, JasperGold 공식 검증 플랫폼 및 스마트 검증 애플리케이션의 Cadence 제품군을 포함한 Cadence 검증 전체 흐름은 하루에 달러당 버그의 검증 처리량이 가장 높습니다.

임베디드

새로운 하이브리드 데이터 흐름 및 Von Neumann 아키텍처는 다음을 포함한 워크로드를 가속화할 수 있습니다. 신경망, 기계 학습, 컴퓨터 비전, DSP 및 기본 선형 대수 하위 프로그램. 실리콘 밸리의 신생 기업인 Quadric은 로봇, 공장 자동화 및 의료 영상과 같은 에지 장치를 위한 AI 및 표준 컴퓨터 비전 알고리즘 워크로드를 모두 가속화하도록 설계된 가속기를 구축했습니다. 회사의 하드웨어 아키텍처는 신경망, 기계 학습, 컴퓨터 비전, DSP 및 기본 선형 대수 하위 프로그램을 포함한 워크로드를 처리할 수 있는 새로운

배터리 관리 시스템(BMS)이 전원 설계에서 어떤 역할을 하는지, 기본 기능에 어떤 구성요소가 필요한지에 대한 높은 수준의 기본 사항을 알아보세요. 오늘날 리튬 이온 배터리는 최대 265Wh/kg의 에너지 밀도를 자랑합니다. 그러나 그들은 과도한 스트레스를 받으면 때때로 모든 에너지를 폭발시키고 태우는 것으로 유명합니다. 이것이 종종 배터리 관리 시스템(BMS)을 제어하여 배터리 관리 시스템을 요구하는 이유입니다. 이 기사에서는 BMS 개념의 기본 사항에 대해 논의하고 일반적인 BMS를 구성하는 몇 가지 기본 요소를 살펴보겠습니