임베디드

이 스타트업의 에너지 효율적인 칩은 M.2를 목표로 합니다. 데이터 센터에서 과속 추천 모델을 위한 가속기 소켓.

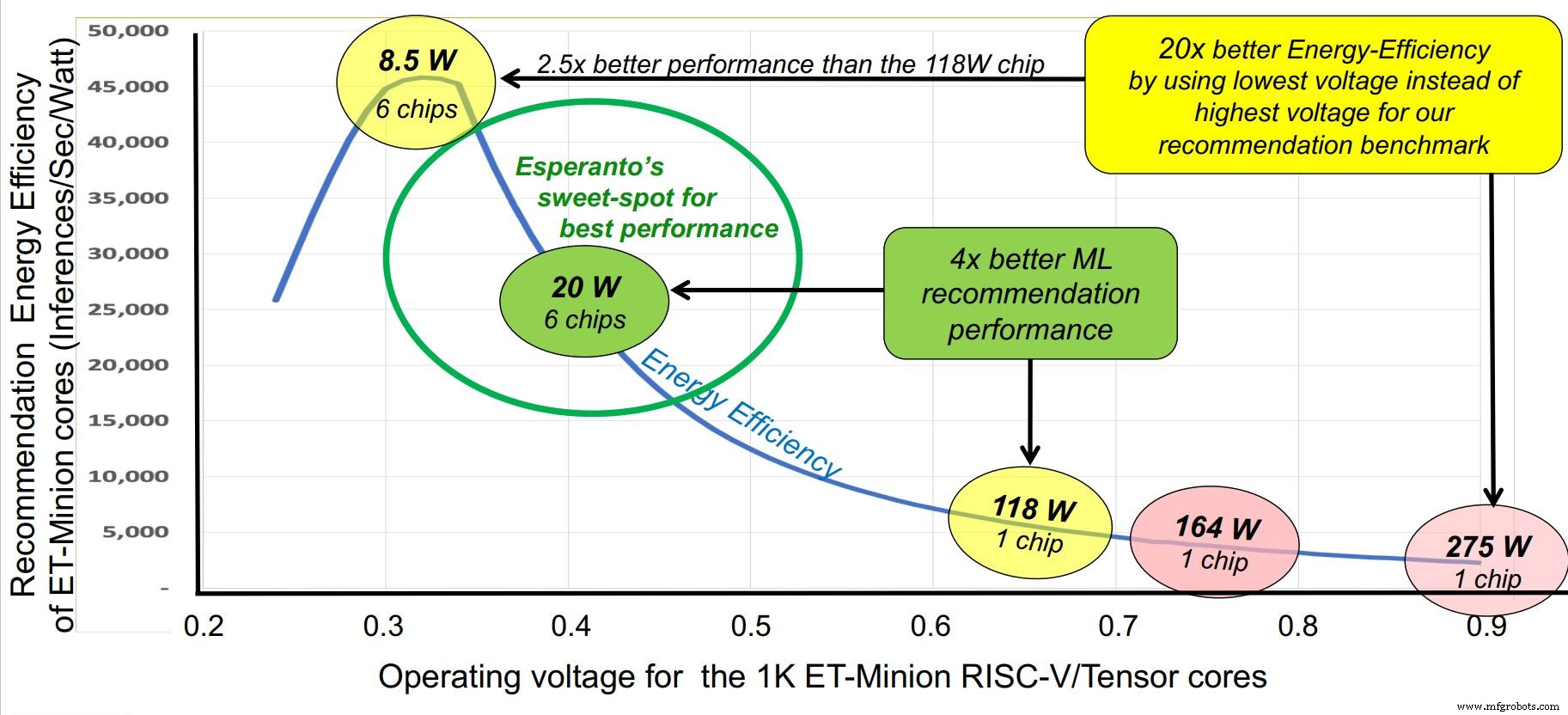

Hot Chips 컨퍼런스와 함께 이번 주에 신생업체 Esperanto가 현재까지 최고 성능의 상용 RISC-V 칩으로 스텔스 모드에서 벗어났습니다. 이 칩은 초대형 데이터 센터용으로 설계된 천 코어 AI 가속기입니다. 칩은 10~60W 사이의 다양한 전압 및 전력 프로필에서 실행될 수 있지만 "스위트 스팟"은 칩당 20W의 전력으로, Glacier Point 가속기 카드에 6개의 칩을 탑재할 수 있는 구성입니다. 총 소비량은 120W 미만입니다. 6개 칩의 총 성능은 약 800TOPS입니다.

에스페란토의 ET-SoC-1은 단일 칩에 구축된 가장 많은 RISC-V 코어(1,093)를 가진 것으로 청구됩니다. 여기에는 에너지 효율적인 AI 가속 엔진 역할을 하는 1,088개의 ET-Minion 맞춤형 RISC-V 코어가 포함됩니다. 4개의 ET-Maxion RISC-V 코어와 RISC-V 서비스 프로세서도 포함되어 있습니다. 전체 디자인은 에너지 효율성에 맞춰져 있습니다.

Hot Chips보다 앞서, EE Times 업계 베테랑인 Dave Ditzel, 에스페란토의 창립자이자 집행 회장과 이야기를 나눴습니다. (Ditzel의 자격 증명에는 David Patterson과 함께 1980년에 출판된 "The Case for Reduced Instruction Set Computer"라는 획기적인 논문의 공동 저작이 포함됩니다.)

"우리는 단일 칩에 1000개의 RISC-V 코어를 탑재한 최초의 기업입니다."라고 Ditzel이 말했습니다. “사람들은 수년 동안 많은 코어 CPU에 대해 이야기했지만 우리는 많이 보지 못했습니다. 시중에 나와 있는 대부분의 RISC-V는 임베디드용입니다.

"우리는 'RISC-V가 하이엔드를 할 수 있다는 것을 보여주자... 우리는 정말 노련한 CPU 디자이너가 여기서 할 수 있는 것을 보여주겠다'고 말했습니다."

고객 요구 사항

Ditzel의 CPU 설계 팀은 대규모 데이터 센터 운영자의 요구 사항에 대한 세부 정보를 알아낼 수 있었습니다.

"그들은 훈련 칩을 원하지 않았고 훈련에 문제가 없었습니다."라고 Ditzel이 말했습니다. AI 교육은 종종 오프라인 문제이며 하이퍼스케일러의 거대한 x86 CPU 용량이 항상 최대 로드에 있는 것은 아닙니다. 따라서 해당 용량은 사용 가능한 경우 교육에 사용할 수 있습니다. "그들의 진짜 문제는 추론입니다."라고 Ditzel이 덧붙였습니다. “그게 바로 그들의 광고를 이끄는 것입니다. 10밀리초 이내에 답변이 필요합니다.”

따라서 온라인 광고를 위한 추천 추론 엔진을 가속화하는 것이 데이터 센터 칩의 초점이 되었습니다. 이러한 유형의 모델을 가속화하기 위한 하이퍼스케일러의 요구 사항은 상당히 명시적이었습니다.

"우리 고객은 100MB의 메모리 온칩을 원했습니다. 추론으로 원하는 모든 작업은 100MB에 맞습니다."라고 그는 말했습니다. 고객들은 또한 오프칩 메모리를 위한 외부 인터페이스를 원했습니다. Ditzel은 "진짜 문제는 가속기 카드를 얼마나 잡을 수 있느냐는 것입니다."라고 설명했습니다. “카드를 칩이 아니라 컴퓨팅 단위로 생각하십시오. 카드에 메모리가 있으면 PCIe 버스를 통해 호스트로 가는 것보다 훨씬 빠르게 액세스할 수 있습니다."

전체 크기 이미지를 보려면 클릭하세요.

Esperanto는 각각 하나의 칩이 있는 6개의 듀얼 M.2 카드를 Glacier Point 가속 카드에 맞춥니다. (출처:에스페란토)

온칩 메모리 시스템에는 L1, L2 및 L3 캐시와 총 100MB가 조금 넘는 레지스터 파일이 있는 전체 주 메모리 시스템이 있습니다. 온카드 메모리 시스템은 약 100GB의 모델에서 대부분의 가중치와 활성화를 저장할 수 있습니다.

권장 모델은 가속화하기 어려운 것으로 악명이 높으며, 이것이 여전히 기존 CPU 서버에서 실행되는 이유 중 하나입니다.

"1억 명의 고객 중에서 최근에 구매한 제품을 고를 때 카드의 메모리에 액세스해야 하며 모든 종류의 임의 메모리 액세스를 수행하므로 캐시가 일하다. 클래식 컴퓨터가 더 필요합니다.”라고 Ditzel이 말했습니다. "x86 서버는 상당한 양의 메모리를 처리하고 프리페칭 기능이 있으며 범용 CPU는 해당 워크로드를 매우 잘 처리합니다. 그래서 어떤 액셀러레이터도 추천 사업에 뛰어들기 어렵다”고 말했다.

또한 FP16 및 FP32 데이터 유형과 함께 INT8에 대한 지원도 필요합니다. 부동 소수점 수학에 대한 요구 사항은 가능한 가장 높은 예측 정확도를 유지해야 할 필요성과 낮은 정밀도 수학을 위해 프로그램을 이식하거나 다시 작성하려는 경향이 부족하기 때문입니다. Ditzel은 주요 x86 서버 칩 제조업체가 최근에야 서버 CPU에 8비트 벡터 확장을 추가했다고 말했습니다.

"[초대형 데이터 센터]에서 백만 x86 서버에서 진행되는 대부분의 추론은 여전히 32비트 부동 소수점입니다."라고 그는 말했습니다.

듀얼 M.2 카드의 에스페란토 칩은 기존 x86 CPU 서버 인프라 내의 가속기 슬롯에 맞도록 설계되었습니다. 그 결과 120W의 전력 제한이 발생하며 공기 냉각이 필요합니다.

Ditzel은 에스페란토의 디자인이 Google TPU나 Amazon Web Services의 Inferentia와 같은 내부 노력과 직접적으로 경쟁하지 않는다고 말했습니다. 하이퍼스케일러는 “전체 커뮤니티가 자신을 위한 가속기 칩을 구축하도록 하려고 합니다. 이들 기업 중 상당수는 오픈 컴퓨팅과 [오픈 컴퓨팅 프로젝트]를 믿습니다.” 따라서 “그들은 OCP 서버를 구입하고 거기에 표준화된 항목을 원합니다. 경쟁이 있다면 그들은 그것을 좋아합니다... 그들은 경쟁을 장려하고 사람들에게 가능한 것을 보여주려고 노력합니다."

그럼에도 불구하고 이 스타트업은 빅 데이터 센터 운영자에게 가속기 칩에 대한 외부 공급업체가 필요하다고 주장합니다. "여전히 구매 대 구매 결정입니다." 예를 들어, 한 에스페란토 고객은 다른 부서에서 사용 중인 내부 개발 칩에 액세스할 수 없었습니다. "그들이 가진 것을 이기면 이 회사들 중 하나에 들어갈 수 있습니다."

새로운 접근 방식

에스페란토는 전력 소모가 큰 경쟁업체의 칩 가속기에 반대 접근 방식을 취하여 여러 가지로 사용할 수 있는 저전력 칩을 제공합니다. 이 접근 방식은 값비싼 HBM에 의존하지 않고도 메모리 I/O에 더 많은 핀을 사용할 수 있으므로 메모리 대역폭 요구 사항을 해결합니다.

에스페란토의 하드웨어도 범용 컴퓨터로 설계되었습니다. Ditzel에 따르면 권장 모델에 중점을 두었음에도 불구하고 이 칩은 병렬 처리를 가속화할 수 있습니다. 6칩 가속기 카드에는 약 6,000개의 병렬 코어가 포함되어 있으며 각 코어는 2개의 스레드를 실행할 수 있으며, 이는 "임의의 문제에서 발생"할 수 있습니다.

에스페란토의 또 다른 속임수는 공격적인 에너지 효율적인 디자인입니다. 고객 요구 사항은 전력 예산을 총 120W로 설정했지만 Glacier Point 카드에 설정된 최대 공간은 칩 6개 또는 칩당 20W였습니다. 이에 비해 AI 추론 가속기는 그 양의 10배 이상 작동합니다.

에스페란토는 여러 각도에서 이 문제를 다루었습니다. 클럭 주파수는 약 1GHz의 최적 수준으로 감소되었습니다. 공급 전압은 SRAM의 한계를 넘어 약 0.4V로 감소했습니다. 스위칭 커패시턴스는 트랜지스터 수를 줄이기 위해 상업적으로 실행 가능한 가장 작은 명령어 세트로 린 RISC-V 코어를 사용하여 지원되었습니다. 고급이지만 안정적인 공정 기술인 TSMC 7nm가 선택되었습니다.

전체 크기 이미지를 보려면 클릭하세요.

Esperanto는 약 1GHz에서 작동하는 "스위트 스팟"을 식별했습니다. (출처:에스페란토)

핵심 디자인

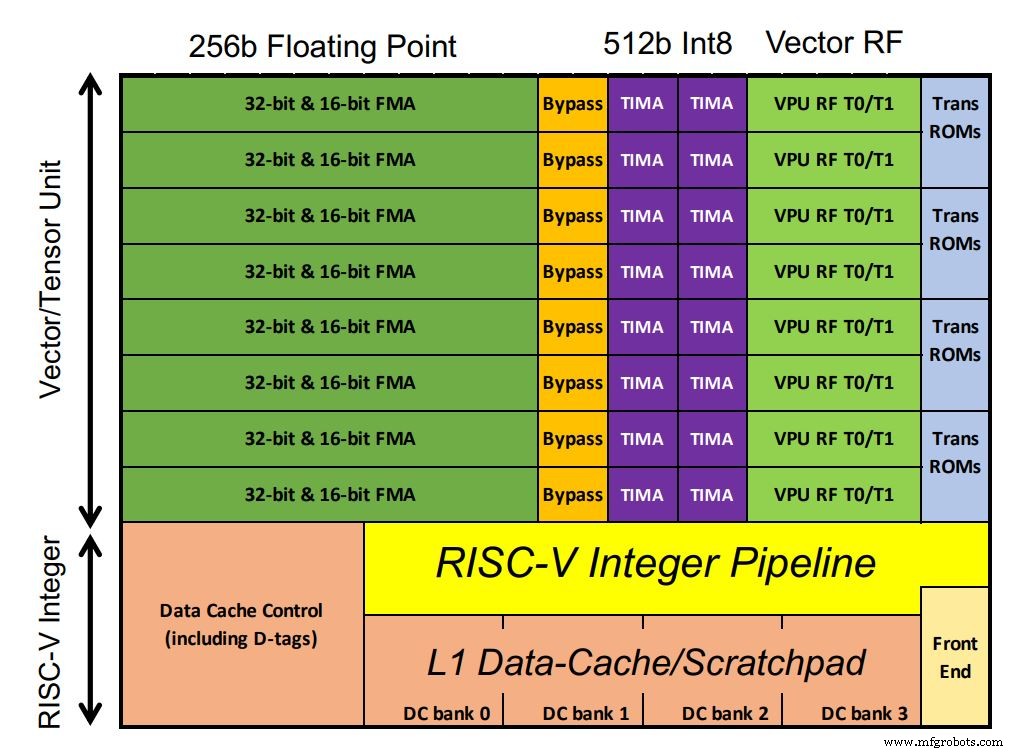

Esperanto의 칩에는 AI 워크로드를 처리하는 1,088개의 ET-Minion 코어가 포함되어 있습니다. 코어는 64비트, 순서대로 RISC-V 프로세서로 Esperanto 자체의 AI 최적화 벡터 및 텐서 유닛이 칩 공간의 많은 부분을 차지합니다. 부동 소수점 MAC이 구성을 지배합니다. 비정상적으로 정수 MAC은 부동 소수점 처리 너비의 두 배입니다(고객 요구 사항에 따라 Ditzel이 언급함). 딥 러닝 모델에서 흔히 볼 수 있는 시그모이드 함수와 같은 벡터 초월 명령어도 지원됩니다. 코어가 단일 저전압 도메인에서 실행되기 때문에 견고한 성능을 보장하기 위해 작은 L1 캐시에서 SRAM과 함께 더 많은 트랜지스터가 사용되었습니다.

전체 크기 이미지를 보려면 클릭하세요.

Esperanto의 칩에는 1,088개의 ET-Minion 코어가 포함되어 있습니다(확대하려면 이미지를 클릭하십시오)(출처:Esperanto)

각 코어는 GHz당 128GOPS가 가능합니다. 맞춤형 다중 주기 텐서 명령어는 전체 512비트 너비를 사용하여 최대 512주기를 인수하고 실행하는 별도의 컨트롤러로 대규모 행렬 곱셈을 수행합니다. 이를 통해 컨트롤러가 다음 RISC-V 명령어를 가져오기 전에 단일 텐서 명령어가 64,000개 이상의 산술 연산을 수행할 수 있습니다. 워크로드의 대부분이 텐서 명령어를 사용하기 때문에 명령어 대역폭이 줄어듭니다. 따라서 512 클록 사이클당 하나의 명령어만 필요합니다.

8개의 ET-Minion 코어는 "이웃"을 구성하고 수정된 명령은 물리적 근접성을 활용합니다. "협동 로드"라는 또 다른 기능을 사용하면 코어가 캐시 가져오기 없이 서로 데이터를 직접 전송할 수 있습니다. 이 구성은 전력을 절약합니다. 8개의 코어는 또한 에너지 효율성을 위해 대용량 L2 캐시를 공유합니다.

다시 축소하면 4개의 8코어 동네가 "미니언 샤이어"를 구성하며 각 칩에 34개의 샤이어가 있고 총 1,088개의 코어가 있습니다. (수율을 향상시키기 위해 단 1,024개의 코어로 계산하는 것도 가능하다고 Ditzel은 말했습니다). 각각 Arm A-72와 대략 비슷한 성능을 보이는 4개의 ET-Maxion 코어는 현재 가속기 구성이 아닌 미래의 독립 실행형 작동을 위한 것입니다.

임계 전압 변동은 개별 전압을 미세 조정할 수 있도록 각 Shire에 자체 전압 공급을 제공하여 완화됩니다.

메모리 시스템

각 칩에는 4개의 64비트 DDR 인터페이스가 있습니다. 실제로 각 인터페이스는 총 96x 16비트 채널에 대해 4개의 16비트 채널을 나타냅니다. 디자인은 스마트폰용 저전력 메모리로 개발된 LPDDR4x를 사용합니다. 비트당 에너지는 대략 HBM과 동일하지만 6칩 가속기 카드의 메모리 인터페이스에서 총 1,536비트를 유지하면 더 높은 총 메모리 대역폭을 얻을 수 있습니다.

에스페란토는 듀얼 소켓 M.2 카드에 칩을 탑재했습니다. 6개는 OCP Glacier Point v2 가속기 카드에 맞습니다(앞면 3개, 뒷면 3개). 이는 1GHz에서 실행되는 칩으로 약 800TOPS를 제공합니다. 또한 각 칩의 전력 예산을 약 60W로 늘리는 로우 프로파일(절반 높이, 절반 길이) PCIe 카드에 장착할 수 있습니다. 칩은 애플리케이션에 따라 300MHz에서 2GHz 사이에서 작동할 수 있습니다.

하드웨어 에뮬레이션 결과를 기반으로 Ditzel은 Glacier Point 카드에 있는 6개의 에스페란토 칩이 경쟁 제품보다 성능이 뛰어날 수 있다고 주장했습니다. 저전압 설계에 중점을 둔 결과 메모리 시스템 설계와 와트당 성능 수치를 고려할 때 권장 사항 벤치마크에서 스타트업의 이점이 두드러집니다.

향후 버전에는 에지 애플리케이션용으로 축소된 버전의 ET-SoC-1이 포함될 수 있습니다. Ditzel은 현재 버전이 "앞으로 몇 달" 안에 출시될 것이라고 말했습니다.

>> 이 기사는 원래 자매 사이트인 EE에 게시되었습니다. 시간.

관련 콘텐츠:

더 많은 Embedded를 보려면 Embedded의 주간 이메일 뉴스레터를 구독하세요.

임베디드

맞춤형 ASIC 설계 회사인 EnSilica는 대량 시장의 첨단 웨어러블 의료 및 피트니스 생체 신호 모니터링 제품의 개발 속도를 높이는 데 도움이 되는 머신 러닝(ML) 가속기가 포함된 맞춤형 단일 칩 의료 센서 ASIC 플랫폼인 eSi-MediSense ASIC을 공개했습니다. 이 회사는 eSi-MediSense ASIC이 무선 기능을 갖춘 업계 최초의 단일 칩 의료 센서로 건강 모니터링 장치의 비용을 낮추는 데 도움이 된다고 주장합니다. 초저전력 플랫폼은 다중 프로세서 및 DSP 구성과 함께 작동합니다. Arm Ethos-U

샌디에이고와 대만에 기반을 둔 AI 실리콘 및 IP 스타트업인 Kneron은 회사의 NPU(신경 처리 장치) IP의 업데이트된 버전을 특징으로 하는 AI SoC를 출시했습니다. KL720은 또한 시스템 제어를 위한 Cadence DSP AI 보조 프로세서와 Arm Cortex M4 코어를 갖추고 있습니다. Kneron의 차세대 AI SoC는 비디오 초인종 및 로봇 진공 청소기와 같은 저전력 에지 및 스마트 홈 장치를 목표로 하지만 KL720은 Tesla에서 토스터에 이르기까지 모든 것에 사용할 수 있습니다라고 회사는 설명했습니다.