나노물질

이 연구에서는 FinFET 유전체 RRAM(FIND RRAM) 장치의 읽기 전류에서 RTN(Random Telegraph Noise) 신호에 대한 관찰이 제공됩니다. FIND RRAM 셀의 RTN 신호는 소자가 사이클링 스트레스를 받은 후 변화하는 것으로 나타났습니다. 사이클링 스트레스를 받은 후 RRAM 셀은 더 빈번하고 강렬한 RTN 신호를 표시하는 경향이 더 강해집니다. FIND RRAM 셀에서 노이즈 레벨의 증가는 일반적으로 고온 어닐링에 의해 완화될 수 있으며, 이러한 개념으로 온칩 어닐링 방식이 제안되고 시연됩니다.

CMOS 기술의 지속적인 확장은 지난 10년 동안 집적 회로의 특성과 성능을 크게 향상시켰습니다. 그러나 기술 노드가 20nm 이하로 축소됨에 따라 RDF(Random Dopant Fluctuation)와 같은 장치 특성의 단일 원자/전자에 의한 편차가 증가하여 간과할 수 없는 근본적인 문제가 발생합니다[1]. 예를 들어, 캐리어 수 또는 구조적 결함의 변동은 스케일링된 디바이스의 출력 및 성능에 훨씬 더 큰 영향을 미치며, RDF 및 게이트 라인 에지 거칠기(LER)로 인한 변동성에 대한 디바이스 스케일링의 영향도 보고되었다[2,3,4]. RTN(Random Telegraph Noise)은 NAND 플래시 및 RRAM과 같이 면적이 작은 장치의 또 다른 주요 문제로 생각됩니다[5,6,7,8,9,10,11]. 이 작업에서 우리는 1kbit 어레이의 표준 로직 프로세스에서 이미 성공적으로 구현된 n채널 FinFET 기반 FIND RRAM 셀에서 RTN 노이즈를 조사합니다[12]. 사이클링 응력과 고온 베이크에 대한 RTN의 변화가 관찰됩니다. 이 연구에서는 FIND RRAM 셀의 RTN 잡음에 대한 스트레스와 온도의 영향을 연구하고 사이클링 후 시변 읽기 전류 잡음을 완화하기 위해 온칩 어닐링 방식을 제안합니다.

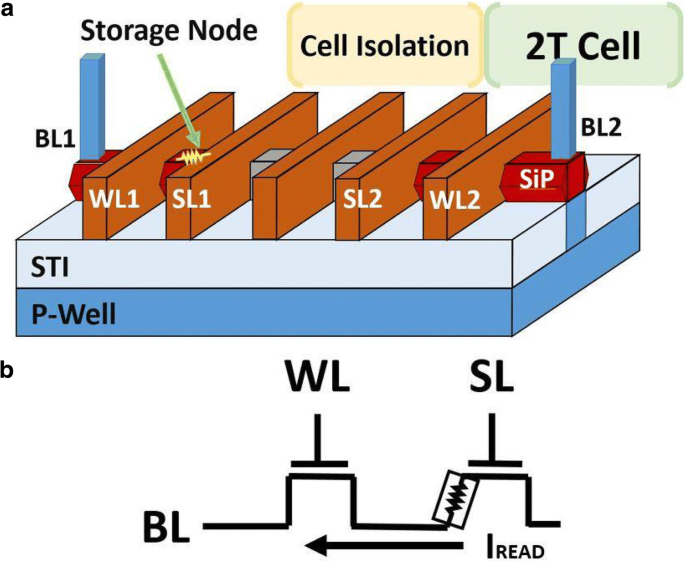

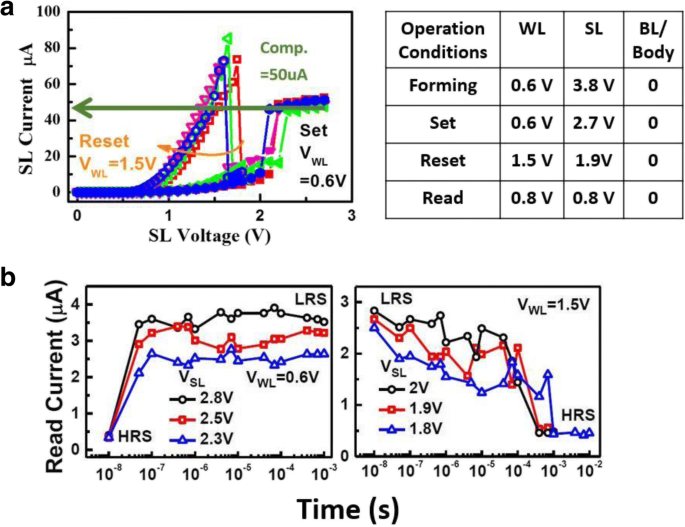

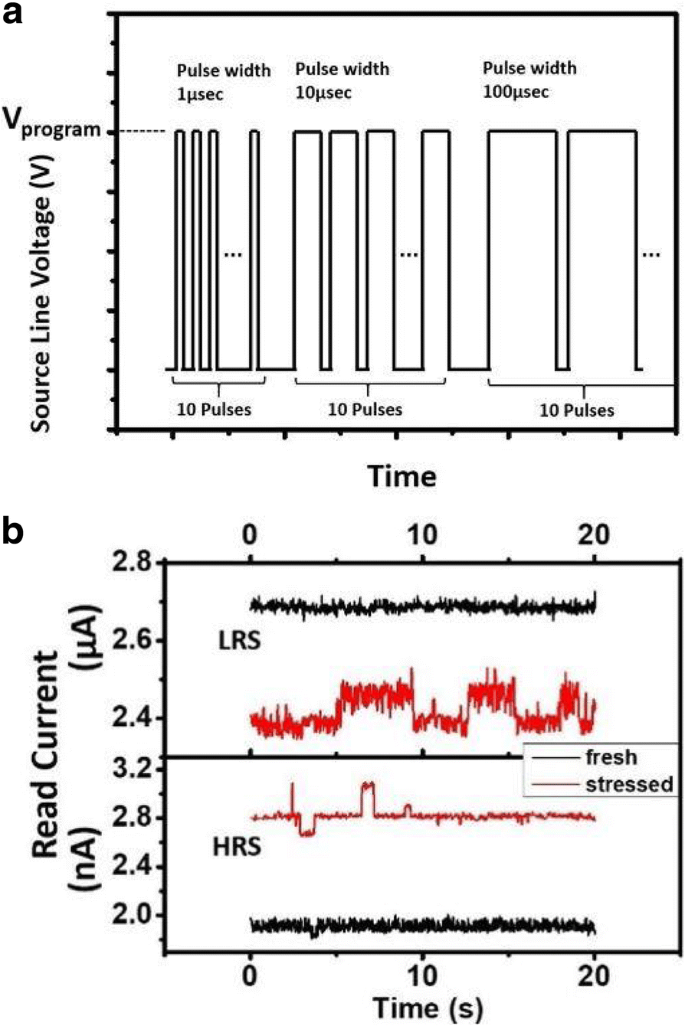

FIND RRAM은 두 개의 FinFET 트랜지스터로 구성됩니다. 하나는 RRAM 노드의 직렬에서 WL 선택 트랜지스터로 작동합니다. 다른 트랜지스터의 SiP와 SL 사이의 고유전율 게이트 유전체는 그림 1a와 같이 스토리지 노드 역할을 합니다. FIND 장치는 표준 FinFET의 게이트 유전막으로 구성되며, 여기서 게이트 전극은 상단 전극의 경우 W이고 하단 전극의 경우 TaN입니다. 게이트 스택 산화물은 HfO2로 구성됩니다. /SiO2 /TiN 스택 레이어 [12]. FIND RRAM 셀의 읽기 조건은 그림 1b에 나와 있습니다. 여기서 WL에는 선택 트랜지스터를 켜기 위해 0.8V가 제공되고 데이터 읽기를 위한 충분한 읽기 전류를 구동하기 위해 SL에 0.8V가 추가됩니다. 높은 저항 상태(HRS)와 낮은 저항 상태(LRS) 상태 사이의 저항 전환은 FIND RRAM 셀에서 설정/리셋을 수행하여 달성됩니다[13]. FIND RRAM은 DC 스위프에서 상당히 안정적인 저항성 스위칭 기능을 보여주며(그림 2a 참조), 설정 시간 및 재설정 시간 특성은 그림 2b에 요약되어 있습니다. 그림 2a에 나열된 작동 조건은 저전압 작동이 가능함을 보여줍니다. 셀은 목표 판독 전류 레벨에 도달하기 위해 설정 및 재설정 모두에 대해 여러 펄스 주기를 거칩니다. 그림 3a와 같이 여러 펄스가 적용된 후 장치가 설정 또는 재설정되지 않으면 펄스 폭이 증가합니다. 독특한 RTN 신호는 그림 3b와 같이 LRS 및 HRS FIND RRAM 셀 모두에서 찾을 수 있습니다. 전류 전도 경로에서 전하 트래핑 및 디트랩핑으로 인해 발생하는 RTN 신호는 상당한 전류 변동을 유발할 수 있습니다[14,15,16,17].

<그림>

아 CMOS FinFET 기술 및 b로 구현된 2 T FIND RRAM 셀의 3D 그림 읽기 조건에서 FIND RRAM에 대한 단위 셀의 회로도가 표시됩니다. 여기서 VSL =VWL =0.8 V이고 BL은 0에서 바이어스됩니다.

<그림>

FIND RRAM의 DC 저항성 스위칭 기능과 작동 조건은 (a ). 설정 시간 및 재설정 시간 특성은 (b )

<그림>

아 설정/리셋 작업을 수행하는 데 사용되는 증가하는 펄스 폭의 그림. 1μs의 첫 번째 펄스 후 읽기 작업이 수행되어 읽기 전류가 LRS의 경우 3μA, HRS의 경우 1μA 미만의 목표 수준에 도달하는지 평가합니다. 필요한 상태가 달성되지 않으면 다음 펄스가 제공됩니다. 펄스 폭은 10펄스마다 한 차수만큼 확장됩니다. ㄴ VSL =VWL =0.8 V 및 VBL =0에서 샘플링된 실온에서의 읽기 전류 비교(샘플링 레이트 500Hz, 100회 주기 전후)

반복적인 사이클링, 즉 두 상태 사이의 전환이 게이트 유전체 층 FinFET에 스트레스를 유발할 수 있다는 것은 잘 알려져 있습니다[18]. FIND RRAM 셀의 응력이 가해진 전이 금속 산화물(TMO) 층은 RTN 노이즈를 표시하는 경향이 더 강해 시간에 따른 읽기 전류를 발생시켜 데이터를 읽는 동안 읽기 오류와 안정성 문제를 일으킬 수 있습니다. 이 실험에서 우리는 FIND RRAM에서 RTN에 대한 스트레스 효과를 관찰하기 위해 10x 주기 후 및 100x 주기 후 어레이의 읽기 전류를 새로 샘플링했습니다.

스트레스를 받는 FIND RRAM 셀에 대한 온도 효과를 조사하기 위해 LRS에서 뚜렷한 RTN 신호를 가진 샘플을 먼저 0°C로 냉각한 다음 점차적으로 50°C까지 가열합니다. 이 과정에서 이러한 온도의 읽기 전류는 500Hz의 속도로 20초 동안 계속 샘플링됩니다. 이것은 RTN이 온도 변화 하에서 어떻게 작동하는지에 대한 몇 가지 단서를 제공합니다.

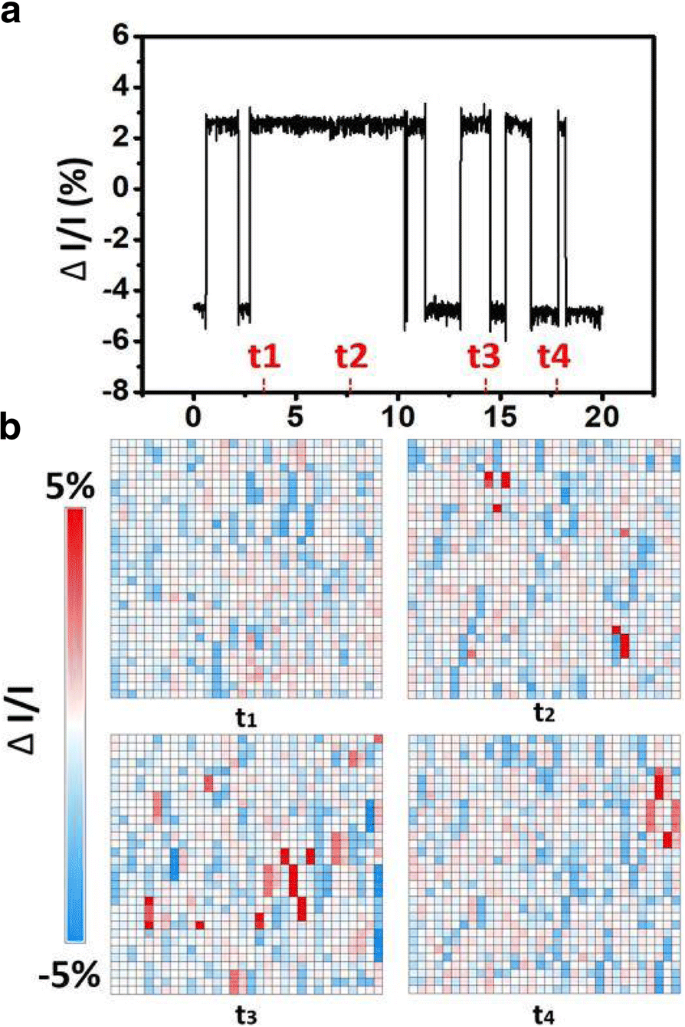

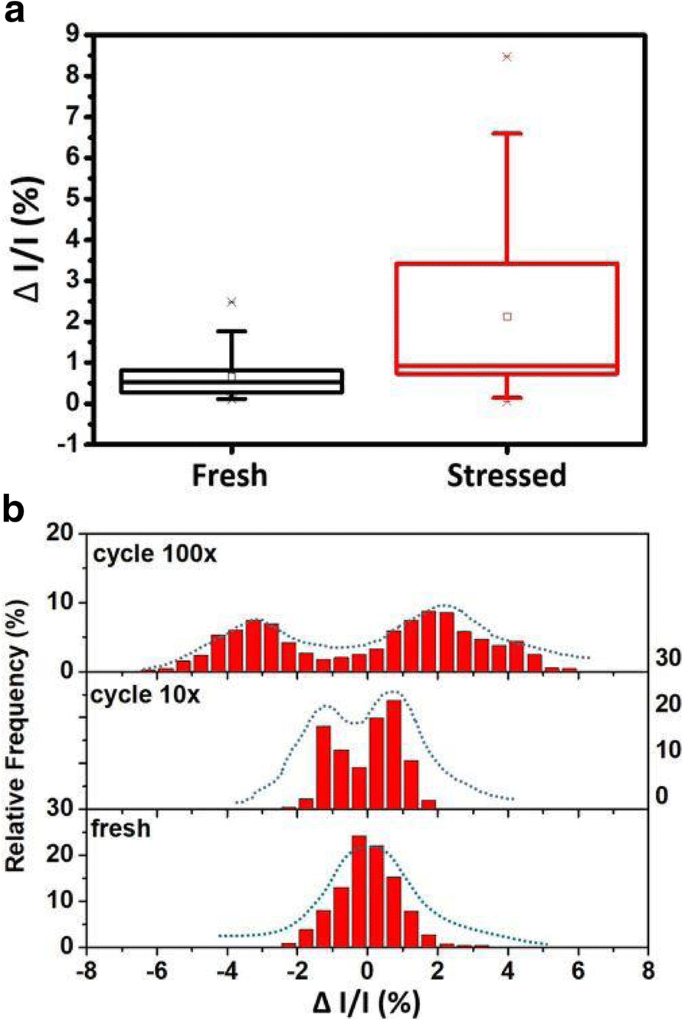

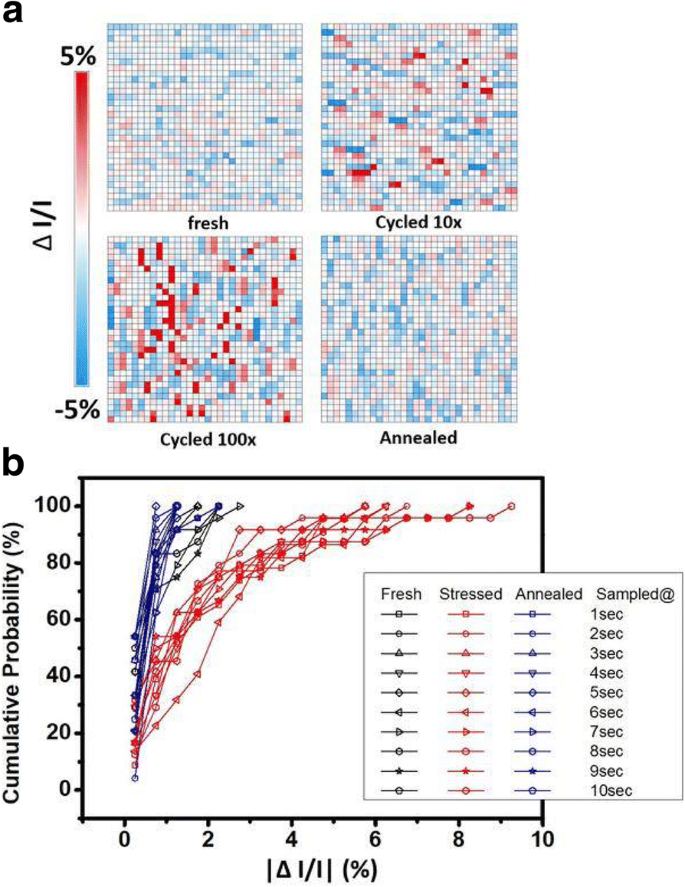

광범위한 측정을 통해 RTN이 LRS의 FIND RRAM 셀에서 보다 안정적이고 쉽게 관찰할 수 있음을 알 수 있습니다. 따라서 FIND RRAM 셀의 RTN에 대한 순환 및 어닐링 효과 연구에서 다음 섹션에서는 LRS의 셀 조사에 중점을 둡니다. 그림 4a와 같이 RTN 노이즈는 읽기 오류를 일으키는 시변 읽기 전류로 이어집니다. 이 효과는 1kbit 셀 어레이에서 관찰할 수 있습니다. 10주기를 거친 어레이에서 20초 간격 동안 읽기 전류를 샘플링할 때 상당한 읽기 전류 변동이 발견됩니다. 어레이의 정규화된 비트 전류 맵은 그림 4b에 배열되어 있으며, 여기서 LRS의 전류 변동은 + 5%만큼 높을 수 있으며, 이는 스트레스 후 게이트 누설 전류에서 관찰된 RTN과 유사합니다[19]. 스트레스의 영향을 조사하기 위해 사이클링 스트레스 전후의 50개 셀의 현재 변동 수준을 추적했습니다. 그림 5a의 데이터는 사이클링 후 90% 이상의 세포가 ΔI/I의 증가를 나타냄을 보여줍니다. 즉, FIND RRAM의 시변 잡음은 셀이 더 많은 사이클링 스트레스를 겪을수록 점차적으로 악화되는 것으로 나타났습니다. 새로운 세포와 순환된 세포의 정규화된 읽기 전류 분포를 비교할 때 더 많은 주기를 거친 세포가 더 중요한 RTN 신호를 나타내고 특정 상태에서 두 개 이상의 피크 전류 분포를 나타냅니다. 반면에 새로운 셀은 표준 분포의 전류 분포를 가지므로 그림 5b[20, 21]에서 볼 수 있듯이 변동과 관련된 RTN 노이즈가 없음을 나타냅니다. 이는 FIND RRAM이 긴 사이클링 스트레스를 받으면 RTN의 추가로 인해 비트 셀 전류가 더 급격하게 변동될 수 있음을 시사합니다.

<그림>

아 10주기를 거친 RRAM 셀에서 500Hz의 속도로 샘플링된 25°C의 정규화된 읽기 전류입니다. 이것은 RTN이 시변 읽기 전류를 유발한다는 것을 보여줍니다. ㄴ t1 =3, t2 =7.5, t3 =14, t4 =17.5 s에서 동시에 샘플링된 10 사이클을 거친 1kbit 배열의 정규화된 전류 플롯을 보여줍니다. 다른 시간의 스냅샷을 비교하여 동일한 읽기 조건에서 읽기 전류가 변동합니다.

<그림>

아 |ΔI/I| 분포 비교 스트레스 전후의 50개 샘플. 세포는 스트레스 후 전반적으로 더 큰 ΔI/I를 나타냄을 알 수 있습니다. 상자 그림의 백분위수 값은 아래에서 위로 각각 25, 50, 75 백분위수를 나타내고 수염은 최대값과 최소값을 나타냅니다. ㄴ 새 상태와 10 및 100 주기 후에 측정된 셀의 정규화된 읽기 전류 분포의 히스토그램입니다. 이것은 FIND RRAM이 긴 사이클링 스트레스를 받으면 RTN의 추가로 인해 비트 셀 전류가 더 급격한 변동을 겪을 수 있음을 보여줍니다.

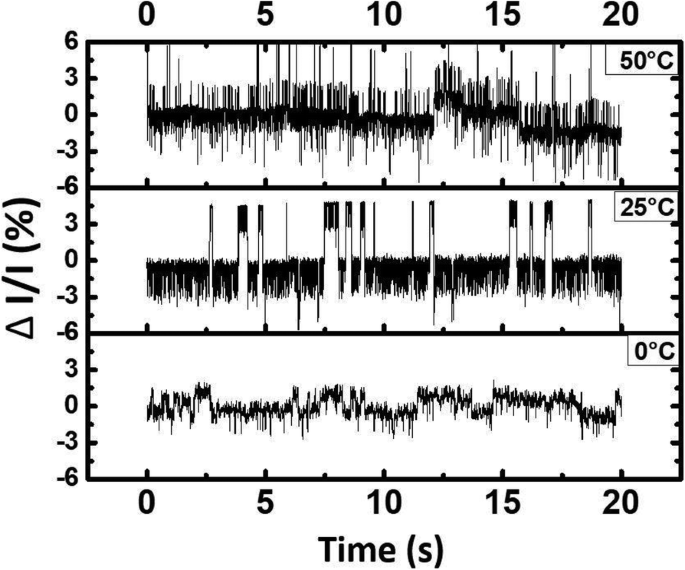

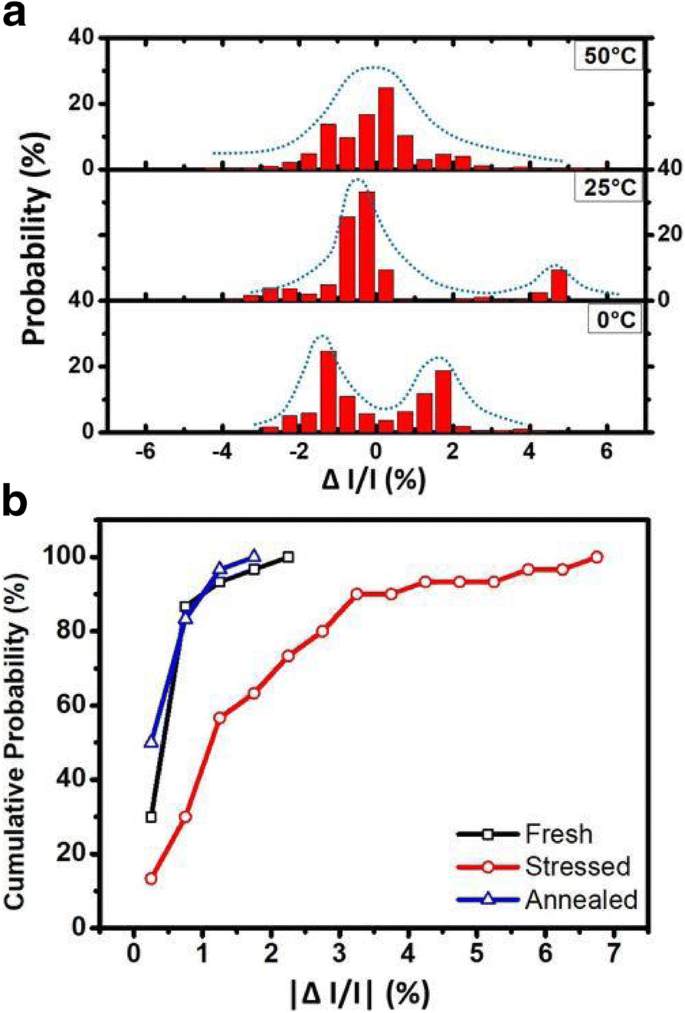

다른 온도 단계에서 판독 전류 샘플의 정규화된 결과가 그림 6에 비교되어 있습니다. RTN 트랩의 캡처 시간과 방출 시간이 연구되었으며 온도에 따라 변화하는 것으로 알려져 있으며 둘 다 온도가 증가함에 따라 감소합니다[22, 23 ]. 예상대로 RTN 노이즈의 주파수는 온도가 증가함에 따라 증가합니다. 즉, 0°C에서 읽기 전류의 변동이 25°C에서보다 덜 자주 발생합니다. 그러나 50°C에서 측정하면 두 상태 간의 전류 변동이 덜 두드러집니다. 이는 0°C, 50°C 및 실온에서 측정된 정규화된 판독 전류의 히스토그램을 플롯한 그림 7a에서 더 자세히 알 수 있습니다. 0°C 및 25°C의 전류 분포에는 두 개의 분포 피크가 있는데, 이는 단일 트래핑 상태 RTN이 전도성 경로를 지배함을 시사하는 반면[19], 50°C에서 샘플링된 전류의 이산 상태는 덜 두드러집니다. 이것은 더 높은 온도에서 RTN 신호를 유발하는 트랩이 어닐링 효과 또는 결함 재결합과 같은 불안정성을 일으켜 결과적으로 전자 트랩 확률에 영향을 미치고 RTN 효과를 완화할 수 있음을 시사합니다[27].

<그림>

500Hz의 샘플링 레이트에서 0, 25, 50°C에서 측정된 RTN 노이즈와 100주기를 거친 RRAM 셀(LRS 상태)의 정규화된 읽기 전류 비교

<그림>

아 0, 25, 50°C에서 측정된 LRS 상태의 셀에 대한 정규화된 읽기 전류 분포의 히스토그램 비교 ㄴ |ΔI/I|의 누적 확률 비교 응력 전, 응력 후 및 어닐링 후 각각 30개 샘플. 어닐링 과정 후에 셀의 많은 부분이 원래의 ΔI/I로 되돌아가는 것으로 밝혀졌습니다.

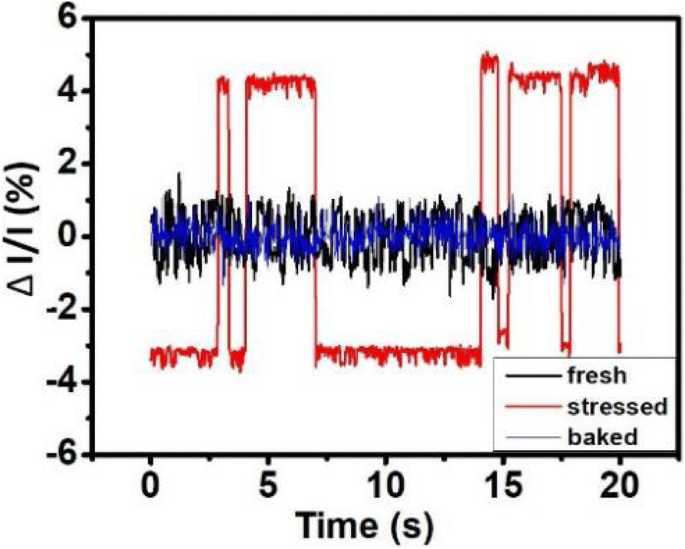

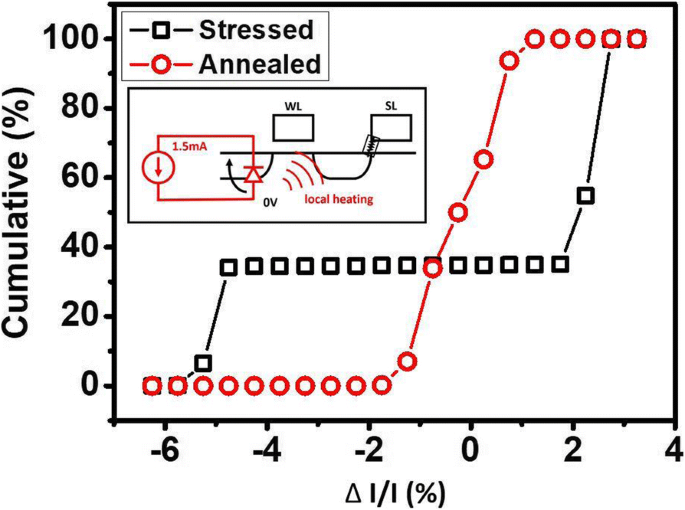

추가 연구에서 샘플은 최대 75°C까지 가열됩니다. 이 세포는 30분 후 실온으로 냉각된 다음 샘플을 채취합니다. 30개의 셀이 선택되고 신선, 스트레스 및 어닐링 후 누적 전류 변동 수준이 그림 7b에서 비교됩니다. 이것은 대부분의 셀이 어닐링 프로세스 후에 원래의 ΔI/I로 되돌아간다는 것을 보여줍니다. 그림 8은 신선한 상태, 스트레스 상태 및 베이킹 후 셀의 정규화된 읽기 전류를 비교한 것입니다. 베이킹 후 전류는 신선한 것과 유사하여 고온 베이크가 RTN 신호를 유발하는 트랩을 어닐링함을 시사합니다. 그림 9a는 1kbit의 새로운 셀, 약간 스트레스를 받은 셀, 높은 스트레스를 받은 셀 및 베이킹 후의 셀의 1kbit 어레이에 대한 정규화된 읽기 전류의 배열된 플롯입니다. 플롯에서 전류 변동은 RRAM에 높은 응력이 가해질 때 더 강렬해지고 고온 베이크 후에는 급격히 감소함을 보여줍니다. 이 효과는 전체 어레이에서 관찰될 수 있으며, 이는 고온 베이크가 실제로 RTN 노이즈를 유도하는 트랩에 어닐링 효과를 제공한다는 것을 확인시켜줍니다[24,25,26,27,28,29]. 그림 9b는 10개의 서로 다른 샘플링을 순차적으로 수행하여 얻은 셀 어레이의 ΔI/I 분포를 추가로 비교합니다. 동일한 어레이가 신선, 응력 및 어닐링 후 상태에서 다른 ΔI/I 분포를 나타내는 것으로 밝혀졌습니다. 데이터는 어닐링이 셀 어레이가 새로운 상태의 어레이 수준과 유사한 감소된 전류 변동을 나타내는 데 도움이 된다고 제안했습니다. 이 결과는 사이클링 스트레스 후 RTN 신호를 나타내는 FIND RRAM 셀의 수명을 수정하고 연장하는 데 사용할 수 있습니다.

<그림>

25°C, 500Hz에서 샘플링된 신선하고 스트레스를 받은 세포의 전류를 실온으로 30분 동안 고온 베이킹 및 냉각한 후의 전지와 비교하여 판독합니다. 베이킹 후 스트레스가 해소되고 세포가 신선한 것과 유사하게 동작함을 보여줍니다.

<사진>

아 특정 시간에 취한 1kbit 어레이의 정규화된 읽기 전류는 신선, 약한 스트레스, 높은 스트레스 및 어닐링 후 플롯됩니다. 어레이에 더 많은 응력이 가해짐에 따라 변동이 심한 셀의 수가 어레이 전체에 걸쳐 크게 증가하고 어닐링된 후에는 소멸됨을 알 수 있습니다. ㄴ |ΔI/I|의 누적 확률 비교 1초 간격으로 다른 시간 인스턴스에서 신선한 상태, 스트레스 상태 및 어닐링 후 상태의 동일한 어레이에서 50개 샘플의 분포. 응력 후 샘플의 전체 ΔI/I가 더 높고 어닐링 후 정상으로 돌아갑니다.

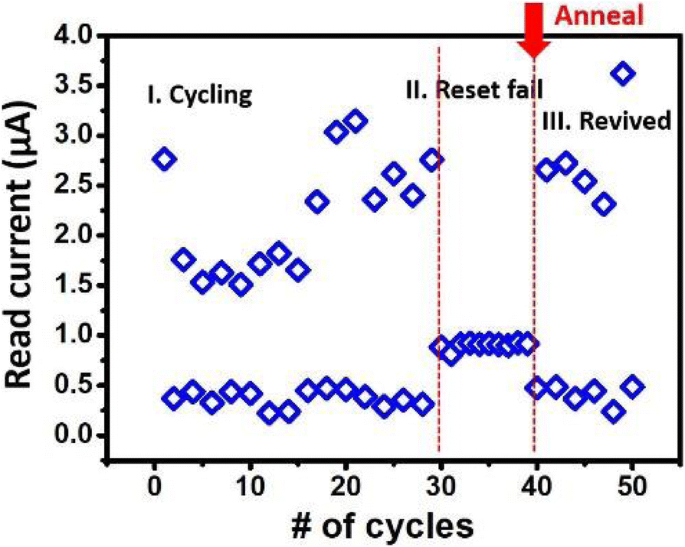

사이클링 중 중간 상태에 갇혀 있던 일부 세포가 고온 처리 후 소생된다는 점은 언급할 가치가 있습니다. FinFET RRAM 셀이 LRS 및 HRS를 순환함에 따라 일부 셀의 전도성 필라멘트는 쉽게 재설정할 수 없는 채널을 형성할 수 있습니다. 베이킹 과정은 이러한 세포에 산소 결손을 재분배하는 경로를 제공하여 결과적으로 HRS로의 효과적인 재설정을 허용합니다[30]. 그림 10은 HRS로 전환할 수 없었던 셀이 125°C, 15분 베이킹 후 소생되는 것을 보여줍니다. 이를 염두에 두고 FIND RRAM 셀을 국부적으로 가열하는 것과 관련된 온칩 어닐링 메커니즘이 제안됩니다. 그림 11a와 같이 10초 주기로 1.5mA의 정전류가 선택 FinFET의 드레인 접합에서 순방향 바이어스를 통해 셀에 인가됩니다. 이 큰 전류는 RRAM TMO 근처의 제한된 영역을 가열하고 유사한 어닐링 효과를 제공합니다. 테스트 대상 장치(DUT)의 열처리 전과 후의 판독 전류를 측정하고 그림 11b에서 분석합니다. 지속적으로 샘플링된 판독 전류의 누적 분포는 온칩 어닐링 단계 후 셀에서 RTN이 제거되었음을 보여줍니다. 여기에서 FIND RRAM의 온칩 어닐링은 스트레스 후 일반적인 RRAM 셀에 대한 공칭 응답을 이해하기 위해 순차적 단계로 단일 셀에서 수행되었습니다. 어레이 수준 실험을 위해 새로운 온칩 어닐링 절차를 개발해야 합니다.

<그림>

중간 상태에 있는 셀에 125°C 베이킹을 적용하고 어닐링 프로세스를 제공하여 이러한 셀을 다시 기능 상태로 전환하여 셀 수명을 연장합니다.

<사진>

우리가 제안한 온칩 어닐링 방식은 BL에 − 1 V를 적용하여 순방향 바이어스와 1.5mA의 측정된 전류를 인가하여 스트레스를 받은 셀을 가열하고 어닐링합니다. Plot에서 처리 전과 후의 셀의 정규화 된 전류의 누적 백분율을 비교하여 RTN으로 인한 전류 변동이 크게 감소함을 알 수 있습니다.

이 논문에서는 FIND RRAM 셀 어레이에서 RTN에 대한 응력 및 온도 영향에 대해 설명합니다. 사이클링 스트레스로 인한 RTN 증가가 관찰됩니다. 고온 처리가 FIND RRAM에서 TMO에 대한 RTN 감소 및 스트레스 완화에 미치는 영향이 관찰됩니다. 마지막으로 온칩 어닐링 방식을 제안하고 시연합니다.

핀 전계 효과 트랜지스터 유전체 저항성 랜덤 액세스 메모리

고저항 상태

선 가장자리 거칠기

낮은 저항 상태

무작위 전신 소음

전이 금속 산화물

나노물질

구성품 및 소모품 Arduino UNO × 1 Adafruit BMP280 × 1 Adafruit OLED 128x32 i2c × 1 이 프로젝트 정보 안녕하세요. BMP280을 사용하여 Arduino UNO 보드와 OLED 디스플레이를 사용하여 온도, 압력 및 고도를 측정하는 이 튜토리얼에 오신 것을 환영합니다. 다음은 데이터시트의 BMP280 주요 매개변수 중 일부입니다. 그래서 이 프로젝트에서 모듈을 사용하여 평소와 같이 미터법 및 영국식 시스템 모두

제품을 제조하는 동안 금속 재료는 다양한 공정을 거칩니다. 금속은 단조, 주조, 굽힘, 회전, 밀링, 연마, 드릴링, 용접 또는 기타 가공될 수 있습니다. 금속 부품에 압력을 가하는 도구와 고정 장치가 너무 많기 때문에 다양한 유형의 응력이 발생할 수 있습니다. 부품이 더 부서지기 쉽고 부드러우며 자성이 생길 수 있습니다. 이러한 문제는 금속의 결정자라고도 하는 작은 입자의 변화로 인해 발생합니다. 금속은 가열 및 냉각 과정에서 성장하는 결정립 구조를 가지고 있습니다. 결정 사이의 영역은 결정립 구조입니다. 금속이 가공됨에 따라