산업기술

반가산기는 두 개 이상의 이진수 양을 더할 때까지 매우 유용합니다. 2진수 가산기를 개발하는 느린 방법은 진리표를 만들고 줄이는 것입니다. 그런 다음 세 개의 이진수 가산기를 만들기로 결정하면 다시 수행하십시오. 그런 다음 4자리 덧셈기를 만들기로 결정하면 다시 하십시오. 그러면 언제... 회로는 빠르지만 개발 시간은 느릴 것입니다.

두 개의 이진수 합계를 보면 여러 이진수로 더하기를 확장하는 데 필요한 것이 무엇인지 알 수 있습니다.

<중> 11 11 11 --- 110중간 열이 사용하는 입력의 수를 보십시오. 가산기는 3개의 입력이 필요합니다. , b 및 이전 합계의 캐리가 있고 2입력 가산기를 사용하여 3입력 가산기를 만들 수 있습니다.

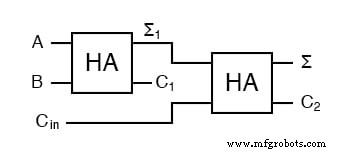

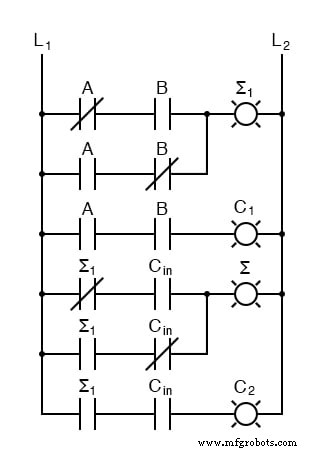

Σ는 쉬운 부분입니다. 일반 산술은 Σ =a + b + Cin이면 및 Σ1 =a + b, Σ =Σ1 + Cin .

C1로 무엇을 할까요? 및 C2 ? 세 가지 입력 합계를 보고 빠르게 계산해 보겠습니다.

<사전>Cin + a + b =? 0 + 0 + 0 =0 0 + 0 + 1 =1 0 + 1 + 0 =1 0 + 1 + 1 =10 1 + 0 + 0 =1 1 + 0 + 1 =10 1 + 1 + 0 =10 1 + 1 + 1 =11

하위 비트가 걱정된다면 회로와 래더가 올바르게 계산되었는지 확인하십시오.

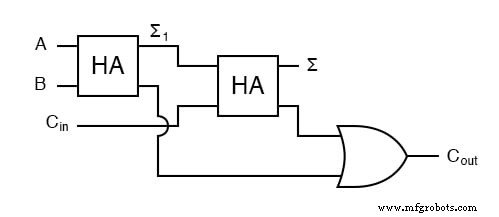

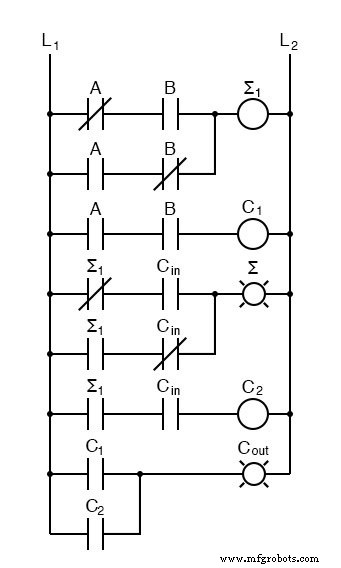

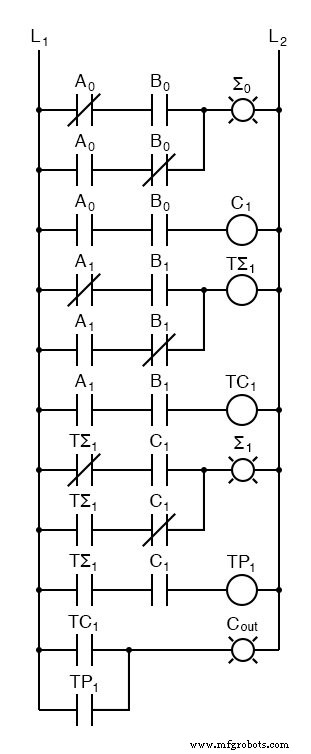

상위 비트를 계산하려면 a + b가 C1을 생성할 때 두 경우 모두 1입니다. . 또한 a + b가 Σ1을 생성할 때 상위 비트는 1입니다. 및 Cin 는 1입니다. 따라서 C1일 때 캐리가 발생합니다. 또는 (Σ1 AND Cin ). 완전한 3개의 입력 가산기는 다음과 같습니다.

일부 디자인의 경우 하나 이상의 게이트 유형을 제거하는 것이 중요할 수 있으며 결과를 변경하지 않고 최종 OR 게이트를 XOR 게이트로 교체할 수 있습니다.

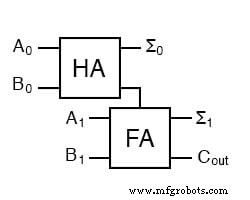

이제 두 개의 가산기를 연결하여 2비트 수량을 추가할 수 있습니다.

A0 A의 하위 비트, A1 A, B0의 상위 비트입니다. B의 하위 비트, B1 B의 상위 비트, Σ0 합계의 하위 비트, Σ1 합계의 상위 비트이고 Cout 캐리입니다.

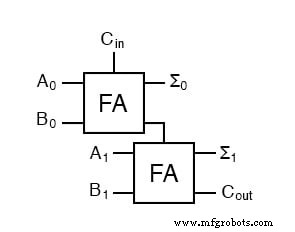

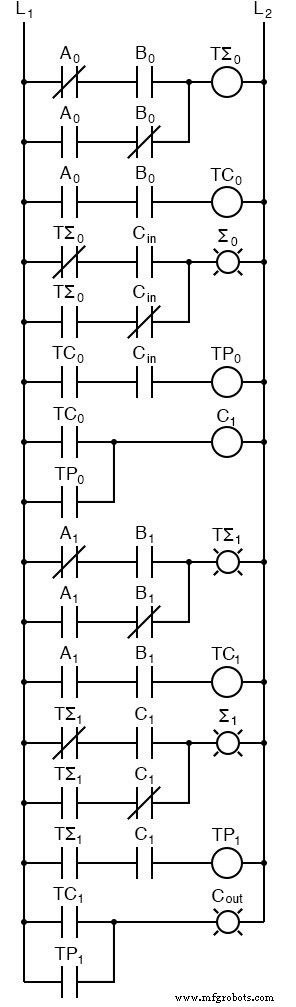

2진수 가산기는 이런 식으로 만들어지지 않습니다. 대신 최하위 비트도 전가산기를 거칩니다.

여기에는 몇 가지 이유가 있는데, 그 중 하나는 회로가 최하위 캐리를 합계에 포함해야 하는지 여부를 결정할 수 있기 때문입니다. 이것은 더 큰 액수의 연결을 허용합니다. 4비트 합을 보는 두 가지 다른 방법을 고려하십시오.

<사전> 111 1<-+ 11<+- 0110 | 01 | 10 1011 | 10 | 11 ----- - | ---- | --- 10001 1 +-100 +-101

프로그램이 2비트 수를 추가하고 나중을 위해 캐리를 기억하도록 허용하면 다음 합계에서 해당 캐리를 사용하면 2비트 가산기만 제공하더라도 프로그램은 사용자가 원하는 수의 비트를 추가할 수 있습니다. 작은 PLC는 더 많은 수를 위해 함께 연결할 수도 있습니다.

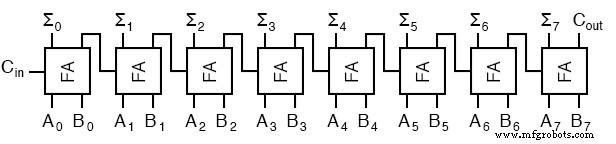

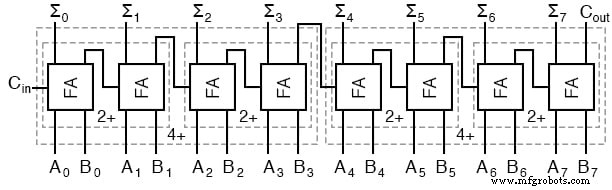

이 전가산기는 공간이 허용하는 모든 수의 비트로 확장될 수도 있습니다. 예를 들어 8비트 가산기를 수행하는 방법은 다음과 같습니다.

이는 2개의 2비트 가산기를 사용하여 4비트 가산기를 만든 다음 2개의 4비트 가산기를 사용하여 8비트 가산기를 만들거나 래더 로직을 다시 복제하여 숫자를 업데이트하는 것과 같은 결과입니다.

각 "2+"는 2비트 가산기이며 2개의 전가산기로 구성됩니다. 각 "4+"는 4비트 가산기이며 2개의 2비트 가산기로 구성됩니다. 그리고 두 개의 4비트 가산기의 결과는 우리가 구축하기 위해 사용했던 것과 동일한 8비트 가산기입니다.

큰 조합 회로의 경우 일반적으로 두 가지 설계 접근 방식이 있습니다. 더 간단한 회로를 선택하여 복제할 수 있습니다. 또는 복잡한 회로를 완전한 장치로 설계할 수 있습니다. 더 간단한 회로를 사용하여 복잡한 회로를 구축하면 설계 시간을 줄일 수 있지만 신호가 트랜지스터를 통해 전파되는 데 더 많은 시간이 필요합니다.

위의 8비트 가산기 디자인은 모든 Cx를 기다려야 합니다. 밖으로 A0에서 이동하라는 신호 + B0 Σ7의 입력까지 . 설계자가 곱의 합으로 단순화된 완전한 장치로 8비트 가산기를 구축하면 각 신호는 하나의 NOT 게이트, 하나의 AND 게이트 및 하나의 OR 게이트를 통해 이동합니다.

17개의 입력 장치에는 131,072개의 항목이 있는 진리표가 있으며 131,072개의 항목을 곱의 합으로 줄이는 데는 시간이 걸립니다. 최종 결과를 제공하기 위해 최대 허용 응답 시간이 있는 시스템을 설계할 때 더 간단한 회로를 사용한 다음 너무 느린 회로 부분을 교체하려고 시도할 수 있습니다.

그렇게 하면 중요한 회로 부분에 대부분의 시간을 할애할 수 있습니다.

관련 워크시트:

<울> <리>이진 수학 회로 워크시트

산업기술

가산기는 두 숫자의 덧셈을 수행하는 디지털 구성 요소입니다. 프로세서의 ALU 내부의 주요 구성 요소이며 주소, 테이블 인덱스, 버퍼 포인터 및 추가가 필요한 다른 많은 위치를 증가시키는 데 사용됩니다. 전가산기는 다른 입력 이진수와 함께 캐리 입력을 추가하여 합계 및 캐리 출력을 생성합니다. 진실의 표 A 나 신 사냥꾼 합 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 디자인 아래는 4비트 폭인

논리 회로는 n비트 값을 함께 추가하기 위해 리플 캐리 가산기에 의존할 수 있습니다. 결과적으로 이 디지털 회로 구현은 많은 애플리케이션에서 유용한 기능을 제공합니다. 그러나 느린 계산 프로세스로 인해 지연된 성능도 나타납니다. 여기에는 일반적으로 각 전가산기 단계가 비트를 다음 전가산기 단계로 파급할 때까지 기다리는 것이 포함됩니다. 이러한 프로세스는 끝에 도달할 때까지 반복되어 결과를 제공합니다. 리플 캐리 가산기를 이해하는 것은 다소 혼란스러울 수 있습니다. 이를 염두에 두고 이 주제에 대해 더 많은 지식을 얻을 수 있도록