verilog

가산기는 두 숫자의 덧셈을 수행하는 디지털 구성 요소입니다. 프로세서의 ALU 내부의 주요 구성 요소이며 주소, 테이블 인덱스, 버퍼 포인터 및 추가가 필요한 다른 많은 위치를 증가시키는 데 사용됩니다.

전가산기는 다른 입력 이진수와 함께 캐리 입력을 추가하여 합계 및 캐리 출력을 생성합니다.

| A | 나 | 신 | 사냥꾼 | 합 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

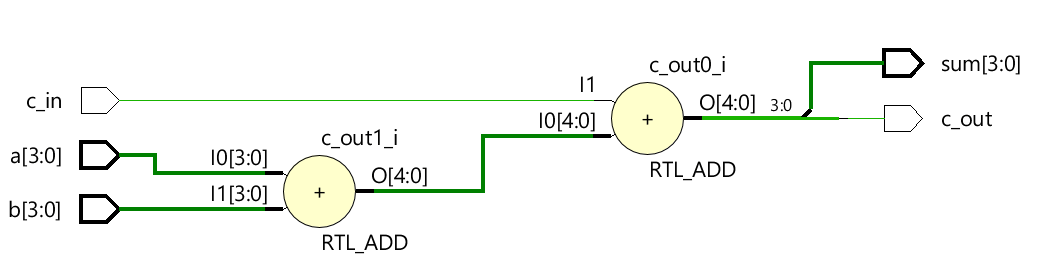

아래는 4비트 폭인 신호 a와 b를 통해 두 개의 이진수를 받아들이는 4비트 가산기의 예입니다. 가산기는 조합 회로이므로 assign로 연속 할당을 사용하여 Verilog에서 모델링할 수 있습니다. 또는 always 모든 입력으로 구성된 민감도 목록이 있는 블록. 아래에 표시된 코드는 이전 방식의 코드입니다.

module fulladd ( input [3:0] a,

input [3:0] b,

input c_in,

output c_out,

output [3:0] sum);

assign {c_out, sum} = a + b + c_in;

endmodule

아래 표시된 코드는 always을 사용합니다. 입력이 값을 변경할 때마다 실행되는 블록입니다.

module fulladd ( input [3:0] a,

input [3:0] b,

input c_in,

output reg c_out,

output reg [3:0] sum);

always @ (a or b or c_in) begin

{c_out, sum} = a + b + c_in;

end

endmodule

module tb_fulladd;

// 1. Declare testbench variables

reg [3:0] a;

reg [3:0] b;

reg c_in;

wire [3:0] sum;

integer i;

// 2. Instantiate the design and connect to testbench variables

fulladd fa0 ( .a (a),

.b (b),

.c_in (c_in),

.c_out (c_out),

.sum (sum));

// 3. Provide stimulus to test the design

initial begin

a <= 0;

b <= 0;

c_in <= 0;

$monitor ("a=0x%0h b=0x%0h c_in=0x%0h c_out=0x%0h sum=0x%0h", a, b, c_in, c_out, sum);

// Use a for loop to apply random values to the input

for (i = 0; i < 5; i = i+1) begin

#10 a <= $random;

b <= $random;

c_in <= $random;

end

end

endmodule

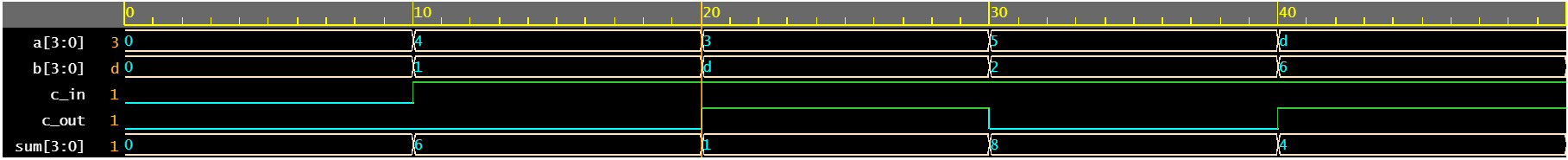

a와 b가 합하여 4비트 너비보다 큰 숫자가 나오면 합계는 0으로 롤오버되고 c_out은 1이 됩니다. 예를 들어 노란색으로 강조 표시된 라인은 합산하여 0x11을 제공하고 하위 4비트가 할당됩니다. 합계 및 비트 #4를 c_out으로.

시뮬레이션 로그ncsim> run a=0x0 b=0x0 c_in=0x0 c_out=0x0 sum=0x0 a=0x4 b=0x1 c_in=0x1 c_out=0x0 sum=0x6 a=0x3 b=0xd c_in=0x1 c_out=0x1 sum=0x1 a=0x5 b=0x2 c_in=0x1 c_out=0x0 sum=0x8 a=0xd b=0x6 c_in=0x1 c_out=0x1 sum=0x4 a=0xd b=0xc c_in=0x1 c_out=0x1 sum=0xa ncsim: *W,RNQUIE: Simulation is complete.<노스크립트>

verilog

디자인 module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else if

가산기는 두 숫자의 덧셈을 수행하는 디지털 구성 요소입니다. 프로세서의 ALU 내부의 주요 구성 요소이며 주소, 테이블 인덱스, 버퍼 포인터 및 추가가 필요한 다른 많은 위치를 증가시키는 데 사용됩니다. 전가산기는 다른 입력 이진수와 함께 캐리 입력을 추가하여 합계 및 캐리 출력을 생성합니다. 진실의 표 A 나 신 사냥꾼 합 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 디자인 아래는 4비트 폭인