산업기술

이진 가중치 입력이라고도 하는 R/2nR DAC 회로 DAC는 반전 합산 연산 증폭기 회로의 변형입니다. ("합산" 회로는 때때로 "여름" 회로라고도 합니다.)

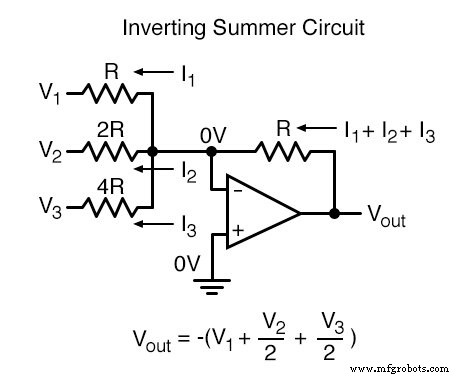

회상한다면, 고전적인 반전 합산 회로는 여러 전압 입력과 하나의 전압 출력이 있는 제어된 이득을 위해 네거티브 피드백을 사용하는 연산 증폭기입니다. 출력 전압은 모든 입력 전압의 반전(반대 극성) 합계입니다.

간단한 반전 합산 회로의 경우 모든 저항의 값이 같아야 합니다. 입력 저항 중 하나라도 다른 경우 입력 전압은 출력에 미치는 영향의 정도가 다르며 출력 전압은 실제 합이 아닙니다.

그러나 의도적으로 입력 저항을 다른 값으로 설정하는 경우를 고려해 보겠습니다. 입력 저항 값을 모두 동일한 값 R:

대신 R, 2R 및 4R의 2승으로 설정한다고 가정합니다.

V1부터 시작 V3을 통해 , 이것은 각 입력 전압이 그 이전의 전압으로 출력에 미치는 영향의 정확히 절반을 줄 것입니다. 즉, 입력 전압 V1 출력 전압(1의 이득)에 1:1 효과가 있는 반면 입력 전압 V2 출력에 절반의 영향을 미치고(1/2의 이득) V3 그 절반(1/4의 이득).

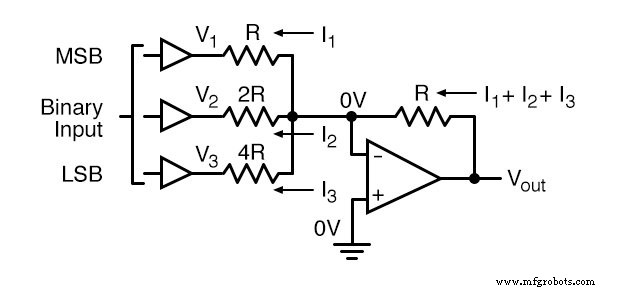

이 비율은 임의로 선택한 것이 아닙니다. 이진법 시스템에서 가중치에 해당하는 동일한 비율입니다. 각 입력이 0볼트 또는 전체 공급 전압이 되도록 이 회로의 입력을 디지털 게이트로 구동하면 출력 전압은 이 3비트의 이진 값의 아날로그 표현이 됩니다.

이 회로에 입력된 8가지 바이너리 비트(000에서 111까지)의 모든 조합에 대한 출력 전압을 차트로 나타내면 다음과 같은 전압 진행을 얻을 수 있습니다.

<사전>---------------- | 바이너리 | 출력 전압 | ----------- | 000 | 0.00V | -------------- | 001 | -1.25V | ------------------ | 010 | -2.50V | -------------- | 011 | -3.75V | ------------------ | 100 | -5.00V | -------------- | 101 | -6.25V | ------------------ | 110 | -7.50V | -------------- | 111 | -8.75V | ------------------

바이너리 카운트 시퀀스의 각 단계에서 출력에 1.25볼트 변화가 발생한다는 점에 유의하십시오.

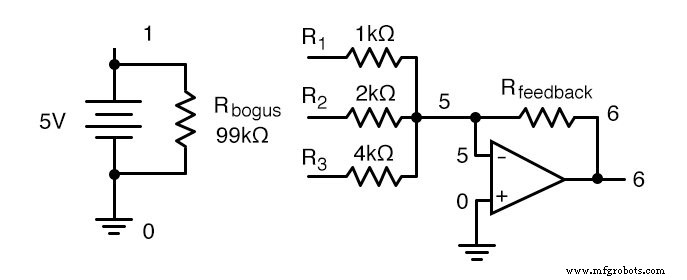

이 회로는 SPICE를 사용하여 시뮬레이션하기가 매우 쉽습니다. 다음 시뮬레이션에서 110의 이진 입력으로 DAC 회로를 설정했습니다(저항 R1의 첫 번째 노드 번호 참고). , R2 , 및 R3 :노드 번호 "1"은 5볼트 배터리의 양극에 연결하고 노드 번호 "0"은 접지에 연결).

시뮬레이션의 노드 6에 출력 전압이 나타납니다.

이진 가중치 dac v1 1 0 dc 5 rbogus 1 0 99k r1 1 5 1k r2 1 5 2k r3 0 5 4k rfeedbk 5 6 1k e1 6 0 5 0 999k .end 노드 전압 0 999k .end 노드 전압 0 노드 전압 (5) 0.0000 (6) -7.5000

이 회로의 저항 값을 조정하여 이진 입력에 직접 해당하는 출력 전압을 얻을 수 있습니다. 예를 들어, 피드백 저항을 1kΩ 대신 800Ω으로 만들면 DAC는 이진 입력 001에 대해 -1볼트, 이진 입력 100에 대해 -4볼트, 이진 입력 111에 대해 -7볼트 등을 출력합니다.

(피드백 저항이 800옴으로 설정됨) ------ | 바이너리 | 출력 전압 | ---------------- | 000 | 0.00V | ------------ | 001 | -1.00V | ---------------- | 010 | -2.00V | ------------ | 011 | -3.00V | ---------------- | 100 | -4.00V | ------------ | 101 | -5.00V | ---------------- | 110 | -6.00V | ------------ | 111 | -7.00V | ----------------

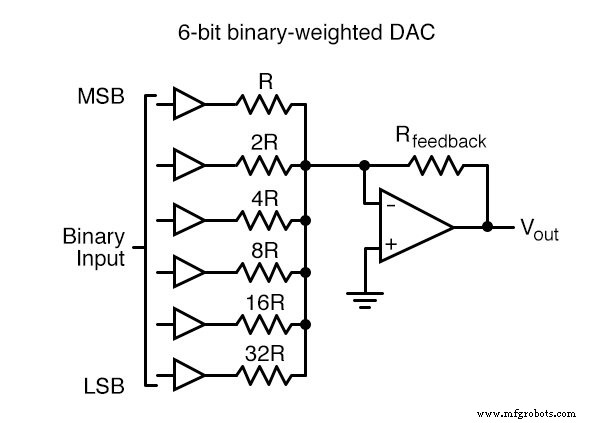

이 DAC의 분해능을 확장하려면(입력에 더 많은 비트 추가) 동일한 2의 거듭제곱 값 시퀀스를 유지하면서 입력 저항을 더 추가하기만 하면 됩니다.

모든 논리 게이트는 "하이" 상태일 때 정확히 동일한 전압을 출력해야 합니다. 한 게이트가 "높음"에 대해 +5.02볼트를 출력하고 다른 게이트가 +4.86볼트만 출력하는 경우 DAC의 아날로그 출력에 부정적인 영향을 미칩니다.

마찬가지로 모든 "낮은" 전압 레벨은 게이트 간에 동일해야 하며 이상적으로는 정확히 0.00볼트여야 합니다. CMOS 출력 게이트를 사용하고 각 게이트가 소싱 또는 싱크해야 하는 전류의 양을 최소화하도록 입력/피드백 저항 값을 선택하는 것이 좋습니다.

산업기술

DIY 디지털 아날로그 변환기 정보, iPod, 랩톱 또는 기타 오디오 장비에서 디지털 방식으로 저장된 정보를 우리가 듣는 아날로그 사운드로 변환하는 것은 까다로운 프로젝트일 수 있습니다. 말처럼 쉽지만 DAC라는 하나의 핵심 구성 요소 없이는 원하는 결과를 얻을 수 없습니다. 소리를 더 좋게 만들더라도 좋은 품질의 디지털-아날로그 변환기를 사용하면 더 나은 음향 배경을 얻을 수 있습니다. 따라서 프로젝트에 대한 더 깊은 청취 범위를 만듭니다. 여기 가장 좋은 부분이 있습니다. DAC를 구입할 필요가 없습니다. DIY DAC

DAC의 종류, 신호는 일반적으로 디지털 신호와 아날로그 신호의 주요 그룹으로 분류됩니다. 그리고 각 통화에는 다양한 유형의 응용 프로그램이 있습니다. 예를 들어, 전원 스위치 및 연산 증폭기와 같은 아날로그 전자 장치는 아날로그 신호를 사용합니다. 반대로 디지털 신호는 마이크로프로세서, 마이크로컨트롤러, 플립플롭, 논리 게이트와 같은 디지털 전자 장치에 있습니다. 두 신호의 더 나은 기능을 위해 항상 두 신호의 더 나은 기능을 위해 두 신호를 한 형식에서 다른 형식으로 변환해야 합니다. 그래서 우리는 아날로그-디지털 변환기(A