verilog

Verilog는 하드웨어 설명 언어이며 설계자가 RTL 설계를 시뮬레이션하여 논리 게이트로 변환할 필요가 없습니다. 시뮬레이션이 필요한 이유는 무엇입니까?

<노스크립트>

시뮬레이션은 RTL 코드가 의도한 대로 동작하는지 확인하기 위해 다른 시간에 다른 입력 자극을 설계에 적용하는 기술입니다. 기본적으로 시뮬레이션은 설계의 견고성을 검증하기 위해 잘 따라야 하는 기술입니다. 또한 가공된 칩이 실제 세계에서 사용되는 방식과 다양한 입력에 반응하는 방식과 유사합니다.

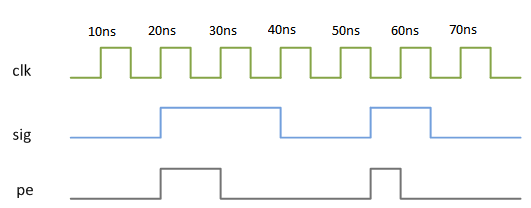

예를 들어, 위의 디자인은 출력 pe 보여진 바와 같이. 시뮬레이션을 통해 관련 신호의 타이밍 다이어그램을 보고 Verilog의 설계 설명이 실제로 어떻게 작동하는지 이해할 수 있습니다.

<노스크립트>

시뮬레이터를 개발하는 여러 EDA 회사가 있습니다. 설계에 대한 다양한 입력에 대한 출력을 파악할 수 있습니다. Verilog는 불연속 이벤트로 정의됩니다. 실행 모델과 다양한 시뮬레이터는 사용자에게 일관된 결과 세트를 제공하기 위해 다양한 알고리즘을 자유롭게 사용할 수 있습니다. Verilog 코드는 여러 프로세스와 스레드로 나뉘며 시뮬레이션 과정에서 다른 시간에 평가될 수 있습니다. 이에 대해서는 나중에 다룹니다.

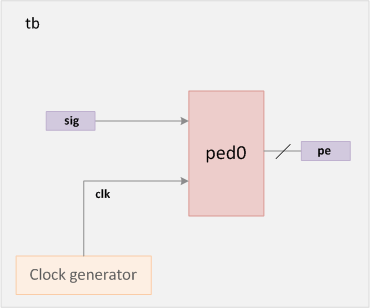

tb라는 테스트벤치는 디자인 모듈을 담는 컨테이너이다. 그러나 이 예에서는 디자인 인스턴스를 사용하지 않았습니다. 두 개의 변수가 있습니다. 또는 신호 특정 시간에 특정 값을 할당할 수 있습니다. clk는 테스트벤치 내에서 생성되는 클럭을 나타냅니다. 이것은 always에 의해 수행됩니다. 5ns마다 클럭 값을 변경하여 명령문. initial 블록에는 서로 다른 시간에 두 신호에 서로 다른 값을 할당하는 일련의 명령문이 포함되어 있습니다.

module tb;

reg clk;

reg sig;

// Clock generation

// Process starts at time 0ns and loops after every 5ns

always #5 clk = ~clk;

// Initial block : Process starts at time 0ns

initial begin

// This system task will print out the signal values everytime they change

$monitor("Time = %0t clk = %0d sig = %0d", $time, clk, sig);

// Also called stimulus, we simply assign different values to the variables

// after some simulation "delay"

sig = 0;

#5 clk = 0; // Assign clk to 0 at time 5ns

#15 sig = 1; // Assign sig to 1 at time 20ns (#5 + #15)

#20 sig = 0; // Assign sig to 0 at time 40ns (#5 + #15 + #20)

#15 sig = 1; // Assign sig to 1 at time 55ns (#5 + #15 + #20 + #15)

#10 sig = 0; // Assign sig to 0 at time 65ns (#5 + #15 + #20 + #15 + #10)

#20 $finish; // Finish simulation at time 85ns

end

endmodule

시뮬레이터는 위의 테스트벤치를 실행한 후 다음과 같은 출력을 제공합니다.

시뮬레이션 로그ncsim> run Time = 0 clk = x sig = 0 Time = 5 clk = 0 sig = 0 Time = 10 clk = 1 sig = 0 Time = 15 clk = 0 sig = 0 Time = 20 clk = 1 sig = 1 Time = 25 clk = 0 sig = 1 Time = 30 clk = 1 sig = 1 Time = 35 clk = 0 sig = 1 Time = 40 clk = 1 sig = 0 Time = 45 clk = 0 sig = 0 Time = 50 clk = 1 sig = 0 Time = 55 clk = 0 sig = 1 Time = 60 clk = 1 sig = 1 Time = 65 clk = 0 sig = 0 Time = 70 clk = 1 sig = 0 Time = 75 clk = 0 sig = 0 Time = 80 clk = 1 sig = 0 Simulation complete via $finish(1) at time 85 NS + 0

시뮬레이션을 통해 RTL 설계의 기능을 분석하고 디버그하기 위해 그래픽으로 나타낼 수 있는 파형으로 설계 및 테스트벤치 신호를 덤프할 수 있습니다. 아래의 파형은 EDA 도구에서 가져온 것으로 각 신호의 시간에 따른 진행 상황을 보여주며 앞서 보여드린 타이밍도와 동일합니다.

<노스크립트>

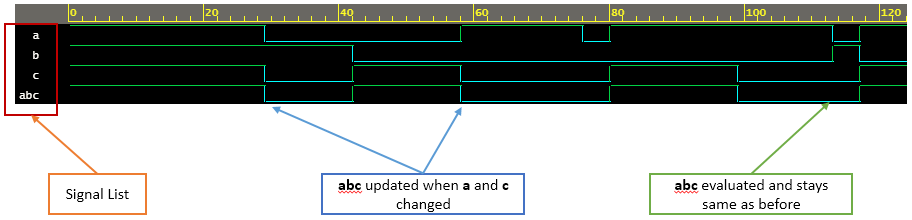

변수 또는 순 값의 모든 변경을 업데이트 이벤트라고 합니다. . 그리고 프로세스는 업데이트 이벤트에 민감합니다. 이러한 프로세스는 업데이트 이벤트가 발생할 때마다 평가되고 평가 이벤트라고 합니다. . 여러 프로세스가 임의로 평가될 가능성 때문에 이벤트 대기열이라는 항목에서 변경 순서를 추적해야 합니다. .

당연히 시뮬레이션 시간에 따라 정렬됩니다. 대기열에 새 이벤트를 배치하는 것을 스케줄링이라고 합니다. . 시뮬레이션 시간은 시뮬레이션되는 회로에 걸리는 실제 시간을 모델링하기 위해 시뮬레이터가 유지 관리하는 시간 값을 참조하는 데 사용됩니다. 위의 예에 대한 시간 값은 나노초로 표시됩니다. ns 타이밍 다이어그램에서.

module des;

wire abc;

wire a, b, c;

assign abc = a & b | c; // abc is updated via the assign statement (process) whenever a, b or c change -> update event

endmodule

<노스크립트>

Verilog를 새로고침하고 예시를 확인하세요!

Verilog 이벤트 대기열은 논리적으로 5개 지역으로 나뉘며 이벤트는 그 중 어느 곳에서나 추가할 수 있습니다. 단, 활성 영역에서만 제거할 수 있습니다.

| 이벤트 | 설명 |

|---|---|

| 활성 | 현재 시뮬레이션 시간에 발생하며 임의의 순서로 처리 가능 |

| 비활성 | 현재 시뮬레이션 시간에 발생하지만 모든 활성 이벤트가 완료된 후에 처리됩니다. |

| 비차단 | 이전 시간에 평가되었지만 활성 및 비활성 이벤트가 완료된 후 현재 시뮬레이션 시간에 할당이 완료됨 |

| 모니터 | 활성, 비활성 및 비차단 이벤트가 모두 완료된 후 처리 |

| 미래 | 미래의 시뮬레이션 시간에 발생 |

시뮬레이션 주기는 모든 활성 이벤트가 처리되는 곳입니다. 이 표준은 몇 가지 경우를 제외하고 특정 일정 순서를 보장합니다. 예를 들어, begin-end 블록 내의 명령문은 나타나는 순서대로만 실행됩니다.

module tb;

reg [3:0] a;

reg [3:0] b;

initial begin // Statements are executed one after the other at appropriate simulation times

a = 5; // At time 0ns, a is assigned 5

b = 2; // In the same simulation step (time 0ns), b is assigned 2

#10 a = 7; // When simulation advances to 10ns, a is assigned 7

end

endmodule

이벤트 대기열 b에 대한 할당을 정의합니다. 에 할당된 후에 발생해야 합니다. .

verilog

매개변수는 다른 사양으로 모듈을 재사용할 수 있도록 하는 Verilog 구성입니다. 예를 들어, 4비트 가산기는 비트 수에 대한 값을 허용하도록 매개변수화될 수 있으며 모듈 인스턴스화 중에 새 매개변수 값이 전달될 수 있습니다. 따라서 N비트 가산기는 4비트, 8비트 또는 16비트 가산기가 될 수 있습니다. 함수 호출 중에 전달되는 함수에 대한 인수와 같습니다. parameter MSB = 7; // MSB is a parameter with a constant value 7 paramet

Verilog 시뮬레이션은 시뮬레이터가 #1이 시간 측면에서 무엇을 의미하는지 알아야 하기 때문에 시간이 정의되는 방식에 따라 다릅니다. `timescale 컴파일러 지시문은 뒤에 오는 모듈의 시간 단위와 정밀도를 지정합니다. 구문 `timescale <time_unit>/<time_precision> // Example `timescale 1ns/1ps `timescale 10us/100ns `timescale 10ns/1ns time_unit time_precision 동안 지연 및 시뮬레