verilog

매개변수는 다른 사양으로 모듈을 재사용할 수 있도록 하는 Verilog 구성입니다. 예를 들어, 4비트 가산기는 비트 수에 대한 값을 허용하도록 매개변수화될 수 있으며 모듈 인스턴스화 중에 새 매개변수 값이 전달될 수 있습니다. 따라서 N비트 가산기는 4비트, 8비트 또는 16비트 가산기가 될 수 있습니다. 함수 호출 중에 전달되는 함수에 대한 인수와 같습니다.

parameter MSB = 7; // MSB is a parameter with a constant value 7

parameter REAL = 4.5; // REAL holds a real number

parameter FIFO_DEPTH = 256,

MAX_WIDTH = 32; // Declares two parameters

parameter [7:0] f_const = 2'b3; // 2 bit value is converted to 8 bits; 8'b3

매개변수는 기본적으로 상수이므로 런타임에 값을 수정하는 것은 불법입니다. 네트, 변수 또는 다른 매개변수에서 이미 사용 중인 이름을 다시 선언하는 것은 불법입니다.

매개변수에는 module의 두 가지 주요 유형이 있습니다. 및 지정 둘 다 범위 사양을 허용합니다. 그러나 일반적으로 저장할 값만큼 넓게 만들어지므로 범위 지정이 필요하지 않습니다.

모듈 매개변수는 모듈 내의 매개변수 정의를 재정의하는 데 사용할 수 있으며 이는 모듈이 컴파일 타임에 다른 매개변수 세트를 갖도록 합니다. 매개변수는 defparam으로 수정할 수 있습니다. 문 또는 모듈 인스턴스 문에서. 매개변수 이름에 대문자를 사용하여 즉시 알아볼 수 있도록 하는 것이 일반적입니다.

아래 표시된 모듈은 매개변수를 사용하여 설계 내에서 버스 너비, 데이터 너비 및 FIFO의 깊이를 지정하고 모듈이 인스턴스화될 때 또는 defparam을 사용하여 새 값으로 재정의할 수 있습니다. 진술.

// Verilog 1995 style port declaration

module design_ip ( addr,

wdata,

write,

sel,

rdata);

parameter BUS_WIDTH = 32,

DATA_WIDTH = 64,

FIFO_DEPTH = 512;

input addr;

input wdata;

input write;

input sel;

output rdata;

wire [BUS_WIDTH-1:0] addr;

wire [DATA_WIDTH-1:0] wdata;

reg [DATA_WIDTH-1:0] rdata;

reg [7:0] fifo [FIFO_DEPTH];

// Design code goes here ...

endmodule

Verilog 포트 선언의 새로운 ANSI 스타일에서는 아래와 같이 매개변수를 선언할 수 있습니다.

module design_ip

#(parameter BUS_WIDTH=32,

parameter DATA_WIDTH=64) (

input [BUS_WIDTH-1:0] addr,

// Other port declarations

);

모듈을 인스턴스화하는 동안 매개변수를 새 값으로 재정의할 수 있습니다. 첫 번째 부분은 새 매개변수가 #( ) 내에 전달되는 d0 이름으로 design_ip라는 모듈을 인스턴스화합니다. . 두 번째 부분은 defparam이라는 Verilog 구성을 사용합니다. 새 매개변수 값을 설정합니다. 첫 번째 방법은 RTL 설계에서 새 매개변수를 전달하는 데 가장 일반적으로 사용되는 방법입니다. 두 번째 방법은 모듈을 다시 인스턴스화할 필요 없이 설계 매개변수를 빠르게 업데이트하기 위해 테스트벤치 시뮬레이션에서 일반적으로 사용됩니다.

module tb;

// Module instantiation override

design_ip #(BUS_WIDTH = 64, DATA_WIDTH = 128) d0 ( [port list]);

// Use of defparam to override

defparam d0.FIFO_DEPTH = 128;

endmodule

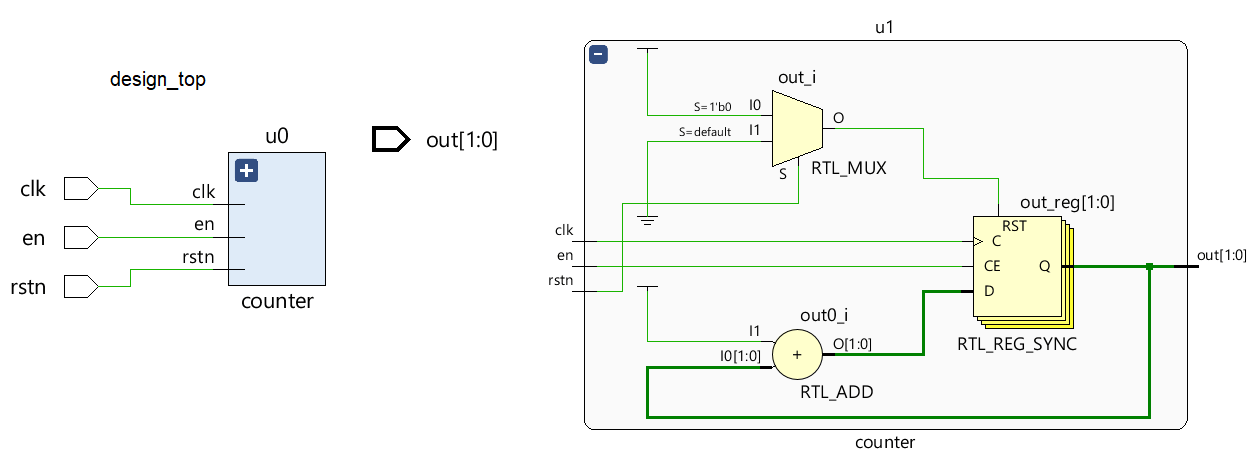

모듈 카운터에는 각각 기본값 2와 0을 갖도록 선언된 두 개의 매개변수 N과 DOWN이 있습니다. N은 카운터의 너비를 효과적으로 제어하는 출력의 비트 수를 제어합니다. 기본적으로 2비트 카운터입니다. Parameter DOWN은 카운터가 증가할지 감소할지를 제어합니다. 매개변수가 0으로 설정되어 있기 때문에 기본적으로 카운터는 감소합니다.

module counter

#( parameter N = 2,

parameter DOWN = 0)

( input clk,

input rstn,

input en,

output reg [N-1:0] out);

always @ (posedge clk) begin

if (!rstn) begin

out <= 0;

end else begin

if (en)

if (DOWN)

out <= out - 1;

else

out <= out + 1;

else

out <= out;

end

end

endmodule

모듈 카운터는 기본 값이 어쨌든 2이기 때문에 필요하지 않더라도 N을 2로 인스턴스화합니다. DOWN은 모듈 인스턴스화 중에 전달되지 않으므로 기본값 0을 취하여 업 카운터로 만듭니다.

module design_top ( input clk,

input rstn,

input en,

output [1:0] out);

counter #(.N(2)) u0 ( .clk(clk),

.rstn(rstn),

.en(en));

endmodule

기본 매개변수가 카운터를 구현하는 데 사용되는 것을 확인하십시오. 여기서 N은 2와 동일하여 2비트 카운터가 되고 DOWN은 0과 동일하여 업 카운터가 됩니다. 카운터의 출력은 최상위 수준에서 연결되지 않은 상태로 유지됩니다.

<노스크립트>

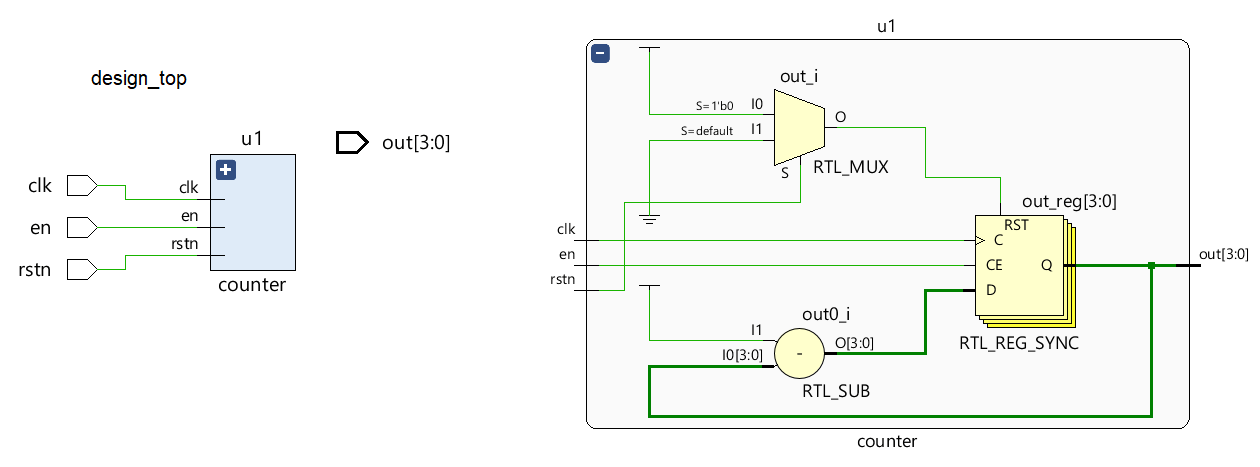

이 경우 모듈 카운터는 N을 4로 인스턴스화하여 4비트 카운터로 만듭니다. DOWN은 모듈 인스턴스화 동안 값 1을 전달하므로 다운 카운터가 구현됩니다.

module design_top ( input clk,

input rstn,

input en,

output [3:0] out);

counter #(.N(4), .DOWN(1))

u1 ( .clk(clk),

.rstn(rstn),

.en(en));

endmodule

<노스크립트>

이는 주로 타이밍 및 지연 값을 제공하는 데 사용되며 specparam을 사용하여 선언됩니다. 예어. 지정 내에서 둘 다 사용할 수 있습니다. 블록과 메인 모듈 본체.

// Use of specify block

specify

specparam t_rise = 200, t_fall = 150;

specparam clk_to_q = 70, d_to_q = 100;

endspecify

// Within main module

module my_block ( ... );

specparam dhold = 2.0;

specparam ddly = 1.5;

parameter WIDTH = 32;

endmodule

| 매개변수 지정 | 모듈 매개변수 |

|---|---|

specparam에 의해 선언됨 | parameter에 의해 선언됨 |

specify 내에서 선언 가능 블록 또는 메인 모듈 내 | 메인 모듈 내에서만 선언 가능 |

| 사양 및 매개변수를 할당할 수 있음 | 사양을 할당할 수 없음 |

| SDF를 사용하여 값을 재정의할 수 있습니다. | 인스턴스 선언 매개변수 값 또는 defparam 재정의하는 데 사용할 수 있습니다. |

verilog

case 문은 주어진 표현식이 목록의 다른 표현식 중 하나와 일치하는지 확인하고 그에 따라 분기합니다. 일반적으로 멀티플렉서를 구현하는 데 사용됩니다. if-else 구문은 확인해야 할 조건이 많고 멀티플렉서 대신 우선 순위 인코더로 합성되는 경우 적합하지 않을 수 있습니다. 구문 Verilog 케이스 명령문은 case로 시작합니다. 키워드이고 endcase로 끝남 예어. 괄호 안의 표현식은 정확히 한 번 평가되고 작성된 순서대로 대안 목록과 비교되며 대안이 주어진 표현식과 일치하는 명령문이 실행됩니다. 여러 문의 블록은 그룹화되

Verilog는 하드웨어 설명 언어이며 설계자가 RTL 설계를 시뮬레이션하여 논리 게이트로 변환할 필요가 없습니다. 시뮬레이션이 필요한 이유는 무엇입니까? 시뮬레이션은 RTL 코드가 의도한 대로 동작하는지 확인하기 위해 다른 시간에 다른 입력 자극을 설계에 적용하는 기술입니다. 기본적으로 시뮬레이션은 설계의 견고성을 검증하기 위해 잘 따라야 하는 기술입니다. 또한 가공된 칩이 실제 세계에서 사용되는 방식과 다양한 입력에 반응하는 방식과 유사합니다. 예를 들어, 위의 디자인은 출력 pe 보여진 바와 같이. 시뮬레이션을 통해