나노물질

이 편지는 V/SiOx에서 선택기 및 메모리 전환을 포함한 이중 기능을 나타냅니다. /AlOy /p ++ 컴플라이언스 전류 제한(CCL)을 간단히 제어하여 Si 저항성 메모리 장치. 단방향 임계값 전환은 1μA의 낮은 CCL로 포지티브 포밍 후에 관찰됩니다. 산소의 V-전극 측으로의 이동은 VOx를 형성합니다. 임계값 스위칭은 금속 절연 전이 현상으로 설명될 수 있는 층입니다. 장치에 적용된 더 높은 CCL(30μA)의 경우 양극성 메모리 스위칭이 얻어지며, 이는 SiOy에서 전도성 필라멘트의 형성 및 파열에 기인합니다. 층. 1.5nm 두께의 Al2Oy 열전도율이 높은 층은 메모리 및 임계값 스위칭의 오프 전류를 낮추는 데 중요한 역할을 합니다. 온도 의존성을 통해 LRS의 고에너지 장벽(0.463 eV)이 확인되며, 이는 저저항 상태에서 비선형성을 유발할 수 있습니다. CCL이 작을수록 비선형성이 높아져 교차점 배열에서 더 큰 배열 크기를 제공합니다. CCL에 따른 메모리와 임계값 전환의 공존은 장치를 의도한 용도에 맞게 제어할 수 있는 유연성을 제공합니다.

<섹션 데이터-제목="배경">저항성 랜덤 액세스 메모리(RRAM)는 빠른 스위칭 속도[1, 2], 낮은 전력 소비[3,4,5,6,7]로 인해 차세대 비휘발성 메모리 기술의 유망한 후보 중 하나입니다. ,8], 다중 레벨 기능 [9,10,11,12,13,14,15], 높은 확장성 [16,17,18,19,20] 및 3D 스태킹 기능 [21,22,23,24,25] ]. 이러한 속성은 주 메모리인 DRAM(Dynamic Random-Access Memory)과 스토리지 메모리인 SSD(Solid State Drive) 간의 성능 격차를 채울 수 있는 SCM(스토리지 클래스 메모리)에 특히 적합합니다. RRAM 장치는 지난 몇 년 동안 많은 발전을 이루었지만 [1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,18,19 ,20,21,22,23,24,25] 그러나 큰 단점이 남아 있습니다. 인접 셀을 통한 스니크 전류가 고밀도 교차점 어레이에서 발생한다는 것입니다[26]. 선택기 부품이 있는 메모리 장치는 이 문제를 극복하기 위해 비선형 전류-전압(I-V) 특성을 제공해야 합니다[26,27,28,29,30,31,32,33,34,35]. 지금까지 CRS(Complementary Resistive Switching)[26], 터널 장벽[27,28,29,30,31,32,33], Ag 기반 임계값 스위칭[34], 다이오드형과 같은 비선형 개념을 가진 다양한 장치 선택기[35, 36], OTS(ovonic threshold switching)[37, 38], MIT(metal-insulator-transition)[39,40,41,42,43]가 보고되었습니다. VOx 전형적인 MIT 재료 중 하나가 광학 및 전기 스위칭 부품으로 잠재적인 응용 분야에서 널리 사용될 수 있기 때문입니다[40,41,42]. SiO2 반도체 산업에서 패시베이션 층으로 널리 사용됩니다. 또한, Si가 풍부한 SiOx (x <2)는 RRAM에서 저항 변화층으로 사용될 수 있다[44,45,46,47,48,49,50,51,52,53,54,55]. SiOx CMOS 공정과의 호환성 및 저렴한 비용 측면에서 다른 많은 재료보다 선호될 수 있습니다. SiOx 기반 RRAM 장치는 높은 확산성을 갖는 Cu 및 Ag와 같은 전극을 사용하여 단순히 브리지를 전도하는 역할의 매개체 역할을 하는 것으로 보고되었습니다[44,45,46,47]. 또 다른 경우에는 SiOx 내부의 원자가 변화 효과에 의해 메모리 전환이 유도됩니다. 이는 산소 결손 또는 양성자 교환 모델의 생성으로 설명될 수 있는 층 [48,49,50,51,52,53,54,55]. 리셋에 앞서 세트 동작을 하는 유니폴라 스위칭에서는 주변 환경에 민감하다. 공중에서 스위칭 성능은 크게 저하됩니다[48,49,50,51,52,53]. 반면, 백워드 스캔 효과가 없는 필라멘트 스위칭은 다양한 SiOx에서 전형적인 단극 및 양극 스위칭을 보여줍니다. 기반 RRAM 장치 [52,53,54].

여기에서는 V/SiOx에서 임계값 스위칭과 메모리 스위칭의 공존을 제시합니다. /AlOy /p ++ 규정 준수 전류 제한(CCL)에 따른 Si 장치. 실리콘 바닥 전극(BE)이 있는 장치는 기존 금속 전극에 비해 몇 가지 장점이 있습니다. 메모리 또는 임계값 스위칭이 있는 RRAM 장치는 트랜지스터의 소스 또는 드레인 측에 직접 연결되며, 이는 임베디드 메모리 및 급경사 장치에 대한 잠재적인 응용 프로그램입니다. Si BE의 직렬 저항으로 인해 오버슈트 전류가 감소할 수 있습니다. 또한, 습식 식각을 통한 실리콘 BE의 나노 팁과 실리콘 표면의 도핑 농도 조정은 스위칭 성능을 향상시킬 수 있습니다. AlOy 절연 특성을 가진 큰 밴드 갭인 레이어는 임계값 및 메모리 스위칭 시 작동 전류를 낮추는 데 도움이 됩니다. SiOx 레이어는 높은 CCL에서 메모리 스위칭 레이어 역할을 하는 반면 낮은 CCL에서 V TE에 산소를 공급하는 역할을 하여 임계값 스위칭을 제공합니다.

V/SiOx /AlOy /p ++ Si 장치는 다음과 같이 제작되었습니다. 첫째, BF2 이온은 40keV의 가속 에너지와 5 × 10 15 의 도즈로 주입되었습니다. cm −2 고농도로 도핑된 Si BE에 Si 기판으로. 격자 손상은 10분 동안 1050°C에서 어닐링 공정에 의해 경화되었습니다. 많이 도핑된 Si BE의 시트 저항은 30.4Ω/□였습니다. 다음으로 1.5nm 두께의 AlOy 층은 H2를 사용하여 원자층 증착(ALD) 시스템에 의해 증착되었습니다. O 및 Al(CH3 )3 및 5.5nm 두께의 SiOx 층은 5% SiH4를 반응시켜 플라즈마 강화 화학 기상 증착(PECVD)을 거쳤습니다. /N2 (160sccm), N2 O(1300sccm) 및 N2 (240sccm), 300°C에서 이어서, Ar 가스(30sccm)로 V 타겟을 DC 스퍼터링하여 직경 100μm의 50nm 두께의 바나듐(V) 상부 전극(TE)을 증착했습니다. 마지막으로 VTE의 추가 산화를 방지하기 위해 DC 스퍼터링으로 보호층으로 50nm 두께의 Al을 증착했습니다. 모든 전기적 특성은 실온에서 각각 Keithley 4200-SCS SPA(반도체 매개변수 분석기) 및 4225-PMU 초고속 전류-전압(I-V) 모듈을 사용하여 DC 전압 스윕 및 펄스 모드를 통해 특성화되었습니다. 장치 작동을 위해 TiN BE를 접지하고 Ni TE 바이어스를 제어했습니다.

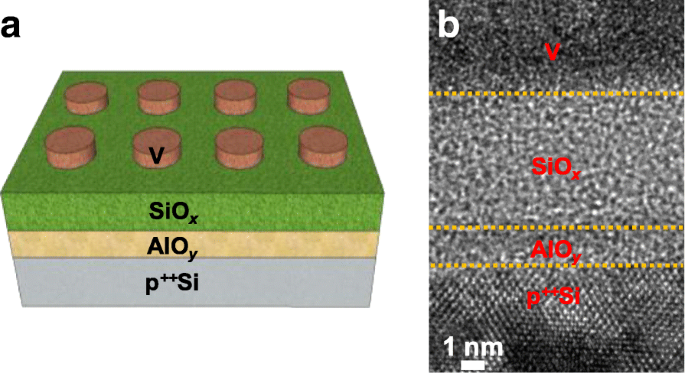

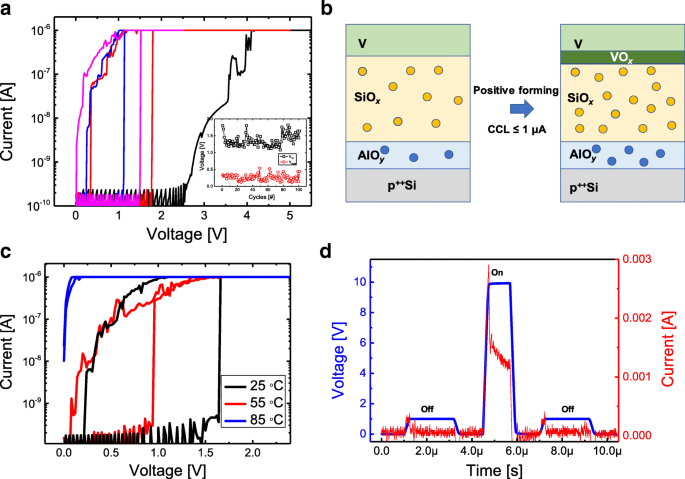

그림 1a는 V/SiOx의 개략적인 구조를 보여줍니다. /AlOy /p ++ 시디바이스. 3개의 비정질 V, SiOx , 및 AlOy 그림 1b와 같이 투과전자현미경(TEM) 단면 이미지로 단결정 Si층과 단결정층을 관찰할 수 있습니다. SiOx의 두께 및 AlOy 레이어는 각각 5.5 및 1.5nm입니다. 두 유전체 필름의 조성비를 확인하기 위해 XPS 분석을 수행했습니다(추가 파일 1). x SiOx의 값 그리고 y AlOy의 값 각각 0.88과 1.33이다. 우리의 SiOx SiO2와 비교하여 PECVD를 사용한 필름 건식 산화를 사용하여 증착된 것은 훨씬 더 낮은 온도에서 증착되고 훨씬 더 많은 결함을 가지므로 상대적으로 더 낮은 전압에서 저항성 스위칭에 적합합니다. 그림 2a는 V/SiOx의 일반적인 임계값 스위칭을 보여줍니다. /AlOy /p ++ 시디바이스. 포지티브 포밍 프로세스를 통한 초기 스위칭은 유전층이 초기에 결함이 더 작기 때문에 후속 임계값 스위칭보다 더 높은 전압이 필요합니다. 1μA의 CCL이 SiOx에서 과도한 전도성 필라멘트 형성을 방지하기 위해 장치에 적용됩니다. 층. 누설 전류는 이전에 보고된 VOx 임계값 전환과 비교하여 매우 낮습니다(1V에서 100pA). . 이 이점은 Al2에 기인합니다. O3 SiO2에 비해 유전율과 열전도율이 더 높음 . Off 상태는 필라멘트가 쉽게 파열되어 남은 필라멘트가 없기 때문에 절연성이 있습니다. 임계값 전환을 위한 가능한 메커니즘은 SiOx에서 공급된 산소로부터 VTE가 산화되는 것입니다. 그림 2b와 같이 포지티브 성형 공정 중 층. VOx의 전기적 특성 V TE와 SiOx 사이 층이 절연 상태에서 금속 상태로 변화하여 급격한 저항 변화를 일으킬 수 있습니다. 1μA의 낮은 CCL은 SiOx 내부에 효율적인 전도성 필라멘트를 생성하기에 충분하지 않습니다. 영화. 따라서 SiOx 절연 특성이 있는 것은 오프 전류를 줄이는 또 다른 원인이 될 수 있습니다. V/SiOx의 네거티브 성형 공정용 /AlOy /p ++ Si 기기, 임계값 전환이 관찰되지 않습니다(추가 파일 1 참조). V TE에 음의 바이어스가 인가되면 산화물의 움직임이 Si BE 쪽으로 이동하므로 V TE는 더 이상 VOx로 임계값 전환에 참여할 수 없습니다. . 그림 2a의 삽입은 임계 전압(Vth ) 및 홀드 전압(Vhold ) 100주기 동안 V번째 거의 무한대에 가까운 기울기로 전류가 급격히 증가하는 곳은 1.08~1.82V이며 Vhold입니다. 이 시점에서 고저항 상태로의 전류 반환은 0.12~0.54V 사이입니다. 그림 2c는 다양한 온도에서 온 전류의 I-V 특성을 보여줍니다. 25°C 및 55°C에서는 거의 유사한 임계값 전환을 나타내지만 85°C의 더 높은 온도에서 I-V 곡선은 임계값 전환 속성을 잃습니다. VOx는 잘 알려져 있습니다. 고온에서 MIT를 잃습니다. 따라서 이 결과는 VOx 임계값 전환의 주요 원인입니다. 그림 2d는 임계값 전환의 과도 특성을 보여줍니다. 진폭이 1V인 펄스는 폭이 1μs인 펄스를 쓰기 전후의 읽기 전류를 모니터링했습니다. 높은 진폭의 펄스를 소자에 인가하면서 고전류를 모니터링한 후, V/SiOx /AlOy /p ++ Si 소자는 쓰기 펄스가 제거된 직후 전류를 차단했습니다. 위에서 분석한 선택기 속성은 1μA 미만의 메모리 요소 작동과 결합할 때 사용할 수 있습니다[55, 56].

<사진>

V/SiOx의 장치 구성 /AlOy /p ++ 시. 아 개략도 및 b TEM 이미지

<그림>

V/SiOx의 단방향 임계값 스위칭 /AlOy /p ++ 1μA의 CCL로 포지티브 성형이 적용될 때의 Si입니다. 아 일반적인 I-V 곡선. ㄴ 성형 공정의 개략도. ㄷ 온도 의존성에 따른 I-V 특성. d 과도 특성

그림 3a는 V/SiOx의 바이폴라 저항성 스위칭을 보여줍니다. /AlOy /p ++ 100μA의 CCL로 포지티브 성형 후 Si 소자. 그 다음, 음의 전압을 스위핑하여 저항이 급격히 증가하는 리셋 프로세스를 수행하고 장치를 HRS(고저항 상태)로 전환합니다. 그런 다음 저항이 급격히 감소하는 설정 프로세스가 양의 바이어스 전압에서 발생하여 장치가 LRS(저저항 상태)로 되돌아갑니다. 전도성 필라멘트의 특성을 이해하기 위해 정규화된 전도도와 온도 의존성을 관찰합니다. LRS의 전도는 전도 필라멘트의 특성을 간접적으로 알려주는 중요한 지침입니다. 그림 3b는 정규화된 컨덕턴스(GN ) 이는 동적 전도도(Gd)로 정의됩니다. ) 정적 전도도(G0)로 나눕니다. ) V/SiOx의 I–V 곡선용 /AlOy /p ++ 온도가 다른 LRS의 Si 소자. 온도에 관계없이 GN 전압이 0일 때 값은 1로 수렴합니다. 이를 통해 Schottky emission, Fowler-Nordheim 터널링 및 Child의 법칙과 같은 잘 알려진 전도 메커니즘을 배제할 수 있습니다(I~V 2 ) 공간 전하 제한 전류(SCLC)에서. 금속 오믹 전도도 그림 3c와 같이 온도 의존성을 고려하여 배제할 수 있습니다. 온도가 증가함에 따라 저항이 감소하는 것은 전도성 필라멘트가 반도체 특성을 가지고 있음을 시사합니다. 따라서 V가 SiOx로 침투하는 것을 배제할 수 있습니다. V/SiOx의 주 전도성 필라멘트용 층 /AlOy /p ++ LRS의 Si 장치. 따라서 V/SiOx의 바이폴라 메모리 동작은 /AlOy /p ++ Si 디바이스는 SiOx의 고유 스위칭에 의해 지배됩니다. . 또한 양의 전류와 음의 전류가 크게 다르지 않은 것으로 확인되어 쇼트키 발광과 같은 계면형보다는 벌크 전도가 지배적임을 알 수 있다. 위에서 언급한 정규화된 컨덕턴스를 고려하면 두 가지 가능한 벌크 우성 전도 메커니즘이 있습니다. 첫 번째는 다음 공식에 따른 호핑 전도입니다.

$$ J={qnav}_o{e}^{-q{\o}_T/ kT}{e}^{qaV/2 dkT} $$

V/SiOx의 메모리 스위칭 /AlOy /p ++ 30μA의 CCL로 포지티브 성형이 적용될 때의 Si입니다. 아 일반적인 I-V 곡선. ㄴ 정규화된 컨덕턴스. ㄷ (I) 대 1000/T에서. d 성형 공정의 개략도

여기서 q , n , 아 , ø T , v 오 , 및 d 는 각각 전하, 공간전하의 농도, 호핑거리의 평균, 호핑을 위한 전자장벽높이, 고유진동주파수, 유전막의 두께이다. ø T ln(I) 대 1000/T의 선형 플롯의 기울기에서 계산된 값은 그림 3c와 같이 0.463eV입니다. Ea 간의 관계에서 계산된 값 V는 5.17nm이며, 이는 SiOx에서 형성된 전도성 필라멘트를 나타냅니다. 강하지 않고 HRS 상태에 가깝습니다. 다른 전도 메커니즘인 P-F(Poole-Frenkel) 방출은 추가 파일 1에서 다루었습니다. 위의 결과를 바탕으로 V/SiOx의 메모리 작동에서 전도성 필라멘트 모델 /AlOy /p ++ Si 장치는 그림 3d에 나와 있습니다. 포지티브 포밍 공정에서는 V TE 측에서 산화 공정이 진행되었지만 높은 CCL로 인해 SiOx 내부에 전도성 필라멘트가 형성될 수 있습니다. 및 AlOy 산소 결손의 이동 때문입니다. 재설정 과정에서 형성 및 설정 반대의 전기장이 산소를 유도하고 산소 결손과 재결합하여 전도성 필라멘트가 파열됩니다. 선택기 및 메모리 작업은 동일한 셀에서 관찰됩니다. 임계값 동작이 발생한 후 스위치가 완전히 꺼진 후 메모리 동작이 가능합니다. 그러나 메모리 동작의 리셋 전환이 완전히 꺼지지 않았기 때문에 역방향은 불가능합니다.

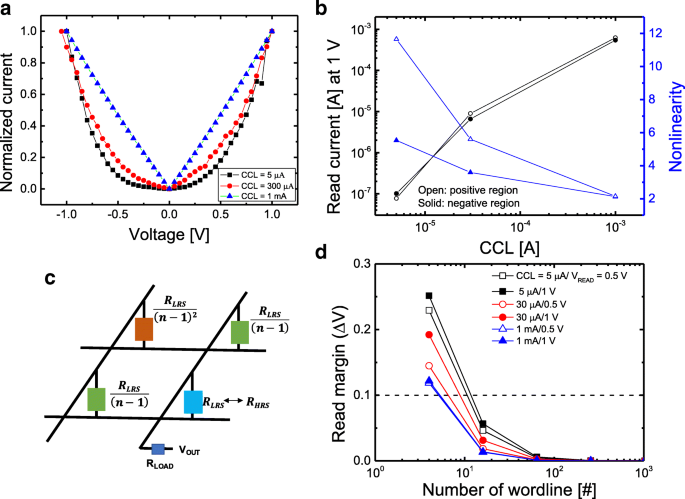

그림 4a는 V/SiOx의 LRS에서 정규화된 I-V 곡선을 보여줍니다. /AlOy /p ++ 다양한 CCL 조건(5μA, 30μA, 1mA)에 대한 저전압 영역(0~1V)의 Si 장치. 여기서 정규화된 I-V 곡선은 각 전압에서의 전류를 1V에서의 전류로 나눈 값으로 정의된다. CCL에 따른 LRS 전류의 레벨이 다양하기 때문에 전류값을 1V로 설정하여 쉽게 비교할 수 있다. 비선형성. CCL이 감소함에 따라 더 낮은 전압 영역에서 전류가 억제됨을 관찰할 수 있습니다. 보다 정량적인 관계를 도출하기 위해 비선형성을 VREAD에서 전류의 비율로 정의합니다. VREAD의 절반에 . 그림 4b는 V/SiOx에 대한 CCL의 함수로서 1V 및 비선형성에서의 읽기 전류를 보여줍니다. /AlOy /p ++ 시디바이스. CCL 감소로 인한 읽기 전류의 감소는 전도성 필라멘트가 미세해지고 비선형성이 증가함을 시사합니다. 진성 산화규소막은 단일층에서도 높은 비선형성을 나타낸다. 고유한 비선형 특성은 실리콘 계면보다는 실리콘 산화물의 벌크 특성에 기인합니다. CCL이 작을수록 SiOx에서 열화가 덜 발생합니다. , 따라서 HRS에 비해 LRS에서 트랩 에너지 준위의 저하가 최소화될 수 있다. 따라서 더 낮은 CCL이 소자에 적용될 때 더 높은 에너지 장벽은 LRS 상태에서 비선형성을 최대화할 수 있다. 유사하게, TaOx에서 P-F 방출로 설명되는 전도 /TiOy 스택은 높은 비선형성을 보장합니다[57]. 또 다른 가능성은 산화물의 유전 상수가 더 작기 때문에 필드의 집중으로 인해 산화물 막에 더 많은 패스가 만들어지는 것입니다. 이것은 Al2의 터널 장벽 역할을 할 것으로 예상할 수 있는 산화물 층의 트랩 에너지 준위를 낮추는 결과를 초래할 수 있습니다. O3 . n에서 읽기 마진(∆V)을 얻으려면 × n 교차점 배열에서는 그림 4c와 같이 단순화된 등가 회로를 사용합니다. 최악의 경우를 고려하여 인접 셀은 LRS와 부하저항(RL ) LRS 저항. ∆V는 VOUT LRS 및 VOUT에서 HRS에서. 그림 4d는 ∆V를 워드 라인 수(n ) V/SiOx의 경우 /AlOy /p ++ 시디바이스. CCL이 작을수록 비선형성이 증가하기 때문에 ∆V가 높아집니다. 10% 읽기 마진이 확보되면 어레이는 5μA의 CCL의 경우 약 10×10 이상, 1mA의 CCL의 경우 5×5까지 확장할 수 있습니다. 스니크 전류를 견딜 수 있는 어레이 크기는 충분하지 않지만 선택기 기능이 있는 장치가 V/SiOx로 연결된 경우 어레이 크기를 확장하는 데 도움이 됩니다. /AlOy /p ++ 시디바이스. 모든 CCL에서 0.5V 읽기와 비교하여 1V에서 읽기로 더 높은 비선형성을 갖습니다. 비록 낮은 VREAD 읽기 작업에서 낮은 정적 전력으로 이어지며 비선형성 값이 작아집니다. 이는 SiOx에서 전기장이 더 적기 때문입니다. /AlOy 더 작은 VREAD의 레이어 .

<그림>

V/SiOx의 비선형 특성 /AlOy /p ++ 메모리 스위칭용 Si. 아 CCL이 다른 I–V 곡선. ㄴ CCL의 함수로 전류 및 비선형성을 읽습니다. ㄷ 교차점 배열의 등가 회로. d 다양한 CCL 및 읽기 전압에 대한 워드 라인 번호의 함수로서의 읽기 마진

이 작업에서 V/SiOx /AlOy /p ++ CCL을 간단히 제어하여 선택기와 메모리 기능을 동시에 갖는 Si 소자를 연구한다. 1μA 이하의 CCL이 적용되면 선택기 적용에 대해 단방향 임계값 전환이 관찰됩니다. 포지티브 포밍은 V 전극과 VOx의 MIT 현상을 산화시킵니다. 임계값 전환을 유발할 수 있습니다. AlOy 레이어는 10 4 의 높은 선택도를 얻을 수 있습니다. 오프 전류를 낮춤으로써. 반면, 5μA 이상의 CCL을 적용하면 SiOx에 효과적인 전도성 필라멘트가 형성되어 메모리 스위칭이 관찰됩니다. 층. CCL이 낮을수록 비선형성이 커져 교차점 배열의 크기를 늘리는 데 도움이 됩니다.

원자층 증착

하단 전극

규정 준수 전류 제한

보완 저항 스위칭

동적 랜덤 액세스 메모리

고저항 상태

전류-전압

저저항 상태

금속-절연체-전이

Ovonic 임계값 전환

플라즈마 강화 화학 기상 증착

풀 프렌켈

저항성 랜덤 액세스 메모리

공간 전하 제한 전류

스토리지 클래스 메모리

반도체 매개변수 분석기

솔리드 스테이트 드라이브

상단 전극

투과전자현미경

바나듐

나노물질

아두이노 PWM Arduino의 프로그래밍 및 기능 PWM이란 무엇입니까? PWM 펄스 폭 변조의 약자 . 이 기술은 전압 변동이 필요한 거의 모든 장치에 널리 사용됩니다. PWM에서 안정된 DC 전압은 펄스 폭이 변하는 구형파로 변환되며 펄스 폭이 ON인 시간에 대한 파형의 총 시간 주기(T)의 비율을 듀티 사이클이라고 합니다. 이 기술은 PDT(Pulse Duration Technique)라고도 합니다. MOSFET, 트랜지스터와 같은 현대 전자 제품의 전원 스위치는 PWM에 필요하며, PWM 신호가 매우 높은 부하를 전달해야

연결성 및 데이터 수집은 기계 가공 및 제조 분야에서 가장 중요한 주제가 되었습니다. 공작 기계 OEM 및 액세서리 공급업체는 장비에 자동 피드백/모니터링 기능을 지속적으로 구축하여 작업장에서 작업장 프로세스를 더 잘 제어할 수 있도록 합니다. 예를 들어 Hainbuch America Corp.는 TopPlus IQ 척 및 맨드릴에 지능형 기능을 제공하고 있습니다. 이러한 지능형 워크홀딩 장치는 부품 측정 및 워크홀딩 매개변수 모니터링 기능을 포함하는 센서와 통합됩니다. 분석 및 프로세스 조정을 위해 데이터를 기계 컨트롤러에 전달하