산업기술

지금까지 트랜지스터 논리 회로에 대한 분석은 TTL으로 제한되었습니다. 바이폴라 트랜지스터가 사용되는 설계 패러다임 및 부동 입력의 일반적인 전략은 "높음"(Vcc에 연결됨)과 동일합니다. ) 입력 및 이에 따라 "개방형 수집기" 출력 단계의 허용이 유지됩니다. 그러나 이것이 논리 게이트를 구축할 수 있는 유일한 방법은 아닙니다.

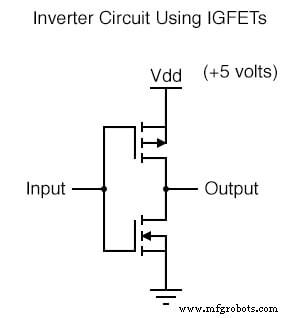

전계 효과 트랜지스터, 특히 절연 게이트 종류는 게이트 회로 설계에 사용할 수 있습니다. 전류 제어 장치가 아닌 전압 제어 장치이기 때문에 IGFET는 매우 단순한 회로 설계를 허용하는 경향이 있습니다. 예를 들어, P 및 N 채널 IGFET를 사용하여 구축된 다음 인버터 회로를 살펴보십시오.

"Vdd ” 레이블이 양극 전원 공급 장치 단자에 있습니다. 이 레이블은 "Vcc와 동일한 규칙을 따릅니다. " TTL 회로:접지를 기준으로 전계 효과 트랜지스터의 드레인에 인가되는 일정한 전압을 나타냅니다.

낮은 입력

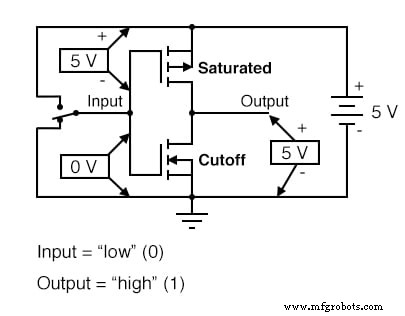

이 게이트 회로를 전원과 입력 스위치에 연결하고 동작을 살펴보자. 이 IGFET 트랜지스터는 E형(향상 모드)이므로 보통 꺼짐입니다. 장치.

on 바이어스하려면 올바른 극성의 게이트와 드레인 사이(실제로는 게이트와 기판 사이)에 인가된 전압이 필요합니다. .

상부 트랜지스터는 P-채널 IGFET입니다. 채널(기판)이 게이트(기판을 기준으로 게이트 음수)보다 더 포지티브하게 되면 채널이 향상되고 소스와 드레인 사이에 전류가 허용됩니다.

따라서 위의 그림에서 상단 트랜지스터가 켜져 있습니다. 게이트와 기판(소스) 사이의 전압이 0인 하위 트랜지스터는 정상 모드에 있습니다. 꺼짐 .

따라서 이 두 트랜지스터의 동작은 게이트 회로의 출력 단자가 Vdd에 견고하게 연결되도록 하는 것입니다. 접지에 대한 매우 높은 저항 연결. 이것은 입력의 "낮음"(0) 상태에 대해 출력을 "높음"(1)으로 만듭니다.

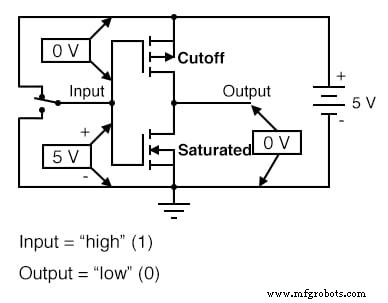

다음으로 입력 스위치를 다른 위치로 이동하고 어떤 일이 일어나는지 살펴보겠습니다.

이제 아래쪽 트랜지스터(N-채널)는 게이트와 기판(채널) 사이에 인가된 올바른 극성의 충분한 전압을 갖고 있기 때문에 포화 상태가 됩니다(게이트에서 양수, 채널에서 음수). 게이트와 기판 사이에 전압이 0인 상부 트랜지스터는 정상 모드에 있습니다. 꺼짐 .

따라서 이 게이트 회로의 출력은 이제 "낮음"(0)입니다. 분명히 이 회로는 인버터 또는 NOT 게이트의 동작을 나타냅니다.

바이폴라 트랜지스터 대신 전계 효과 트랜지스터를 사용하여 인버터 게이트의 설계를 크게 단순화했습니다. 이 게이트의 출력은 가장 단순한 TTL 회로의 경우처럼 플로팅되지 않습니다. 이 게이트는 부하 전류를 소싱 및 싱킹할 수 있는 자연스러운 "토템폴" 구성을 가지고 있습니다.

이 게이트 회로의 우아한 디자인의 핵심은 상보적입니다. P 채널 및 N 채널 IGFET 모두 사용. IGFET는 MOSFET(M etal-O xide-S 반도체 F 필드 E 효과 T (ransistor), 이 회로는 P-채널과 N-채널 트랜지스터를 함께 사용합니다. 이와 같은 게이트 회로에 주어진 일반적인 분류는 CMOS입니다. :C 보완 M etal O xide S 반도체.

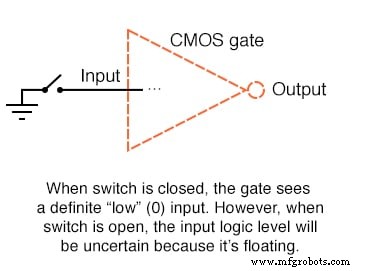

CMOS 회로는 전계 효과 트랜지스터의 고유한 비선형성으로 인해 어려움을 겪지 않습니다. 왜냐하면 디지털 회로의 트랜지스터는 항상 포화 상태에서 작동하기 때문입니다. 또는 컷오프 모드 및 절대 활성 방법. 그러나 입력은 정전기(정전기) 소스에서 생성된 고전압에 민감하며 부동 상태로 두면 가짜 전압 소스에 의해 "높음"(1) 또는 "낮음"(0) 상태로 활성화될 수도 있습니다.

이러한 이유로 CMOS 논리 게이트 입력이 어떤 상황에서도 부동하도록 허용하는 것은 바람직하지 않습니다. 이것은 부동 입력이 "높은"(1) 논리 레벨로 안전하게 해석되는 TTL 게이트의 동작과 매우 다릅니다.

이것은 CMOS 논리 게이트에 대한 입력이 단일 스로우 스위치에 의해 구동되는 경우 문제를 일으킬 수 있습니다. 여기서 한 상태에서는 입력이 Vdd 중 하나에 단단히 연결되어 있습니다. 또는 접지이고 다른 상태는 입력 부동(아무것도 연결되지 않음):

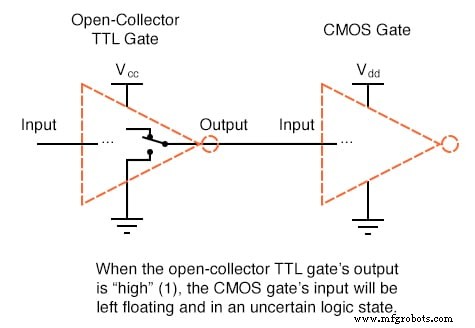

또한 이 문제는 CMOS 게이트 입력이 오픈 컬렉터에 의해 구동되는 경우에 발생합니다. TTL 게이트. 이러한 TTL 게이트의 출력은 "하이"(1)가 되면 부동하므로 CMOS 게이트 입력은 불확실한 상태로 남게 됩니다.

풀업 저항기

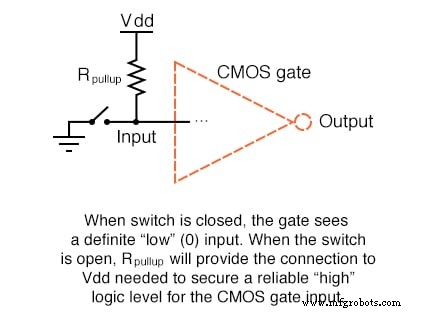

다행히도 CMOS 논리 회로에서 자주 사용되는 이 딜레마에 대한 쉬운 솔루션이 있습니다. 단일 스로우 스위치(또는 다른 종류의 게이트 출력이 둘 다 불가능할 때마다 소싱 및 싱킹 전류)는 Vdd에 연결된 저항인 CMOS 입력을 구동하는 데 사용됩니다. 또는 접지는 구동 장치의 출력이 플로팅되는 상태에 대한 안정적인 논리 레벨을 제공하는 데 사용될 수 있습니다.

이 저항의 값은 중요하지 않습니다. 일반적으로 10kΩ이면 충분합니다. 부동 신호 소스의 경우 "높은"(1) 논리 레벨을 제공하는 데 사용되는 경우 이 저항을 풀업 저항이라고 합니다. :

풀다운 저항기

이러한 저항이 부동 신호 소스의 경우 "낮은"(0) 논리 레벨을 제공하는 데 사용되는 경우 이를 풀다운 저항이라고 합니다. . 다시 말하지만, 풀다운 저항의 값은 중요하지 않습니다.

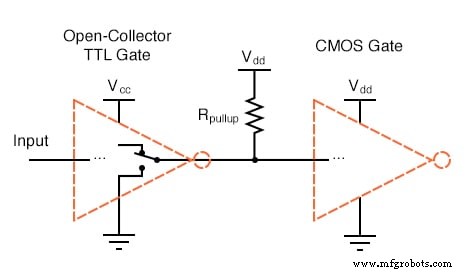

오픈 컬렉터 TTL 출력은 항상 싱크, 소싱 없음, 전류, 풀업업을 하지 않기 때문에 이러한 출력을 CMOS 게이트 입력에 연결할 때 저항이 필요합니다.

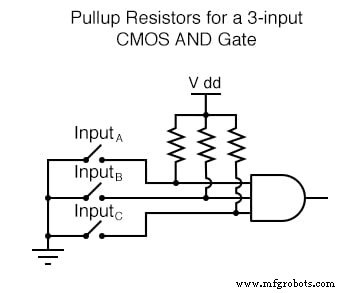

다중 풀업 및 풀다운 저항기

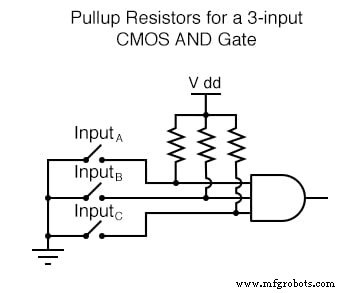

앞의 예에서 사용된 CMOS 게이트는 모두 인버터(단일 입력)였지만 풀업 및 풀다운 저항의 동일한 원리가 다중 입력 CMOS 게이트에 적용됩니다. 물론 각 게이트 입력에 대해 별도의 풀업 또는 풀다운 저항이 필요합니다.

이것은 다음 질문으로 이어집니다. AND, NAND, OR 및 NOR와 같은 다중 입력 CMOS 게이트를 어떻게 설계합니까? 당연히 이 질문에 대한 대답은 TTL에 비해 CMOS 인버터와 유사한 설계 단순성을 보여줍니다.

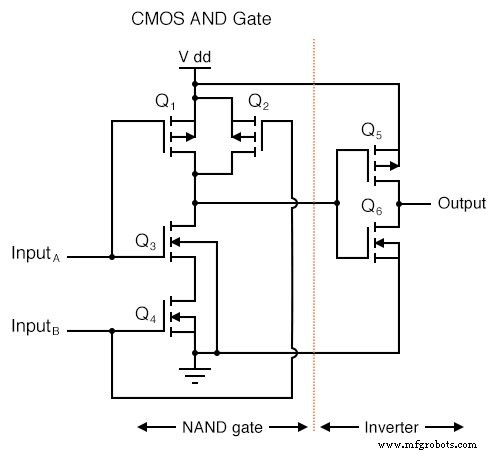

예를 들어 다음은 CMOS NAND 게이트의 개략도입니다.

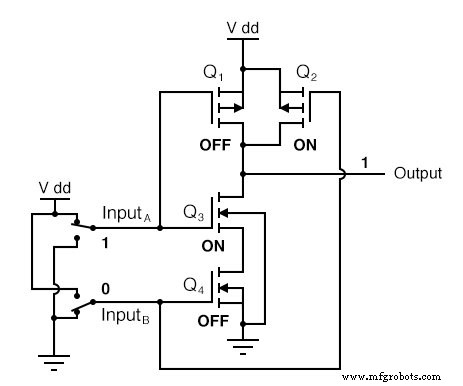

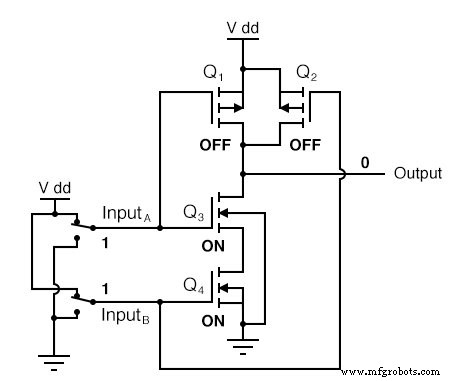

트랜지스터 Q1 및 Q3 인버터 회로의 직렬 연결된 보완 쌍과 유사합니다. 둘 다 동일한 입력 신호(입력 A)에 의해 제어되며, 입력이 "하이"(1)일 때 상위 트랜지스터가 꺼지고 하위 트랜지스터가 켜지며 그 반대의 경우도 마찬가지입니다.

트랜지스터 Q2 및 Q4 동일한 입력 신호(입력 B)에 의해 유사하게 제어되며 동일한 입력 논리 레벨에 대해 동일한 켜기/끄기 동작을 나타내는 방법도 있습니다. 두 쌍의 상위 트랜지스터(Q1 및 Q2 ) 소스 및 드레인 단자가 병렬로 연결되어 있는 반면 하위 트랜지스터(Q3 및 Q4 )는 직렬로 연결되어 있습니다.

이것이 의미하는 바는 둘 중 하나 상단 트랜지스터가 포화되고 둘 다인 경우에만 "낮음"(0)이 됩니다. 낮은 트랜지스터 포화도.

다음 그림 시퀀스는 입력 논리 레벨(00, 01, 10, 11)의 네 가지 가능성 모두에 대한 이 NAND 게이트의 동작을 보여줍니다.

TTL NAND 게이트와 마찬가지로 CMOS NAND 게이트 회로는 AND 게이트 생성을 위한 시작점으로 사용될 수 있습니다. 추가해야 하는 것은 출력 신호를 반전시키는 트랜지스터의 또 다른 단계입니다.

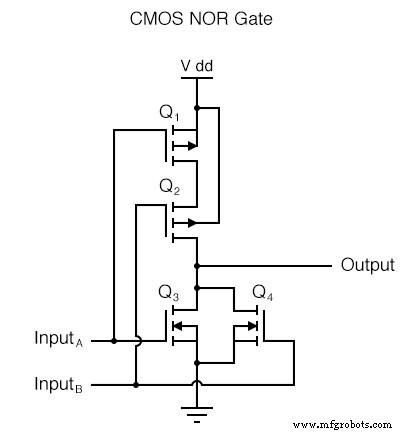

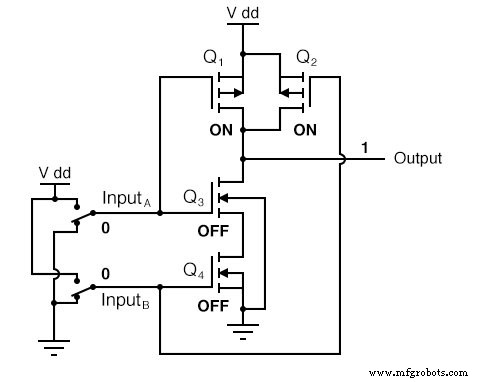

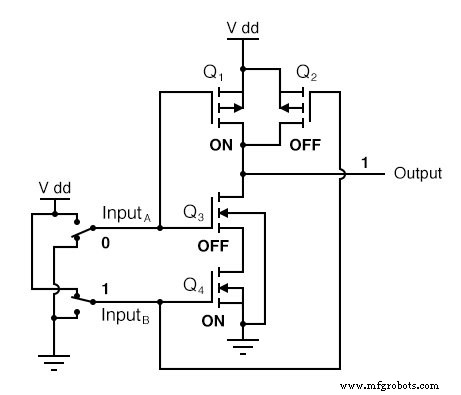

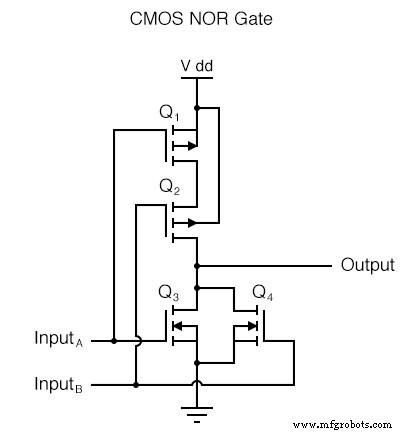

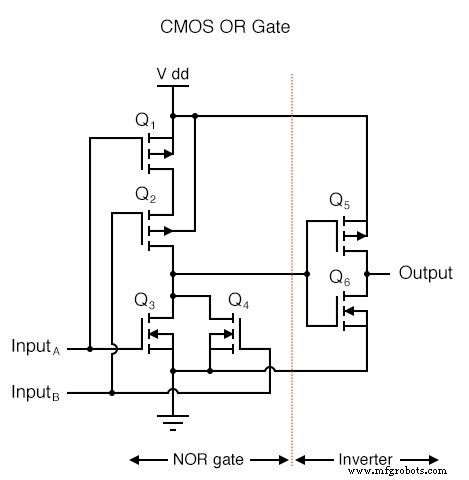

CMOS NOR 게이트 회로는 트랜지스터 배열이 다르다는 점을 제외하고는 NAND 게이트와 마찬가지로 4개의 MOSFET을 사용합니다. 두 개의 병렬 소싱 대신 Vdd에 연결된 (상단) 트랜지스터 및 2개의 직렬 연결된 싱킹 (하단) 트랜지스터가 접지에 연결된 경우 NOR 게이트는 다음과 같이 직렬 연결된 2개의 소싱 트랜지스터와 2개의 병렬 연결된 싱킹 트랜지스터를 사용합니다.

NAND 게이트와 마찬가지로 트랜지스터 Q1 및 Q3 트랜지스터 Q2와 마찬가지로 보완 쌍으로 작동 및 Q4 . 각 쌍은 단일 입력 신호로 제어됩니다. 둘 중 하나인 경우 입력 A 또는 입력 B는 "높음"(1), 낮은 트랜지스터 중 하나 이상(Q3 또는 Q4 )이 포화되어 출력이 "낮음"(0)이 됩니다.

둘 다인 경우에만 입력이 "낮음"(0)이면 하위 트랜지스터가 모두 차단 모드에 있고 상위 트랜지스터가 모두 포화되어 출력이 "높음"(1)이 되는 데 필요한 조건이 됩니다. 물론 이 동작은 NOR 논리 함수를 정의합니다.

OR 기능은 출력에 인버터 단계를 추가하여 기본 NOR 게이트에서 구축할 수 있습니다.

TTL 기술을 사용하여 구성할 수 있는 모든 게이트가 CMOS에서 복제될 수 있는 것처럼 보이지만 논리 설계의 이 두 "패밀리"가 여전히 공존하는 이유는 무엇입니까? 대답은 TTL과 CMOS 모두 고유한 장점이 있다는 것입니다.

TTL과 CMOS의 비교 목록에서 가장 먼저 언급되는 것은 전력 소비 문제입니다. 이러한 성능 측정에서 CMOS는 확실한 승자입니다. CMOS 게이트 회로의 상보적 P 및 N 채널 MOSFET 쌍은 (이상적으로는) 절대로 동시에 전도되지 않기 때문에 Vdd 부하에 전류를 공급하는 데 필요한 전류를 제외하고 전원 공급 장치. 반면에 TTL은 만들어진 바이폴라 트랜지스터의 바이어싱 요구 사항으로 인해 항상 약간의 전류가 흐르지 않으면 작동할 수 없습니다.

그러나 이 이점에 대한 주의 사항이 있습니다. TTL 게이트의 전력 소모는 작동 상태에 관계없이 일정하게 유지되는 반면 CMOS 게이트는 입력 신호의 주파수가 상승함에 따라 더 많은 전력을 소모합니다. CMOS 게이트가 정적(불변) 조건에서 작동하면 제로 전력(이상적으로는)을 소모합니다.

그러나 CMOS 게이트 회로는 모든 출력 상태가 "낮음"에서 "높음"으로 또는 그 반대로 전환되는 동안 과도 전류를 끌어옵니다. 따라서 CMOS 게이트가 모드를 더 자주 전환할수록 Vdd 따라서 더 큰 주파수에서 더 큰 전력 손실이 발생합니다.

CMOS의 장점

CMOS 게이트는 또한 MOSFET이 전류 제어가 아닌 전압 제어 장치이기 때문에 TTL 게이트보다 구동 게이트 출력에서 훨씬 적은 전류를 소비합니다. 이것은 하나의 게이트가 TTL 입력보다 더 많은 CMOS 입력을 구동할 수 있음을 의미합니다. 단일 게이트 출력이 구동할 수 있는 게이트 입력의 수를 측정하는 것을 팬아웃이라고 합니다. .

CMOS 게이트 설계가 TTL에 비해 누리는 또 다른 이점은 허용 가능한 전원 전압 범위가 훨씬 더 넓다는 것입니다. TTL 게이트는 전원 공급 장치(Vcc ) 4.75~5.25볼트 사이의 전압에서 CMOS 게이트는 일반적으로 3~15볼트 사이의 모든 전압에서 작동할 수 있습니다!

전원 공급 장치 전압의 이러한 차이 뒤에 있는 이유는 MOSFET 대 바이폴라 접합 트랜지스터의 각 바이어스 요구 사항 때문입니다. MOSFET은 (기판에 대한) 게이트 전압에 의해 독점적으로 제어되는 반면 BJT는 전류 제어 장치.

TTL 게이트 회로 저항은 5볼트 조정 전원 공급 장치를 가정하여 적절한 바이어스 전류에 대해 정확하게 계산됩니다. 해당 전원 공급 장치 전압의 상당한 변동은 트랜지스터 바이어스 전류가 부정확한 결과를 초래하여 불안정한(예측할 수 없는) 작동을 초래합니다.

전원 공급 장치 전압의 변화가 CMOS 게이트에 미치는 유일한 영향은 "하이"(1) 상태의 전압 정의입니다. 15볼트의 전원 공급 전압에서 작동하는 CMOS 게이트의 경우(Vdd ), 입력 신호는 "높음"(1)으로 간주되기 위해 15볼트에 가까워야 합니다. "낮음"(0) 신호에 대한 전압 임계값은 0볼트에 가깝게 동일하게 유지됩니다.

CMOS의 단점

CMOS의 결정적인 단점 중 하나는 TTL에 비해 속도가 느리다는 것입니다. CMOS 게이트의 입력 커패시턴스는 BJT가 아닌 MOSFET을 사용하기 때문에 비교 가능한 TTL 게이트의 입력 커패시턴스보다 훨씬 크므로 CMOS 게이트는 신호 전환(낮음-높음)에 응답하는 속도가 느립니다. 또는 그 반대) TTL 게이트보다 다른 모든 요소는 동일합니다.

회로 저항과 게이트의 입력 커패시턴스에 의해 형성되는 RC 시정수는 디지털 로직 레벨의 빠른 상승 및 하강 시간을 방해하여 고주파 성능을 저하시키는 경향이 있습니다.

단점을 극복하기 위한 전략

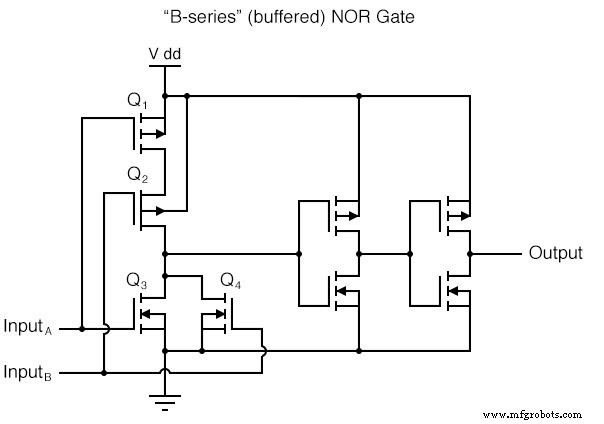

CMOS 게이트 회로의 이러한 고유한 단점을 최소화하기 위한 전략은 추가 트랜지스터 단계로 출력 신호를 "버퍼링"하여 장치의 전체 전압 이득을 높이는 것입니다. 이것은 한 논리 상태에서 다른 논리 상태로 천천히 변하는 입력 전압에 대해 더 빠른 전환 출력 전압(높음에서 낮음 또는 낮음에서 높음)을 제공합니다.

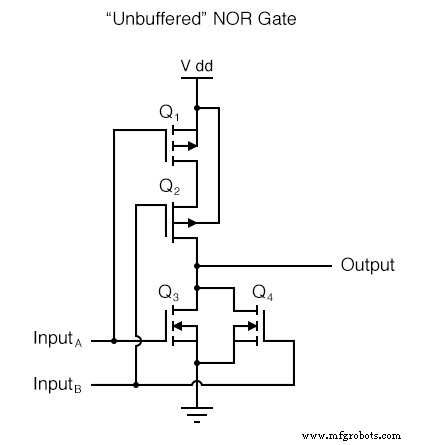

"버퍼링되지 않은" NOR 게이트와 "버퍼링된" 또는 B 시리즈의 이 예를 고려하십시오. , NOR 게이트:

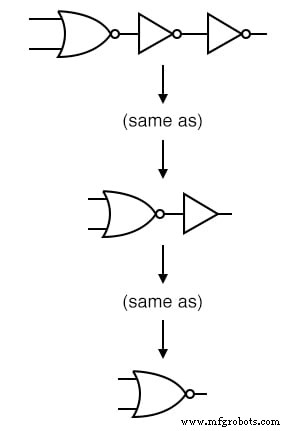

본질적으로 B 시리즈 설계 향상은 간단한 NOR 회로의 출력에 두 개의 인버터를 추가합니다. 두 개의 캐스케이드 인버터가 단순히 취소하기 때문에 이것은 디지털 로직에 관한 한 아무 소용이 없습니다.

그러나 이러한 인버터 단계를 회로에 추가하면 전체 전압 이득을 증가시켜 출력을 입력 상태의 변화에 더 민감하게 만들어 CMOS 게이트 입력 커패시턴스로 인한 고유한 속도 저하를 극복하는 데 도움이 됩니다.

검토:

<울>

관련 워크시트:

<울> <리>절연 게이트 전계 효과 트랜지스터 워크시트

<리>CMOS 논리 게이트 워크시트

산업기술

트랜지스터는 복잡한 전자 부품일 수 있습니다. 그래서 사람들은 종종 트랜지스터를 저항과 혼동하고 혼동합니다. 그러나 트랜지스터는 유형과 용도가 훨씬 다양합니다. 이 가이드에서는 특히 SL100 트랜지스터를 살펴봅니다. 우리는 그것이 다른 트랜지스터와 어떻게 다른지, 그 구조와 언제 가장 잘 사용하는지 다룰 것입니다. SL100 트랜지스터란 무엇입니까? SL100은 저렴한 다목적 바이폴라 접합 NPN(음-양-음) 트랜지스터입니다. 중저전력 트랜지스터입니다. 따라서 초보자 회로 기판 프로젝트에 적합합니다. SL100 트랜지스터

전자 회로는 효과적인 기능을 용이하게 하기 위해 다양한 구성 요소를 통합합니다. 이러한 구성 요소 중에는 광범위한 범위의 트랜지스터가 있습니다. 따라서 다양한 트랜지스터 유형에 대해 자세히 알아보려면 계속 읽으십시오. . 트랜지스터란 트랜지스터는 IC에서 전기 신호를 전환하거나 증폭하는 3층 능동 부품입니다. 또한 능동 구성 요소는 입력 전압이 출력 전압보다 크다는 것을 의미합니다. 트랜지스터는 공간을 덜 차지하고 열 저항이 더 우수하기 때문에 트랜지스터는 진공관을 대체합니다. 그리고 트랜지스터는 더 적은 작동 전력을 사용합