verilog

이전 기사에서는 always을 사용하는 다양한 예를 보여주었습니다. 조합 논리를 구현하는 블록. always 블록은 주로 순차를 구현하는 데 사용됩니다. 값을 저장할 수 있는 플립플롭과 같은 메모리 요소가 있는 논리입니다.

JK 플립 플롭은 값을 저장하는 데 사용되는 여러 유형의 플롭 중 하나이며 2개의 데이터 입력 j 및 k와 함께 리셋 rstn용 및 클록 clk용 하나가 있습니다. JK 플롭에 대한 진리표는 아래와 같으며 일반적으로 NAND 게이트를 사용하여 구현됩니다.

| 첫째 | j | k | q | 댓글 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 리셋이 실행되면 출력은 항상 0입니다. |

| 1 | 0 | 0 | 보유 가치 | j와 k가 모두 0일 때 출력은 이전과 동일하게 유지됩니다. |

| 1 | 0 | 1 | 1 | k=1일 때 출력은 1이 됩니다. |

| 1 | 1 | 0 | 0 | k=0일 때 출력은 0이 됩니다. |

| 1 | 1 | 1 | 토글 값 | j=1,k=1인 경우 출력이 현재 값을 토글합니다. |

JK 플립플롭에 대한 동작 Verilog 코드는 아래와 같이 작성할 수 있습니다.

module jk_ff ( input j, // Input J

input k, // Input K

input rstn, // Active-low async reset

input clk, // Input clk

output reg q); // Output Q

always @ (posedge clk or negedge rstn) begin

if (!rstn) begin

q <= 0;

end else begin

q <= (j & ~q) | (~k & q);

end

end

endmodule

먼저 테스트벤치에서 사용되는 모든 변수를 선언하고 간단한 always을 사용하여 시계를 시작합니다. 설계에 적용할 수 있는 블록입니다. 그런 다음 설계를 인스턴스화하고 해당 포트를 해당 테스트벤치 변수와 연결합니다. q는 wire 유형입니다. 능동적으로 구동할 디자인의 출력에 연결되어 있기 때문입니다. 디자인에 대한 다른 모든 입력은 reg 유형입니다. initial과 같은 절차적 블록 내에서 구동될 수 있도록 .

자극은 먼저 설계에 대한 모든 입력을 0으로 초기화한 다음 일정 시간 후에 재설정을 취소합니다. for 루프는 임의의 시간에 구동되는 j와 k에 다른 값을 구동하는 데 사용됩니다. 루프가 완료되면 잠시 더 기다렸다가 시뮬레이션을 종료합니다.

module tb;

// Declare testbench variables

reg j, k, rstn, clk;

wire q;

integer i;

reg [2:0] dly;

// Start the clock

always #10 clk = ~clk;

// Instantiate the design

jk_ff u0 ( .j(j), .k(k), .clk(clk), .rstn(rstn), .q(q));

// Write the stimulus

initial begin

{j, k, rstn, clk} <= 0;

#10 rstn <= 1;

for (i = 0; i < 10; i = i+1) begin

dly = $random;

#(dly) j <= $random;

#(dly) k <= $random;

end

#20 $finish;

end

endmodule

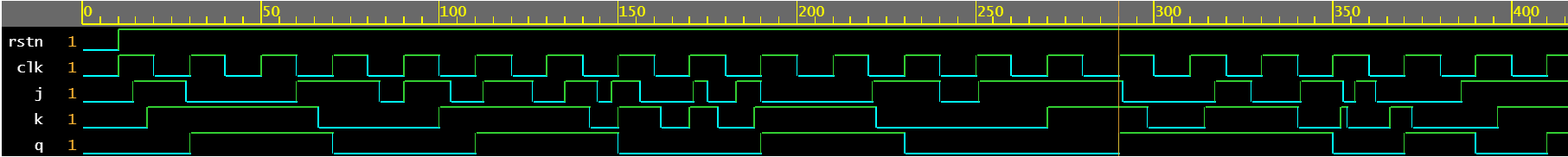

시뮬레이션 파동에서 클럭의 위치에서 출력 q는 진리표에 주어진 것처럼 입력 j와 k의 상태에 따라 값을 변경합니다.

<노스크립트>

Modulus(MOD) 카운터는 단순히 0으로 롤백하기 전에 특정 숫자까지 계산합니다. MOD-N 카운터는 0에서 N-1까지 카운트한 다음 0으로 롤백하고 다시 카운트를 시작합니다. 이러한 카운터는 일반적으로 log2가 필요합니다. 카운트 값을 유지하기 위한 N개의 플롭. 아래는 reset rstn이 선언 해제되는 한 모든 클럭 clk에서 계속 카운트업하는 MOD-10 카운터에 대한 Verilog 코드입니다.

Verilog 매개변수를 사용하여 더 확장 가능한 MOD-N 카운터를 만들 수 있습니다.

module mod10_counter ( input clk,

input rstn,

output reg[3:0] out);

always @ (posedge clk) begin

if (!rstn) begin

out <= 0;

end else begin

if (out == 10)

out <= 0;

else

out <= out + 1;

end

end

endmodule

테스트벤치는 먼저 일부 값을 할당하고 설계 입력에 적용할 수 있는 일부 변수를 선언합니다. 그런 다음 카운터 모듈이 인스턴스화되고 나중에 자극의 일부 값으로 구동되는 테스트벤치 신호와 연결됩니다. 카운터에도 시계가 필요하므로 테스트 벤치 시계는 always으로 모델링됩니다. 차단하다. 자극은 단순히 시간 0ns에서 기본값을 설정하고 10ns 후에 선언 해제를 재설정하고 일정 시간 동안 설계를 실행할 수 있습니다.

module tb;

reg clk, rstn;

reg [3:0] out;

mod10_counter u0 ( .clk(clk), .rstn(rstn), .out(out));

always #10 clk = ~clk;

initial begin

{clk, rstn} <= 0;

#10 rstn <= 1;

#450 $finish;

end

endmodule

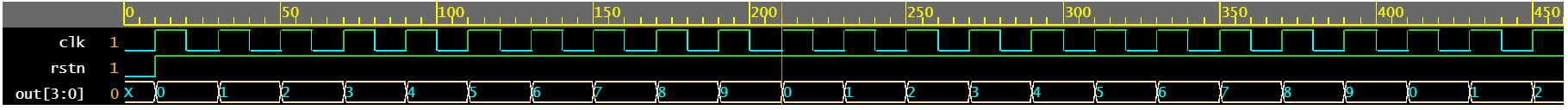

카운터 모듈이 0에서 9까지 카운트하고 0으로 롤오버한 다음 다시 카운트를 시작하는지 확인합니다.

<노스크립트>

아래는 입력 d를 LSB로 받아들이는 4비트 왼쪽 시프트 레지스터이며 다른 모든 비트는 1만큼 왼쪽으로 시프트됩니다. 예를 들어 d가 0이고 레지스터의 초기 값이 0011이면 0110에서 0110이 됩니다. 클럭의 다음 에지.

module lshift_4b_reg ( input d,

input clk,

input rstn,

output reg [3:0] out

);

always @ (posedge clk) begin

if (!rstn) begin

out <= 0;

end else begin

out <= {out[2:0], d};

end

end

endmodule

테스트벤치는 일부 변수가 선언되고 디자인 모듈이 인스턴스화되고 테스트벤치 신호와 연결되는 이전에 표시된 것과 유사한 템플릿을 따릅니다. 그런 다음 시계가 시작되고 initial을 사용하여 자극이 설계에 적용됩니다. 차단하다. 이 테스트벤치 예제에서는 d의 다른 값을 실행해야 하므로 for 루프는 20번 반복하고 디자인에 임의의 값을 적용하는 데 사용됩니다.

module tb;

reg clk, rstn, d;

wire [3:0] out;

integer i;

lshift_4b_reg u0 ( .d(d), .clk(clk), .rstn(rstn), .out(out));

always #10 clk = ~clk;

initial begin

{clk, rstn, d} <= 0;

#10 rstn <= 1;

for (i = 0; i < 20; i=i+1) begin

@(posedge clk) d <= $random;

end

#10 $finish;

end

endmodule

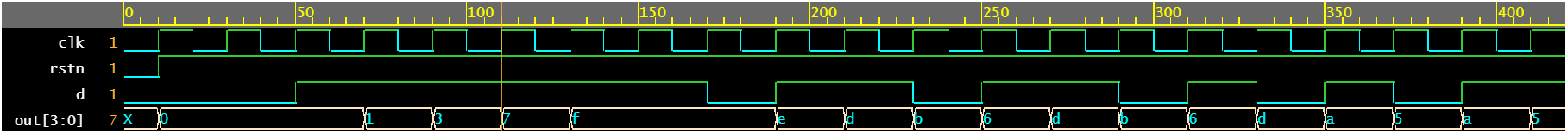

각 비트는 왼쪽으로 1만큼 이동하고 d의 새 값은 LSB에 적용됩니다.

<노스크립트>

verilog

구성품 및 소모품 Arduino UNO × 1 근접 센서 × 1 점퍼 와이어(일반) × 1 이 프로젝트 정보 안녕하세요, 친구들! 오늘은 IR 센서를 Arduino UNO와 인터페이스하는 방법을 보여 드리겠습니다. 시작하겠습니다! 구성 요소 1. 아두이노 우노 2. 적외선 센서 3. LED 4.Arduio 케이블 5.점퍼 와이어 Arduino Uno는 무엇에 사용되나요? Arduino는 사용하기 쉬운 하드웨어 및 소프트웨어를 기

컴퓨터, 통신 장비 및 기타 유사한 유형의 시스템에서 볼 수 있는 것과 같은 디지털 회로를 배우거나 만드는 데 관심이 있습니까? 가장 먼저 살펴볼 것은 트랜지스터 플립플롭입니다. 플립플롭의 기본 빌딩 블록은 논리 게이트이며, 이는 부울 기능을 구현하는 이상적인 전자 모델입니다. 이러한 논리 게이트에는 커패시터 및 저항과 같은 여러 구성 요소가 있을 수 있지만 주로 트랜지스터입니다. 아래에서 다양한 유형의 플립플롭 회로와 해당 배선도에 대해 자세히 설명했습니다. 프로젝트에 사용할 수 있는 방법을 알아보세요. 플립플롭이란 무엇입니까