임베디드

이 기사에서는 다양한 유형의 멀티코어 프로세서와 이러한 장치가 오늘날 일반화되고 인기를 얻고 있는 이유를 포함하여 멀티코어 처리의 다양한 측면에 대해 논의할 것입니다. 그런 다음 칩에 코어가 두 개 이상 있을 때 발생하는 몇 가지 문제와 최신 멀티코어 인식 디버거가 이러한 복잡한 작업을 보다 쉽게 관리할 수 있도록 하는 방법을 살펴보겠습니다.

시스템 성능

똑똑한 컴파일러 알고리즘에서 효율적인 하드웨어 솔루션에 이르기까지 임베디드 컴퓨팅 시스템의 성능을 향상시키는 방법에는 여러 가지가 있습니다. 컴파일러 최적화는 읽고 이해하기 쉬운 고급 언어 코드에서 가장 효율적인 명령어 스케줄링을 얻는 데 중요합니다. 이 외에도 시스템은 프로젝트에서 사용 가능한 병렬 처리를 활용하여 한 번에 둘 이상의 작업을 처리할 수 있습니다. 물론 클럭 주파수를 조정하면 컴퓨팅 시스템에서 더 많은 성능을 얻을 수 있는 효과적인 방법이 될 수 있습니다.

불행히도 클럭 속도가 기하학적으로 증가한다고 가정할 수 있었던 시대는 지났습니다. 그리고 코드 최적화는 특히 여러 세대에 걸친 컴파일러 기술 개발을 거친 후에야 훨씬 더 많은 개선을 얻을 수 있습니다. 따라서 시간이 지남에 따라 시스템 성능을 계속 확장할 수 있는 가장 좋은 기회로 병렬 처리를 고려할 수 있습니다.

병렬화

우물을 파는 것은 병렬화하기 어려운 작업입니다. 다른 사람들이 삽으로 흙을 치우는 것을 도울 수 있지만 실제로 구덩이를 파는 것은 일반적으로 한 사람의 작업입니다. 결과적으로 구멍에 더 많은 사람을 추가해도 작업이 더 빨리 완료되지 않습니다. 사실, 다른 사람들은 방해가 되어 프로세스를 늦출 수 있습니다. 일부 작업은 병렬화에 적합하지 않습니다.

다른 작업은 쉽게 병렬화됩니다. 도랑을 파는 것은 병렬화에 적합한 작업입니다. 많은 사람들이 서로 협력할 수 있습니다.

이 그림은 MIMD(Multiple Instruction Multiple Data)라고 하는 병렬 처리의 한 형태를 보여줍니다. 각 굴착기는 별도의 단위이며 다른 작업을 수행할 수 있습니다. 이 경우 네 명의 굴착기가 작업을 약 1/4 만에 완료할 수 있다고 상상할 수 있습니다. 광부 한 사람의 시간입니다.

SIMD(Single Instruction Multiple Data)를 사용하면 단일 굴착기가 이와 같은 삽을 사용할 수 있습니다.

SIMD 장치는 한 번에 한 가지 유형의 계산만 수행할 수 있지만 여러 데이터 조각에 대해 병렬로 수행할 수 있습니다. 이러한 유형의 명령어는 많은 프로세서의 벡터 처리 장치에서 일반적입니다. 이는 데이터가 매우 규칙적이고 이미지 처리와 같이 대규모 데이터 세트에 대해 동일한 작업을 반복해서 수행해야 하는 경우에 유용합니다. 그러나 보다 일반적인 컴퓨팅 작업의 경우 이 모델은 유연성이 부족하고 성능이 향상되지 않습니다.

따라서 단일 칩에 여러 개의 전체 CPU 하위 시스템을 배치하여 다중 코어 프로세서를 생성하는 선택을 하게 됩니다. 하나의 칩에 여러 코어가 있으면 성능을 확장할 수 있습니다. 각 코어는 전체 CPU이며 독립적으로 또는 다른 코어와 함께 작동할 수 있습니다.

다양한 유형의 멀티코어 처리

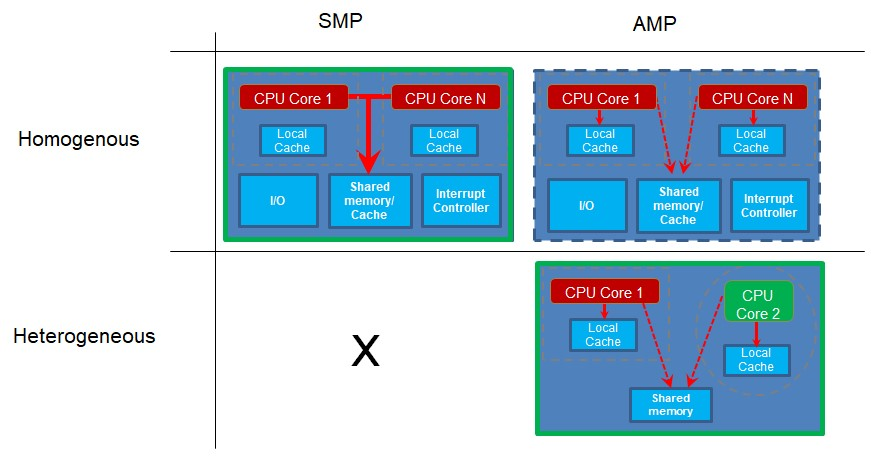

프로세서 칩에 있을 수 있는 코어 유형과 코어 간에 작업이 분산되는 방식의 다양한 조합이 있습니다.

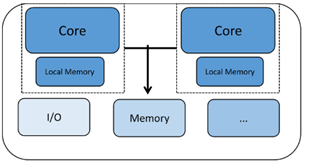

동종 멀티코어 프로세서에는 동일한 프로세서 코어의 사본이 두 개 이상 있습니다. 각 코어는 자율적으로 실행되며 공유 메모리 또는 메일박스 시스템과 같은 여러 메커니즘을 통해 다른 코어와 통신하고 동기화할 수 있습니다. 각 프로세서에는 고유한 레지스터와 기능 단위가 있으며 고유한 로컬 메모리 또는 캐시가 있을 수 있습니다. 그러나 이것을 동질적으로 만드는 것은 우리가 보고 있는 모든 코어가 동일한 유형이라는 사실입니다.

다른 유형의 다중 코어 칩은 2개 이상의 서로 다른 종류의 CPU 코어가 있는 이기종 다중 코어라고 합니다. 여기에서 코어는 시스템 처리 요구 사항의 다른 부분에 매우 적합한 매우 다른 특성을 가질 수 있습니다. 한 가지 예는 한 코어가 Bluetooth 프로토콜 스택 관리 전용인 Bluetooth 통신 칩일 수 있으며 다른 코어는 외부 통신, 애플리케이션 처리, 휴먼 인터페이스 등을 관리할 수 있습니다. 이러한 종류의 다중 코어 칩은 두 가지가 모두 필요한 애플리케이션에 사용할 수 있습니다. 한 코어에서는 실시간 전용 성능을 제공하고 다른 코어에서는 시스템 관리 기능을 제공합니다.

이제 코어가 어떻게 사용되는지 살펴보겠습니다. SMP(대칭 다중 처리)는 둘 이상의 코어가 있고 코어가 동일한 프로젝트 코드 기반을 실행할 때 발생합니다. 다른 코어에서 동시에 코드의 다른 부분을 실행할 수 있지만 코드는 단일 프로젝트로 빌드되고 실시간 운영 체제(RTOS)와 같은 일부 제어 프로그램에 의해 별도의 코어로 디스패치됩니다. 한 가지 유형의 프로세서에 대해 컴파일된 동일한 프로젝트 코드를 모두 사용하기 때문에 이러한 방식으로 작동하는 코어는 필연적으로 동일한 유형이어야 합니다.

AMP(Asymmetric multiprocessing)는 두 개 이상의 코어 또는 프로세서가 있고 각 프로세서가 자체 프로젝트 애플리케이션을 실행할 때 발생합니다. 별도의 코어는 때때로 동기화하거나 통신할 수 있지만 각각 실행되는 자체 코드 기반이 있습니다. 그들은 각각 자신의 프로젝트를 실행하고 있기 때문에 이러한 코어는 다른 유형이거나 이기종 코어일 수 있습니다. 그러나 이것은 요구 사항이 아닙니다. 두 개 이상의 동일한 유형의 코어가 다른 프로젝트 코드를 실행하는 경우 AMP를 실행하는 동종 코어입니다.

SMP 작업의 경우 모두 동일한 단일 프로젝트 코드 기반에서 코드를 실행하기 때문에 여러 개의 동종 코어가 있어야 합니다. 그러나 실행할 서로 다른 코어에 대해 서로 다른 코드 기반을 가진 여러 프로젝트가 있는 경우 이기종 시스템과 같이 서로 다른 코어가 될 수 있습니다. 그러나 코어가 동일하면 작동합니다.

멀티코어를 사용하는 이유

지난 몇 년 동안 1960년대 중반에 만들어진 무어의 법칙은 마침내 기력이 바닥나거나 적어도 느려지는 것 같습니다. 프로세서 클럭 속도는 더 이상 2-3년마다 두 배로 증가하지 않으며 실제로 최고 속도의 CPU는 수년 동안 낮은 한 자리 GHz 범위에서 한계에 도달했습니다.

성능 한계를 계속해서 끌어올리는 한 가지 방법은 효율적으로 사용할 수 있는 경우 더 많은 CPU 코어가 함께 작동하도록 하는 것입니다.

속도가 정체되는 동안 트랜지스터 크기는 계속 축소되었습니다. 과거보다 속도는 느리지만 소형 트랜지스터는 단일 칩에 더 많은 로직을 담을 수 있습니다. 결과적으로 이러한 트랜지스터를 사용하여 단일 칩에 여러 CPU 코어를 배치하면 여러 CPU와 메모리 하위 시스템 간의 훨씬 빠르고 넓은 버스 상호 연결을 활용할 수 있습니다.

이기종 비대칭 멀티프로세싱은 애플리케이션에 특성과 요구 사항이 매우 다른 두 개 이상의 워크로드가 있는 경우 매우 유용합니다. 하나는 실시간 및 인터럽트 대기 시간에 종속될 수 있는 반면 다른 하나는 응답 시간보다 처리량에 더 많이 종속될 수 있습니다. 이 모델은 매우 잘 작동합니다. 예를 들어, 장치는 하나의 코어를 Bluetooth 또는 Zigbee와 같은 통신 프로토콜 스택을 관리하는 데 사용하고 다른 코어는 인간 상호 작용 및 전체 시스템 관리 작업을 실행하는 애플리케이션 프로세서 역할을 합니다. 분리된 통신 프로세서는 프로토콜 스택에 필요한 우수한 실시간 응답을 제공할 수 있습니다. 또한 통신 소프트웨어는 시스템의 이 부분과 기능 수정을 분리하여 전체 제품을 쉽게 인증할 수 있는 표준으로 인증할 수 있습니다.

멀티코어를 사용한 과제

칩에 둘 이상의 CPU 코어를 넣을 때 어떤 종류의 문제가 발생합니까? 자, 파헤쳐 보겠습니다.

모놀리식 응용 프로그램이나 소프트웨어는 사용 가능한 컴퓨팅 리소스를 효율적으로 사용하지 못할 수 있습니다. 둘 이상의 코어 리소스를 사용하기 위해 동시에 실행할 수 있는 병렬 작업으로 애플리케이션을 구성해야 합니다. 이것은 소프트웨어 엔지니어가 임베디드 디자인을 생각하는 데 익숙하지 않은 방식을 요구할 수 있습니다. 기존 단일 루프 코드를 마이그레이션하는 것은 그리 쉽지 않을 수 있습니다. 스레드가 너무 적거나 너무 많으면 성능 장벽이 될 수 있습니다.

여러 스레드 또는 프로세스 간에 데이터 구조 또는 I/O 장치를 공유하는 응용 프로그램에는 직렬 병목 현상이 있을 수 있습니다. 데이터 무결성을 유지하려면 읽기 잠금, 읽기-쓰기 잠금, 쓰기 잠금, 스핀 잠금, 뮤텍스 등과 같은 잠금 기술을 사용하여 이러한 공유 리소스에 대한 액세스를 직렬화해야 할 수 있습니다. 비효율적으로 설계된 잠금은 공유 리소스를 사용하기 위해 잠금을 획득하려는 여러 스레드 또는 프로세스 간의 높은 잠금 경합으로 인해 병목 현상을 일으킬 수 있습니다. 이는 잠재적으로 응용 프로그램 또는 소프트웨어의 성능을 저하시킬 수 있습니다. 일부 코어가 일반 잠금을 기다리는 다른 코어를 지연시켜 2개의 코어가 1개보다 성능을 저하시키는 경우 코어 또는 프로세서 수가 증가함에 따라 애플리케이션 성능이 저하될 수도 있습니다.

불균등하게 분산된 워크로드는 컴퓨팅 리소스를 활용하는 데 비효율적일 수 있습니다. 큰 작업을 병렬로 실행할 수 있는 작은 작업으로 나누어야 할 수도 있습니다. 성능과 확장성을 향상시키기 위해 직렬 알고리즘을 병렬 알고리즘으로 변경해야 할 수도 있습니다. 그러나 일부 작업은 매우 빠르게 실행되고 다른 작업은 상당한 시간이 소요되는 경우 빠른 작업은 긴 작업이 완료될 때까지 기다리는 데 상당한 시간을 할애할 수 있습니다. 그 결과 귀중한 컴퓨팅 리소스가 유휴 상태가 되고 성능 조정이 저하됩니다.

RTOS가 도움이 될 수 있지만 모든 것을 해결하지는 못할 수도 있습니다. SMP 시스템에서 이는 여러 유사한 코어에 대한 작업을 예약하기 위해 사실상 필수입니다. 수행할 작업은 데이터 또는 기능별로 나눌 수 있습니다. 데이터 청크로 사물을 나누면 각 스레드가 처리 파이프라인의 모든 단계를 수행할 수 있습니다. 또는 한 스레드가 함수의 한 단계를 수행하고 다른 스레드가 다음 단계를 수행하는 등의 작업을 수행할 수 있습니다. 한 기술의 장점은 수행할 작업의 특성에 따라 다릅니다.

멀티코어 환경에서 디버깅

멀티코어 시스템을 디버깅할 때 가장 먼저 유용한 것은 모든 코어의 가시성입니다. 이상적으로는 코어를 동시에 또는 개별적으로 시작 및 중지할 수 있어야 합니다. 멀티코어 중단점은 다른 코어의 상태를 전제로 한 코어의 작동을 제어하는 데 매우 유용할 수 있습니다.

멀티코어 추적은 구현하기가 매우 어려울 수 있습니다. 여러 코어에서 높은 대역폭의 추적 정보를 관리하고 다른 종류의 코어에서 잠재적으로 다른 유형의 추적 데이터를 처리하는 것은 정말 어려운 일입니다.

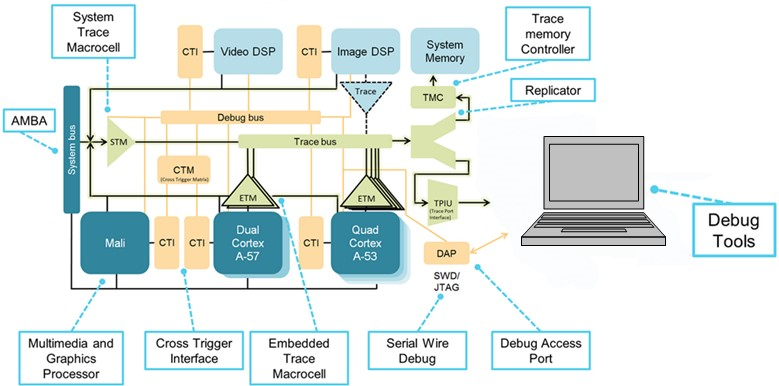

(출처:IAR Systems, 다이어그램 제공:Arm Ltd.)

다음은 이기종 및 동종 멀티코어 구현을 모두 포함하는 프로세서의 예입니다. 두 개의 동종 코어 그룹이 있습니다. 하나는 이중 Arm Cortex-A57을 기반으로 하고 다른 하나는 쿼드 Cortex-A53을 기반으로 합니다. 이러한 그룹은 내부적으로는 동질적이지만 두 그룹 간에는 이질적입니다.

CoreSight 디버그 아키텍처는 모든 코어의 디버그 리소스와 통신하기 위한 프로토콜 및 메커니즘을 제공하며 디버거가 이 모든 정보를 관리하고 다른 코어의 메시지를 구문 분석합니다. 교차 트리거 인터페이스 및 매트릭스(CTI, CTM)는 두 코어의 동시 정지, 추적 트리거 등을 허용합니다. 추적 인프라에는 추적 흐름을 원활하게 하는 데 사용되는 직렬(SWD) 및 병렬(TPIU) 추적 포트와 각 소스의 추적을 단일 흐름으로 결합하는 추적 깔때기가 포함됩니다. 듀얼 코어 부품과 비교하여 표시된 다이어그램은 제어해야 하는 훨씬 더 복잡한 칩을 나타냅니다.

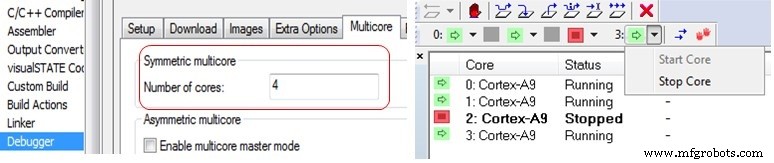

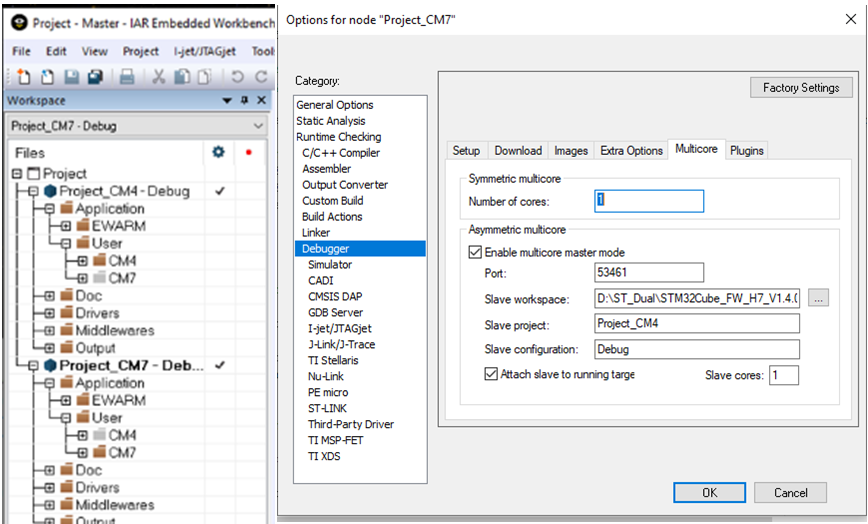

IAR Embedded Workbench의 C-SPY 디버거는 대칭 및 비대칭 멀티코어 디버깅을 모두 지원합니다. 이것은 멀티코어 탭의 디버거 옵션을 통해 활성화됩니다. 대칭형 멀티코어 디버그를 활성화하려면 디버거가 통신할 서로 다른 프로세서의 수를 알 수 있도록 코어 수를 입력하기만 하면 됩니다. 다른 IDE에서도 유사한 옵션을 사용할 수 있습니다.

오른쪽(위)에서 4코어 Cortex-A9 SMP 클러스터가 다른 3개 코어가 실행되는 동안 코어 번호 2가 중지된 상태로 코어 상태가 표시되는 디버거 보기를 볼 수 있습니다.

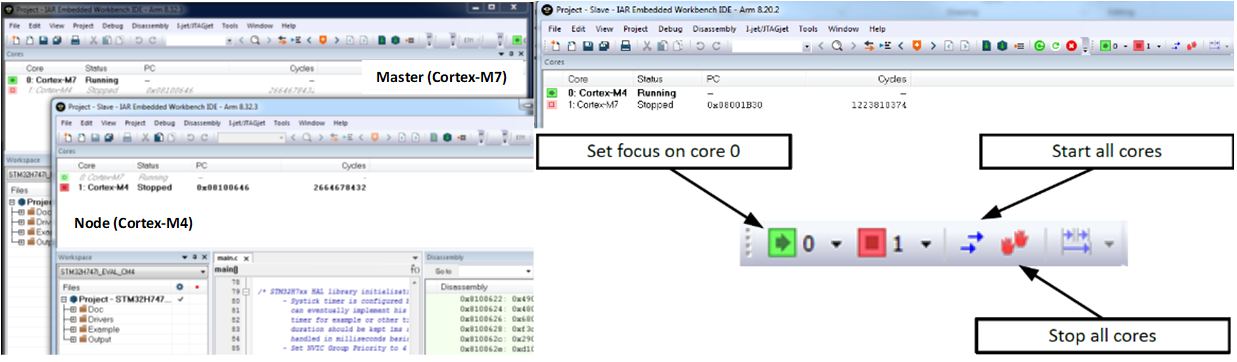

비대칭 멀티코어 시스템은 하나의 Cortex-M7 코어와 별도의 Cortex-M4가 있는 ST STM32H745/755와 같은 이기종 멀티코어 부품을 사용할 수 있습니다. 이 경우 디버거가 실행될 때 IDE의 두 인스턴스(마스터 및 노드)를 사용합니다. 두 코어에서 서로 다른 프로젝트 코드를 실행하고 있으므로 각 코어당 하나씩.

IDE의 각 인스턴스에는 제어 중인 코어와 다른 창에서 제어되는 다른 코어에 대한 상태 정보가 있습니다. 코어를 함께 또는 별도로 시작 및 중지하는 것이 개발자의 제어 하에 있도록 디버거의 동작을 제어하도록 선택할 수 있는 옵션이 있습니다.

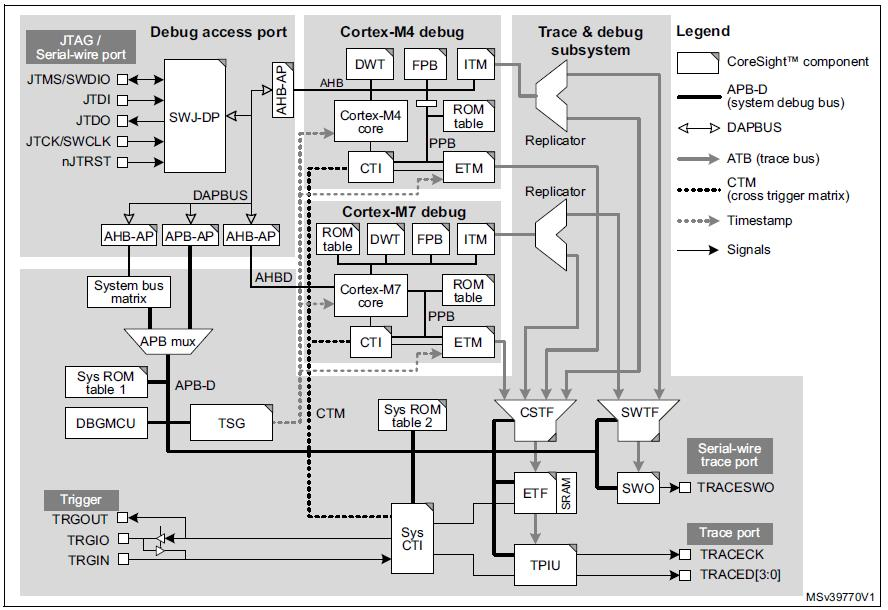

이 완전한 제어는 교차 트리거 인터페이스(CTI)와 교차 트리거 매트릭스(CTM)가 함께 Arm 내장 교차 트리거 기능을 형성하기 때문에 가능합니다. 세 가지 CTI 구성 요소가 있습니다. 하나는 시스템 수준, 하나는 Cortex-M7 전용, 다른 하나는 Cortex-M4 전용입니다. 세 개의 CTI는 아래 그림과 같이 CTM을 통해 서로 연결됩니다. 시스템 수준 및 Cortex-M4 CTI는 시스템 액세스 포트 및 관련 APB-D를 통해 디버거에서 액세스할 수 있습니다. Cortex-M7 CTI는 물리적으로 Cortex-M7 코어에 통합되어 있으며 Cortex-M7 액세스 포트를 통해 액세스할 수 있습니다.

(출처:IAR Systems, M0399 참조 설명서의 STMicroelectronics 다이어그램 제공)

CTI를 사용하면 다양한 소스의 이벤트가 디버그 및 추적 활동을 트리거할 수 있습니다. 예를 들어, 프로세서 코어 중 하나에서 중단점에 도달하면 다른 프로세서를 중지하거나 외부 트리거 입력에서 감지된 전환이 코드 추적을 시작하도록 설정할 수 있습니다.

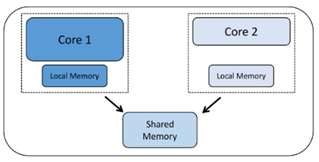

단일 칩에 Cortex-M7 코어와 Cortex-M4 코어가 있는 이기종 멀티코어 프로세서가 있는 이 예에서는 두 개의 개별 프로그램이 사용됩니다. 하나는 Cortex-M4에서 실행되고 다른 하나는 Cortex-M7에서 실행됩니다. 각 프로젝트는 FreeRTOS를 사용하여 프로세서에서 실행되는 소프트웨어를 관리합니다. 두 코어는 공유 메모리 인터페이스를 통해 통신합니다. 그러나 응용 프로그램은 모두 FreeRTOS 메시지 전달 메커니즘을 사용하여 다른 프로세서와 통신하고 기본 메커니즘의 복잡성을 숨깁니다. 따라서 한 CPU의 관점에서는 다른 작업과 함께 메시지를 보내거나 받는 것뿐입니다. 다른 작업이 다른 CPU 코어에서 실행되고 있다는 것은 투명합니다.

아래 이미지는 IDE의 Workspace Explorer 창입니다. Cortex-M7 및 Cortex-M4 프로젝트의 내용을 모두 볼 수 있도록 두 프로젝트의 개요가 여기에 표시됩니다.

창 하단에 있는 다른 탭 중 하나를 선택하여 M4 프로젝트 또는 M7 프로젝트로 포커스를 전환할 수 있습니다.

Cortex-M7 프로젝트에는 Cortex-M4에서 실행 중인 작업에 메시지를 보내는 작업이 있습니다. Cortex-M4에는 실행 중인 수신 작업의 두 인스턴스가 있습니다. Cortex-M7에는 주기적으로 실행되는 "확인" 작업이 있어 작업이 여전히 올바르게 실행되고 있는지 확인합니다.

마지막으로 디버거는 두 프로젝트를 모두 로드합니다. 이는 두 번째 디버거용 Embedded Workbench의 추가 인스턴스가 시작되었음을 의미합니다.

비대칭 멀티프로세싱 지원을 위해 디버거를 설정하려면 한 프로젝트를 "마스터"로 지정하고 다른 프로젝트를 "노드" 프로젝트로 지정해야 합니다. 사실 선택은 임의적이며 시작할 때 다른 프로젝트를 시작할 수 있는 기능이 있는 프로젝트만 결정합니다.

"노드" 프로젝트에는 특별한 설정이 없으며 다른 프로젝트에 대해 "노드"로 실행되고 있음을 인식하지 못합니다.

이런 식으로 "마스터" 프로젝트에서 디버거가 시작되면 두 번째 프로젝트가 실행될 두 번째 디버거 세션을 수용하기 위해 IDE의 다른 인스턴스를 자동으로 시작합니다.

요약

멀티코어는 무어의 법칙이 끝날 때 성능 향상을 가능하게 합니다. 그러나 멀티코어는 디버깅 문제를 제시하고 애플리케이션이 멀티코어 아키텍처를 최대한 활용할 수 있도록 특정 개발 접근 방식이 필요합니다.

디버그 설정이 구성되면 멀티코어 디버깅이 그 어느 때보다 쉬워졌습니다. 이전에 모노 코어 디버깅을 위한 도구를 사용한 적이 있다면 여기에 포함된 모든 것을 인식할 것이며 다른 사람들이 멀티코어 디버깅이 얼마나 어려운지 이야기하는 것을 결코 이해하지 못할 것입니다.

최신 하드웨어 및 소프트웨어 도구는 멀티코어 디버깅 문제를 극복하는 데 도움이 됩니다.

참고:그림 이미지는 달리 명시되지 않는 한 IAR Systems에서 제공한 것입니다.

아론 바우치 IAR Systems의 선임 필드 애플리케이션 엔지니어로 미국 동부 및 캐나다의 고객과 협력하고 있습니다. Aaron은 Intel, Analog Devices 및 Digital Equipment Corporation을 포함한 회사의 임베디드 시스템 및 소프트웨어와 함께 일했습니다. 그의 디자인은 의료 기기, 내비게이션 및 은행 시스템을 포함한 광범위한 응용 분야를 다루고 있습니다. Aaron은 또한 Southern NH University의 교수로 Embedded System Design을 비롯한 여러 대학 수준의 과정을 가르쳤습니다. Bauch씨는 뉴욕주 뉴욕에 있는 Cooper Union에서 전기 공학 학사 학위를, Columbia University에서 전기 공학 석사 학위를 취득했습니다.

아론 바우치 IAR Systems의 선임 필드 애플리케이션 엔지니어로 미국 동부 및 캐나다의 고객과 협력하고 있습니다. Aaron은 Intel, Analog Devices 및 Digital Equipment Corporation을 포함한 회사의 임베디드 시스템 및 소프트웨어와 함께 일했습니다. 그의 디자인은 의료 기기, 내비게이션 및 은행 시스템을 포함한 광범위한 응용 분야를 다루고 있습니다. Aaron은 또한 Southern NH University의 교수로 Embedded System Design을 비롯한 여러 대학 수준의 과정을 가르쳤습니다. Bauch씨는 뉴욕주 뉴욕에 있는 Cooper Union에서 전기 공학 학사 학위를, Columbia University에서 전기 공학 석사 학위를 취득했습니다. 관련 콘텐츠:

더 많은 Embedded를 보려면 Embedded의 주간 이메일 뉴스레터를 구독하세요.

임베디드

지속 가능성은 제조업의 미래를 여는 열쇠입니다. 소비자와 기업이 모두 제품의 탄소 발자국을 고려함에 따라 혁신적인 제조업체는 제조 과정에서 생성되는 배출량을 추적, 평가 및 줄이는 새로운 방법을 모색하고 있습니다. 공동 창립자이자 CEO인 Lou Rassey로부터 보다 지속 가능한 제조를 위한 Fast Radius의 노력에 대해 자세히 알아보세요. 대본: 기업이 지속 가능성에 대해 이야기하는 것을 들을 때, 때로는 그것이 몇 년 또는 수십 년이 지난 것처럼 느껴질 수 있습니다. 기업이 더 지속 가능하게 만들고 움직이기를 원한다면

오늘날의 비즈니스가 디지털 시대에 성장함에 따라 자동화는 점점 더 많은 산업에 영향을 미치고 있습니다. 이러한 산업에는 제조 및 용접이 포함됩니다. 많은 사람들이 로봇으로 대체되는 일자리에 대해 걱정하고 있습니다. 인공 지능의 급속한 발전은 트럭 운전사, 고객 서비스 담당자 및 자동차 작업자가 자신의 직업을 위험에 빠뜨릴 것이라는 두려움을 불러일으킵니다. 로봇이 인간보다 더 효율적으로 반복적인 작업을 수행할 수 있기 때문에 가치 있는 일을 맡게 될까요? 대답은 단순한 예 또는 아니오보다 더 복잡합니다. 다음은 로봇 공학이 직업에 영