산업기술

다음 회로는 SPICE 2g6용으로 사전 테스트된 넷리스트이며 필요한 경우 간단한 설명과 함께 완료됩니다. (SPICE의 네트리스트에 대한 자세한 내용은 2장의 전기 회로의 컴퓨터 시뮬레이션을 참조하십시오.)

분석 및/또는 수정을 위해 넷리스트를 자신의 SPICE 소스 파일에 자유롭게 "복사" 및 "붙여넣기"하십시오. 여기에서 제 목표는 두 가지입니다. SPICE 넷리스트 구문에 대한 더 깊은 이해를 위해 SPICE 넷리스트 설계의 실제 예를 제공하고 간단한 회로를 분석할 때 SPICE 넷리스트가 얼마나 간단하고 컴팩트할 수 있는지 보여 주는 것입니다.

이 예에 대한 모든 출력 목록은 관련 없는 정보를 "잘라냄"으로 SPICE 출력을 가능한 한 가장 간결하게 표시합니다. 저는 주로 이 문서의 공간을 절약하기 위해 이 작업을 수행합니다.

일반적인 SPICE 출력에는 당면한 작업과 반드시 관련이 있는 것은 아닌 많은 헤더와 요약 정보가 포함됩니다. 따라서 직접 시뮬레이션을 실행하고 결과가 정확하게 아닌 것을 발견하더라도 놀라지 마십시오. 내가 여기에 표시한 것과 같습니다!

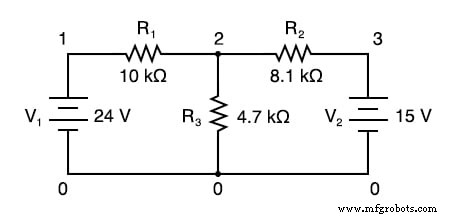

.dc 없이 카드 및 .print 또는 .plot 카드에서 이 넷리스트의 출력은 노드 1, 2, 3의 전압만 표시합니다(물론 노드 0 참조).

넷리스트:

다중 dc 소스 v1 1 0 dc 24 v2 3 0 dc 15 r1 1 2 10k r2 2 3 8.1k r3 2 0 4.7k .end

출력:

노드 전압 노드 전압 노드 전압 ( 1) 24.0000 ( 2) 9.7470 ( 3) 15.0000

전압 소스 전류 이름 전류 v1 -1.425E-03 v2 -6.485E-04

총 전력 손실 4.39E-02와트

.dc 추가 분석 카드 및 소스 V1 지정 24볼트에서 24볼트로 1단계로(즉, 24볼트 안정), .print를 사용할 수 있습니다. 원하는 두 지점 사이의 전압을 출력하는 카드 분석.

이상하게도 .dc 분석 옵션이 호출되면 각 노드(접지)에 대한 기본 전압 출력이 사라지므로 결국 .print에서 명시적으로 지정해야 합니다. 카드를 모두 볼 수 있습니다.

넷리스트:

다중 dc 소스 v1 1 0 v2 3 0 15 r1 1 2 10k r2 2 3 8.1k r3 2 0 4.7k .dc v1 24 24 1 .print dc v(1) v(2) v(3) v( 1,2) v(2,3) .end

출력:

<이전>v1 v(1) v(2) v(3) v(1,2) v(2,3) 2.400E+01 2.400E+01 9.747E+00 1.500E+01 1.425E+01 -5.253 E+00

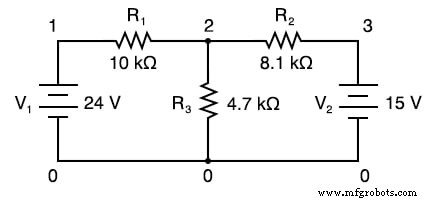

DC 분석의 경우 모든 무효 부품(C 또는 L)의 초기 조건을 지정해야 합니다(커패시터의 경우 전압, 인덕터의 경우 전류). 이것은 각 커패시터 카드의 마지막 데이터 필드에 의해 제공됩니다(ic=0 ).

DC 분석을 수행하려면 .tran ("일시적 ") 분석 옵션을 지정해야 하며 첫 번째 데이터 필드는 시간 증분을 초 단위로 지정하고 두 번째 데이터 필드는 총 분석 시간(초)을 지정하며 "uic "는 분석 시 "초기 조건을 사용"하도록 지시합니다.

넷리스트:

RC 시간 지연 회로 v1 1 0 dc 10 c1 1 2 47u ic=0 c2 1 2 22u ic=0 r1 2 0 3.3k .tran .05 1 uic .print tran v(1,2) .end출력:

<전>시간 v(1,2) 0.000E+00 7.701E-06 5.000E-02 1.967E+00 1.000E-01 3.551E+00 1.500E-01 4.824E+00 2.050E 2.500E-01 6.664E+00 3.000E-01 7.322E+00 3.500E-01 7.851E+00 4.000E-01 8.274E+00 4.500E+01 8.615E -01 9.107E+00 6.000E-01 9.283E+00 6.500E-01 9.425E+00 7.000E-01 9.538E+00 7.500E-01 9.629E+00 802E 9.761E+00 9.000E-01 9.808E+00 9.500E-01 9.846E+00 1.000E+00 9.877E+00

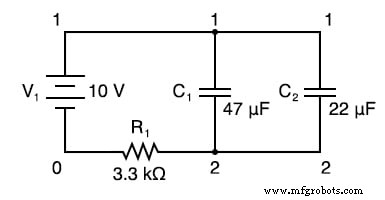

이 연습은 .plot를 사용하여 사인파 전압 소스의 순시 값을 플로팅하기 위한 적절한 설정을 보여줍니다. 기능(일시적인 분석). 당연히 이 데크의 푸리에 분석에는 .tran도 필요합니다. (일시적인) 분석 옵션은 적절한 시간 범위에 대해 지정되어야 합니다.

이 특정 데크의 시간 범위는 정확도가 다소 떨어지는 푸리에 분석을 허용합니다. 과도 해석을 수행하는 기본 주파수의 주기가 많을수록 푸리에 해석이 더 정확해집니다. 이것은 SPICE의 특징이 아니라 파형의 기본 원리입니다.

넷리스트:

v1 1 0 sin(0 15 60 0 0) rload 1 0 10k * 더 나은 푸리에 정밀도를 위해 tran 카드를 다음으로 변경 * .tran 1m 30m .01m 및 .options 카드 포함:* .options itl5=30000 .tran 1m 30m .plot tran v(1) .four 60 v(1) .end

출력:

<사전>시간 v(1) -2.000E+01 -1.000E+01 0.000E+00 1.000E+01 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 0.000E+00 . . * . . 1.000E-03 5.487E+00 . . . * . . 2.000E-03 1.025E+01 . . . * . 3.000E-03 1.350E+01 . . . . * . 4.000E-03 1.488E+01 . . . . *. 5.000E-03 1.425E+01 . . . . * . 6.000E-03 1.150E+01 . . . . * . 7.000E-03 7.184E+00 . . . * . . 8.000E-03 1.879E+00 . . . * . . 9.000E-03 -3.714E+00 . . * . . . 1.000E-02 -8.762E+00 . . * . . . 1.100E-02 -1.265E+01 . * . . . . 1.200E-02 -1.466E+01 . * . . . . 1.300E-02 -1.465E+01 . * . . . . 1.400E-02 -1.265E+01 . * . . . . 1.500E-02 -8.769E+00 . . * . . . 1.600E-02 -3.709E+00 . . * . . . 1.700E-02 1.876E+00 . . . * . . 1.800E-02 7.191E+00 . . . * . . 1.900E-02 1.149E+01 . . . . * . 2.000E-02 1.425E+01 . . . . * . 2.100E-02 1.489E+01 . . . . *. 2.200E-02 1.349E+01 . . . . * . 2.300E-02 1.026E+01 . . . * . 2.400E-02 5.491E+00 . . . * . . 2.500E-02 1.553E-03 . . * . . 2.600E-02 -5.514E+00 . . * . . . 2.700E-02 -1.022E+01 . * . . . 2.800E-02 -1.349E+01 . * . . . . 2.900E-02 -1.495E+01 . * . . . . 3.000E-02 -1.427E+01 . * . . . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -과도 응답의 푸리에 성분 v(1) dc 성분 =-1.885E-03 고조파 주파수 푸리에 정규화 위상 정규화 없음(hz) 성분 성분(deg) 위상(deg) 1 6.000E+01 1.494E+01 1.000000 - 71.998 0.000 2 1.200E + 02 1.886E-02 -50.162 0.001262 21.836 3 1.800E + 02 1.346E-03 0.000090 102.674 174.671 4 2.400E + 02 1.799E-02 -10.866 0.001204 61.132 5 3.000E + 02 3.604E-03 0.000241 160.923 232.921 6 3.600E + 02 5.642E-03 0.000378 7 -176.247 -104.250 4.200E + 02 2.095E-03 0.000140 122.661 194.658 8 4.800E + 02 4.574E-03 -143.754 -71.757 0.000306 9 5.400E + 02 4.896E- 03 0.000328 -129.418 -57.420 총 고조파 왜곡 =0.186350%

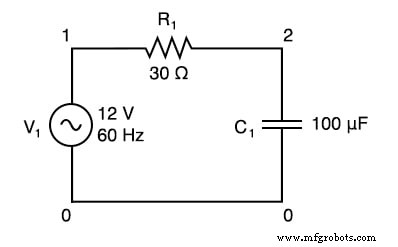

.ac 카드는 단일 지점에서 60Hz에서 60Hz까지 ac 분석 지점을 지정합니다. 물론 이 카드는 주파수 범위를 단계적으로 분석할 수 있는 다중 주파수 분석에 조금 더 유용합니다. .print 카드는 노드 1과 2 사이의 AC 전압을 출력하고 노드 2와 접지 사이의 AC 전압을 출력합니다.

넷리스트:

간단한 AC 회로 데모 v1 1 0 ac 12 sin r1 1 2 30 c1 2 0 100u .ac lin 1 60 60 .print ac v(1,2) v(2) .end

출력:

주파수 v(1,2) v(2) 6.000E+01 8.990E+00 7.949E+00

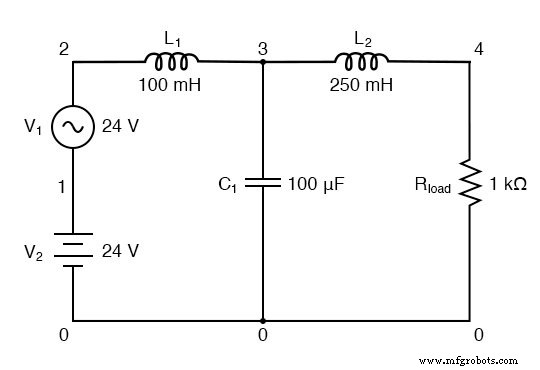

이 저역 통과 필터는 AC를 차단하고 DC를 Rload로 전달합니다. 저항기. 정류기 회로의 리플을 억제하는 데 사용되는 일반적인 필터로, 실제로는 공진 주파수가 있어 기술적으로 대역 통과 필터가 됩니다.

그러나 어쨌든 DC를 통과시키고 AC-DC 정류 프로세스에 의해 생성된 고주파 고조파를 차단하는 것은 잘 작동합니다. 성능은 500Hz ~ 15kHz 범위의 AC 소스로 측정됩니다. 원하는 경우 .print 카드는 .plot으로 대체되거나 보완될 수 있습니다. 노드 4의 AC 전압을 그래픽으로 표시하는 카드.

넷리스트:

저역통과 필터 v1 2 1 ac 24 sin v2 1 0 dc 24 rload 4 0 1k l1 2 3 100m l2 3 4 250m c1 3 0 100u .ac lin 30 500 15k(4)ac vplot 4) .end

주파수 v(4) 5.000E+02 1.935E-01 1.000E+03 3.275E-02 1.500E+03 1.057E-02 2.000E+03 4.614E-03 2.500E+ +03 1.403E-03 3.500E+03 8.884E-04 4.000E+03 5.973E-04 4.500E+03 4.206E-04 5.000E+03 3.072E-04+5.5 1.782E-04 6.500E+03 1.403E-04 7.000E+03 1.124E-04 7.500E+03 9.141E-05 8.000E+03 7.536E-05 8.560.2 -05 9.500E+03 4.504E-05 1.000E+04 3.863E-05 1.050E+04 3.337E-05 1.100E+04 2.903E-05 1.150E+04 2.150E+04 2.05 1.250E+04 1.979E-05 1.300E+04 1.760E-05 1.350E+04 1.571E-05 1.400E+04 1.409E-05 1.450E+04-05268E 사전> <사전>주파수 v(4) 1.000E-06 1.000E-04 1.000E-02 1.000E+00 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 5.000E+02 1.935E-01 . . . * . 1.000E+03 3.275E-02 . . . * . 1.500E+03 1.057E-02 . . * . 2.000E+03 4.614E-03 . . * . . 2.500E+03 2.402E-03 . . * . . 3.000E+03 1.403E-03 . . * . . 3.500E+03 8.884E-04 . . * . . 4.000E+03 5.973E-04 . . * . . 4.500E+03 4.206E-04 . . * . . 5.000E+03 3.072E-04 . . * . . 5.500E+03 2.311E-04 . . * . . 6.000E+03 1.782E-04 . . * . . 6.500E+03 1.403E-04 . .* . . 7.000E+03 1.124E-04 . * . . 7.500E+03 9.141E-05 . * . . 8.000E+03 7.536E-05 . *. . . 8.500E+03 6.285E-05 . *. . . 9.000E+03 5.296E-05 . * . . . 9.500E+03 4.504E-05 . * . . . 1.000E+04 3.863E-05 . * . . . 1.050E+04 3.337E-05 . * . . . 1.100E+04 2.903E-05 . * . . . 1.150E+04 2.541E-05 . * . . . 1.200E+04 2.237E-05 . * . . . 1.250E+04 1.979E-05 . * . . . 1.300E+04 1.760E-05 . * . . . 1.350E+04 1.571E-05 . * . . . 1.400E+04 1.409E-05 . * . . . 1.450E+04 1.268E-05 . * . . . 1.500E+04 1.146E-05 . * . . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

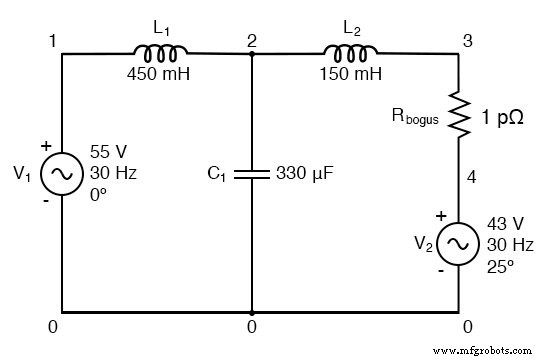

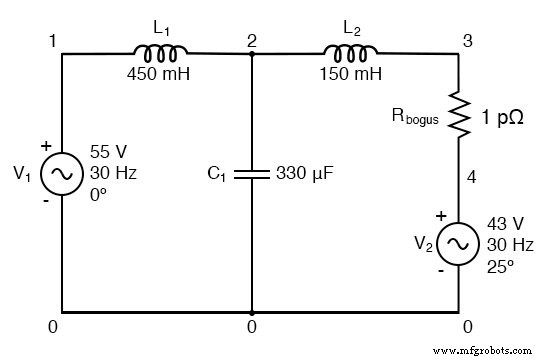

SPICE의 특징 중 하나는 직렬 전압 소스와 인덕터로만 구성된 회로의 루프를 처리할 수 없다는 것입니다. 따라서 V1의 "루프"는 -L1 -L2 -V2 -V1 허용되지 않습니다.

이 문제를 해결하려면 low - 루프의 어딘가에 저항 저항을 넣어 끊습니다. 따라서 R가짜가 있습니다. 3~4(저항 1피코옴) 및 V2 4와 0 사이. 위의 회로는 원래 디자인이고 아래의 회로에는 R가짜가 있습니다. SPICE 오류를 피하기 위해 삽입되었습니다.

넷리스트:

다중 ac 소스 v1 1 0 ac 55 0 sin v2 4 0 ac 43 25 sin l1 1 2 450m c1 2 0 330u l2 2 3 150m rbogus 3 4 1e-12 .ac lin 30 1.230 ) .끝

출력:

주파수 v(2) 3.000E+01 1.413E+02

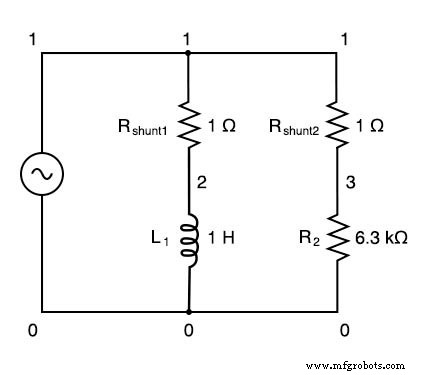

각 레그를 통과하는 전류는 각각의 션트 저항(1 amp =1 볼트에서 1 Ω)에 걸친 전압 강하로 표시되며, v(1,2)에 의해 출력됩니다. 및 v(1,3) .print 약관 카드. 각 레그를 통과하는 전류의 위상은 vp(1,2)에 의해 출력되는 각 션트 저항에 걸친 전압 강하의 위상으로 표시됩니다. 및 vp(1,3) .print의 용어 카드.

넷리스트:

<사전>위상 편이 v1 1 0 ac 4 sin rshunt1 1 2 1 rshunt2 1 3 1 l1 2 0 1 r1 3 0 6.3k .ac lin 1 1000 1000 .print ac v(1,2) v(1,3) vp (1,2) vp(1,3) .end출력:

<사전>주파수 v(1,2) v(1,3) vp(1,2) vp(1,3) 1.000E+03 6.366E-04 6.349E-04 -9.000E+01 0.000E+00

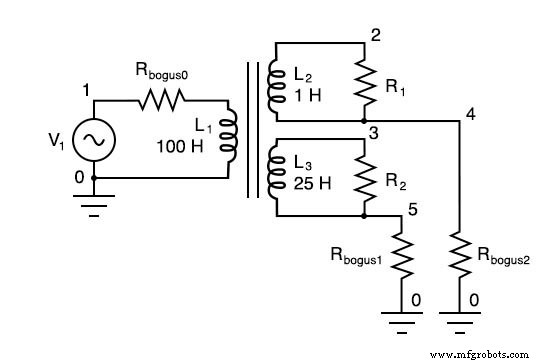

SPICE는 변압기를 상호 결합된 인덕터 세트로 이해합니다. 따라서 SPICE에서 변압기를 시뮬레이션하려면 1차 및 2차 권선을 별도의 인덕터로 지정한 다음 SPICE에 "k ” 카드는 커플링 상수를 지정합니다.

이상적인 변압기 시뮬레이션의 경우 결합 상수는 1이 됩니다(1). 그러나 SPICE는 이 값을 처리할 수 없으므로 0.999와 같은 값을 결합 계수로 사용합니다. 모두 권선 인덕터 쌍은 자체 k와 결합되어야 합니다. 시뮬레이션이 제대로 작동하려면 카드를 사용하십시오. 2권선 변압기의 경우 단일 k 카드로 충분합니다.

3권선 변압기의 경우 3개의 k 카드를 지정해야 합니다(L1를 연결하려면 L2 포함 , L2 L3 포함 , 및 L1 L3 포함 ). L1 /L2 100:1의 인덕턴스 비율은 10:1의 강압 변환 비율을 제공합니다. 120볼트를 입력하면 L2에서 12볼트가 표시되어야 합니다. 굴곡. L1 /L3 100:25(4:1)의 인덕턴스 비율은 2:1 강압 전압 변환 비율을 제공하므로 L3에서 60볼트를 제공해야 합니다. 120볼트의 권선.

넷리스트:

변압기 v1 1 0 ac 120 sin rbogus0 1 6 1e-3 l1 6 0 100 l2 2 4 1 l3 3 5 25 k1 l1 l2 0.999 k2 l2 l3 0.999 93 0l9 0.999 k3 0l1 0 1e10 rbogus2 4 0 1e10 .ac lin 1 60 60 .print ac v(1,0) v(2,0) v(3,0) .end

출력:

주파수 v(1) v(2) v(3) 6.000E+01 1.200E+02 1.199E+01 5.993E+01

이 예에서 Rbogus0 V1의 소스/인덕터 루프를 분리하는 역할을 하는 매우 낮은 값의 저항입니다. /L1 . R가짜1 및 Rbogus2 절연된 각 회로의 접지에 DC 경로를 제공하는 데 필요한 매우 높은 값의 저항기입니다. 또한 1차 회로의 한 쪽은 직접 접지되어 있습니다. 이러한 접지 참조가 없으면 SPICE는 오류를 생성합니다!

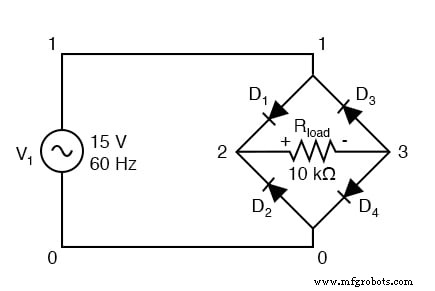

SPICE의 모든 반도체 구성 요소와 마찬가지로 다이오드는 SPICE가 작동 방식에 대한 모든 핵심 세부 사항을 알 수 있도록 모델링해야 합니다. 다행히 SPICE는 몇 가지 일반 모델과 함께 제공되며 다이오드가 가장 기본입니다. .model 주목 단순히 "d를 지정하는 카드 " mod1의 일반 다이오드 모델 .

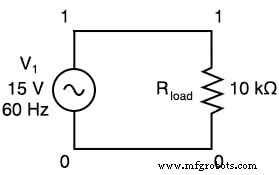

여기서도 파형을 플로팅하므로 단일 카드에 AC 소스의 모든 매개변수를 지정하고 .tran을 사용하여 모든 값을 인쇄/플로팅해야 합니다. 옵션.

넷리스트:

전파 브리지 정류기 v1 1 0 sin(0 15 60 0 0) rload 1 0 10k d1 1 2 mod1 d2 0 2 mod1 d3 3 1 mod1 d4 3 0 mod1 .model mod1 d .tran .5mplot 25m (1,0) v(2,3) .end

출력:

<사전>범례:*:v(1) +:v(2,3) 시간 v(1) (*)--------- -2.000E+01 -1.000E+01 0.000E+00 1.000E+01 2.000E+01 (+)--------- -5.000E+00 0.000E+00 5.000E+00 1.000E+01 1.500E+01 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 0.000E+00 . + * . . 5.000E-04 2.806E+00 . . + . * . . 1.000E-03 5.483E+00 . . + * . . 1.500E-03 7.929E+00 . . . + * . . 2.000E-03 1.013E+01 . . . +* . 2.500E-03 1.198E+01 . . . . * + . 3.000E-03 1.338E+01 . . . . * + . 3.500E-03 1.435E+01 . . . . * +. 4.000E-03 1.476E+01 . . . . * + 4.500E-03 1.470E+01 . . . . * + 5.000E-03 1.406E+01 . . . . * + . 5.500E-03 1.299E+01 . . . . * + . 6.000E-03 1.139E+01 . . . . *+ . 6.500E-03 9.455E+00 . . . + *. . 7.000E-03 7.113E+00 . . . + * . . 7.500E-03 4.591E+00 . . +. * . . 8.000E-03 1.841E+00 . . + . * . . 8.500E-03 -9.177E-01 . . + *. . . 9.000E-03 -3.689E+00 . . *+ . . . 9.500E-03 -6.380E+00 . . * . + . . 1.000E-02 -8.784E+00 . . * . + . . 1.050E-02 -1.075E+01 . *. . .+ . 1.100E-02 -1.255E+01 . * . . . + . 1.150E-02 -1.372E+01 . * . . . + . 1.200E-02 -1.460E+01 . * . . . + 1.250E-02 -1.476E+01 .* . . . + 1.300E-02 -1.460E+01 . * . . . + 1.350E-02 -1.373E+01 . * . . . + . 1.400E-02 -1.254E+01 . * . . . + . 1.450E-02 -1.077E+01 . *. . .+ . 1.500E-02 -8.726E+00 . . * . + . . 1.550E-02 -6.293E+00 . . * . + . . 1.600E-02 -3.684E+00 . . x . . . 1.650E-02 -9.361E-01 . . + *. . . 1.700E-02 1.875E+00 . . + . * . . 1.750E-02 4.552E+00 . . +. * . . 1.800E-02 7.170E+00 . . . + * . . 1.850E-02 9.401E+00 . . . + *. . 1.900E-02 1.146E+01 . . . . *+ . 1.950E-02 1.293E+01 . . . . * + . 2.000E-02 1.414E+01 . . . . * +. 2.050E-02 1.464E+01 . . . . * + 2.100E-02 1.483E+01 . . . . * + 2.150E-02 1.430E+01 . . . . * +. 2.200E-02 1.344E+01 . . . . * + . 2.250E-02 1.195E+01 . . . . *+ . 2.300E-02 1.016E+01 . . . +* . 2.350E-02 7.917E+00 . . . + * . . 2.400E-02 5.460E+00 . . + * . . 2.450E-02 2.809E+00 . . + . * . . 2.500E-02 -8.297E-04 . + * . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

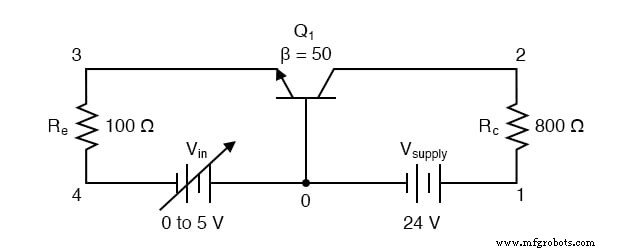

이 분석은 입력 전압(Vin)을 0에서 5볼트로 0.1볼트씩 증가시킨 다음 트랜지스터 v(2,3)의 컬렉터와 이미터 리드 사이의 전압을 출력합니다. 트랜지스터(Q1)는 순방향 베타가 50인 NPN입니다.

넷리스트:

공통 기반 BJT 증폭기 대 공급 1 0 dc 24 vin 0 4 dc rc 1 2 800 re 3 4 100 q1 2 0 3 mod1 .model mod1 npn bf=50 .dc vin 0 5 0.1 .print dc v(2 3) .plot dc v(2,3) .end

출력:

<이전>빈 v(2,3) 0.000E+00 2.400E+01 1.000E-01 2.410E+01 2.000E-01 2.420E+01 3.000E-01 2.430E+01-40E+014 5.000E-01 2.450E+01 6.000E-01 2.460E+01 7.000E-01 2.466E+01 8.000E-01 2.439E+01 9.000E-01 2.383E +00 2.246E+01 1.200E+00 2.174E+01 1.300E+00 2.101E+01 1.400E+00 2.026E+01 1.500E+00 1.951E+01E+00 1.951E+01E+1.0 1.800E+01 1.800E+00 1.724E+01 1.900E+00 1.648E+01 2.000E+00 1.572E+01 2.100E+00 1.495E+01 2.200E +01 2.400E+00 1.265E+01 2.500E+00 1.188E+01 2.600E+00 1.110E+01 2.700E+00 1.033E+01 2.800E+00E+9.0E 3.000E+00 8.014E+00 3.100E+00 7.240E+00 3.200E+00 6.465E+00 3.300E+00 5.691E+00 3.400E+00 4.915E +00 3.364E+00 3.700E+00 2.588E+00 3.800E+00 1.811E+00 3.900E+00 1.034E+00 4.000E+00 2.587E-01+400 7.815E-02 4.300E+00 6.806E-02 4.400E+00 6.141E-02 4.500E+00 5.657E-02 4.600E+00 5.281E-02 4.700E -02 4.90 0E+00 4.525E-02 5.000E+00 4.346E-02 <이전>빈 v(2,3) 0.000E+00 1.000E+01 2.000E+01 3.000E+01 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 2.400E+01 . . . * . 1.000E-01 2.410E+01 . . . * . 2.000E-01 2.420E+01 . . . * . 3.000E-01 2.430E+01 . . . * . 4.000E-01 2.440E+01 . . . * . 5.000E-01 2.450E+01 . . . * . 6.000E-01 2.460E+01 . . . * . 7.000E-01 2.466E+01 . . . * . 8.000E-01 2.439E+01 . . . * . 9.000E-01 2.383E+01 . . . * . 1.000E+00 2.317E+01 . . . * . 1.100E+00 2.246E+01 . . . * . 1.200E+00 2.174E+01 . . . * . 1.300E+00 2.101E+01 . . .* . 1.400E+00 2.026E+01 . . * . 1.500E+00 1.951E+01 . . *. . 1.600E+00 1.876E+01 . . * . . 1.700E+00 1.800E+01 . . * . . 1.800E+00 1.724E+01 . . * . . 1.900E+00 1.648E+01 . . * . . 2.000E+00 1.572E+01 . . * . . 2.100E+00 1.495E+01 . . * . . 2.200E+00 1.418E+01 . . * . . 2.300E+00 1.342E+01 . . * . . 2.400E+00 1.265E+01 . . * . . 2.500E+00 1.188E+01 . . * . . 2.600E+00 1.110E+01 . . * . . 2.700E+00 1.033E+01 . * . . 2.800E+00 9.560E+00 . *. . . 2.900E+00 8.787E+00 . * . . . 3.000E+00 8.014E+00 . * . . . 3.100E+00 7.240E+00 . * . . . 3.200E+00 6.465E+00 . * . . . 3.300E+00 5.691E+00 . * . . . 3.400E+00 4.915E+00 . * . . . 3.500E+00 4.140E+00 . * . . . 3.600E+00 3.364E+00 . * . . . 3.700E+00 2.588E+00 . * . . . 3.800E+00 1.811E+00 . * . . . 3.900E+00 1.034E+00 .* . . . 4.000E+00 2.587E-01 * . . . 4.100E+00 9.744E-02 * . . . 4.200E+00 7.815E-02 * . . . 4.300E+00 6.806E-02 * . . . 4.400E+00 6.141E-02 * . . . 4.500E+00 5.657E-02 * . . . 4.600E+00 5.281E-02 * . . . 4.700E+00 4.981E-02 * . . . 4.800E+00 4.734E-02 * . . . 4.900E+00 4.525E-02 * . . . 5.000E+00 4.346E-02 * . . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

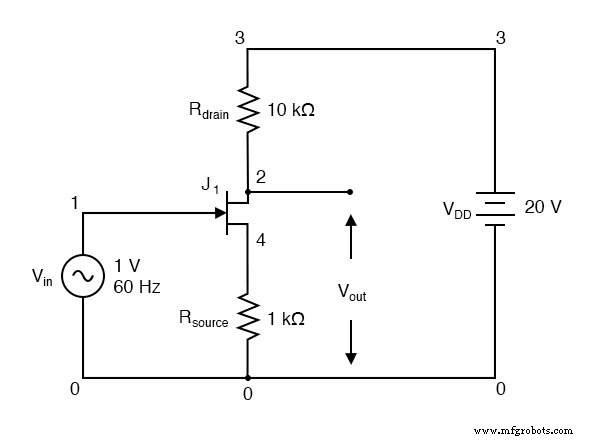

넷리스트:

공통 소스 jfet 증폭기 vin 1 0 sin(0 1 60 0 0) vdd 3 0 dc 20 rdrain 3 2 10k rsource 4 0 1k j1 2 1 4 mod1 .model mod1 njf .tran 1m 30m(2plot tran v ,0) v(1,0) .end

출력:

<사전>범례:*:v(2) +:v(1) 시간 v(2) (*)--------- 1.400E+01 1.600E+01 1.800E+01 2.000E+01 2.200E+01 (+)--------- -1.000E+00 -5.000E-01 0.000E+00 5.000E-01 1.000E+00 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 1.708E+01 . . * + . . 1.000E-03 1.609E+01 . .* . + . . 2.000E-03 1.516E+01 . * . . . + . 3.000E-03 1.448E+01 . * . . . + . 4.000E-03 1.419E+01 .* . . . + 5.000E-03 1.432E+01 . * . . . +. 6.000E-03 1.490E+01 . * . . . + . 7.000E-03 1.577E+01 . * . . +. . 8.000E-03 1.676E+01 . . * . + . . 9.000E-03 1.768E+01 . . + *. . . 1.000E-02 1.841E+01 . + . . * . . 1.100E-02 1.890E+01 . + . . * . . 1.200E-02 1.912E+01 .+ . . * . . 1.300E-02 1.912E+01 .+ . . * . . 1.400E-02 1.890E+01 . + . . * . . 1.500E-02 1.842E+01 . + . . * . . 1.600E-02 1.768E+01 . . + *. . . 1.700E-02 1.676E+01 . . * . + . . 1.800E-02 1.577E+01 . * . . +. . 1.900E-02 1.491E+01 . * . . . + . 2.000E-02 1.432E+01 . * . . . +. 2.100E-02 1.419E+01 .* . . . + 2.200E-02 1.449E+01 . * . . . + . 2.300E-02 1.516E+01 . * . . . + . 2.400E-02 1.609E+01 . .* . + . . 2.500E-02 1.708E+01 . . * + . . 2.600E-02 1.796E+01 . . + * . . 2.700E-02 1.861E+01 . + . . * . . 2.800E-02 1.900E+01 . + . . * . . 2.900E-02 1.916E+01 + . . * . . 3.000E-02 1.908E+01 .+ . . * . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

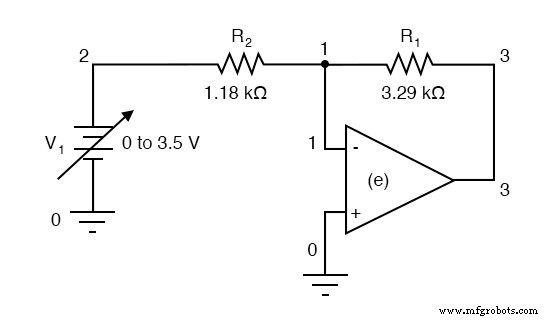

SPICE에서 이상적인 연산 증폭기를 시뮬레이션하기 위해 전압 종속 전압 소스를 매우 높은 이득을 갖는 차동 증폭기로 사용합니다. "에 ” 카드는 4개의 노드로 종속 전압 소스를 설정합니다. 전압 출력은 3과 0, 전압 입력은 1과 0입니다. 실제 연산 증폭기와 달리 종속 전압 소스에 전원 공급 장치가 필요하지 않습니다. 이 경우 전압 이득은 999,000으로 설정됩니다. 입력 전압 소스(V1 ) 0.05볼트 단위로 0에서 3.5볼트로 스윕합니다. 넷리스트:

반전 opamp v1 2 0 dc e 3 0 0 1 999k r1 3 1 3.29k r2 1 2 1.18k .dc v1 0 3.5 0.05 .print dc v(3,0) .end

출력:

<이전>v1 v(3) 0.000E+00 0.000E+00 5.000E-02 -1.394E-01 1.000E-01 -2.788E-01 1.500E-01 -4.182E-01 2.050E-7 -01 2.500E-01 -6.970E-01 3.000E-01 -8.364E-01 3.500E-01 -9.758E-01 4.000E-01 -1.115E+00 4.500E-01 -1.02 01 -1.394E+00 5.500E-01 -1.533E+00 6.000E-01 -1.673E+00 6.500E-01 -1.812E+00 7.000E-01 -1.952E+00E-01 -1.952E+00E-905 00 8.000E-01 -2.231E+00 8.500E-01 -2.370E+00 9.000E-01 -2.509E+00 9.500E-01 -2.649E+00 1.000E+080 -2.07 -2.928E+00 1.100E+00 -3.067E+00 1.150E+00 -3.206E+00 1.200E+00 -3.346E+00 1.250E+00 -3.485E+00 1.300E -3.485E+00 1.300E 1.350E+00 -3.764E+00 1.400E+00 -3.903E+00 1.450E+00 -4.043E+00 1.500E+00 -4.182E+00 1.550E+00 -4.322E 4.461E+00 1.650E+00 -4.600E+00 1.700E+00 -4.740E+00 1.750E+00 -4.879E+00 1.800E+00 -5.019E+00 50 -5.019E+00 1.850E E+00 -5.297E+00 1.950E+00 -5.437E+00 2.000E+00 -5.576E+00 2.050E+00 -5.716E+00 2.100E+00 -5.855E+00 -5.855E+00 2.050E+00 -5.716E+00 E+00 2.200E+00 -6.134E+00 2.250E+00 -6.273E+00 2.300E+00 -6.413E+00 2 .350E+00 -6.552E+00 2.400E+00 -6.692E+00 2.450E+00 -6.831E+00 2.500E+00 -6.970E+00 2.550E+00 -7.110E+ 7.249E+00 2.650E+00 -7.389E+00 2.700E+00 -7.528E+00 2.750E+00 -7.667E+00 2.800E+00 -7.807E+00 2.850E E+00 -8.086E+00 2.950E+00 -8.225E+00 3.000E+00 -8.364E+00 3.050E+00 -8.504E+00 3.100E+00 -8.643E+00 -8.643E+07E+800 E+00 3.200E+00 -8.922E+00 3.250E+00 -9.061E+00 3.300E+00 -9.201E+00 3.350E+00 -9.340E+00 3.400E+00 -+50E +00 -9.619E+00 3.500E+00 -9.758E+00

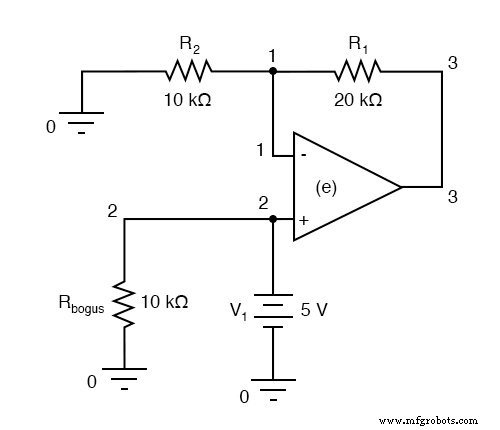

SPICE 문제의 또 다른 예:종속 전압 소스 "e "는 전압 소스 V1에 대한 부하로 간주되지 않습니다. , SPICE는 V1을 해석합니다. 개방되고 분석을 거부할 것입니다. 수정은 R가짜를 연결하는 것입니다. V1과 병렬로 DC 부하로 작동합니다.

V1을 통해 직접 연결됨 , R가짜의 저항 회로 작동에 중요하지 않으므로 10kΩ이 잘 작동합니다. V1을(를) 청소하지 않기로 결정했습니다. 네트리스트 및 출력 목록을 단순하게 유지하기 위해 이 회로에서 입력 전압을 전혀 사용하지 마십시오.

넷리스트:

비반전 opamp v1 2 0 dc 5 rbogus 2 0 10k e 3 0 2 1 999k r1 3 1 20k r2 1 0 10k .end

출력:

노드 전압 노드 전압 노드 전압 ( 1) 5.0000 ( 2) 5.0000 ( 3) 15.0000

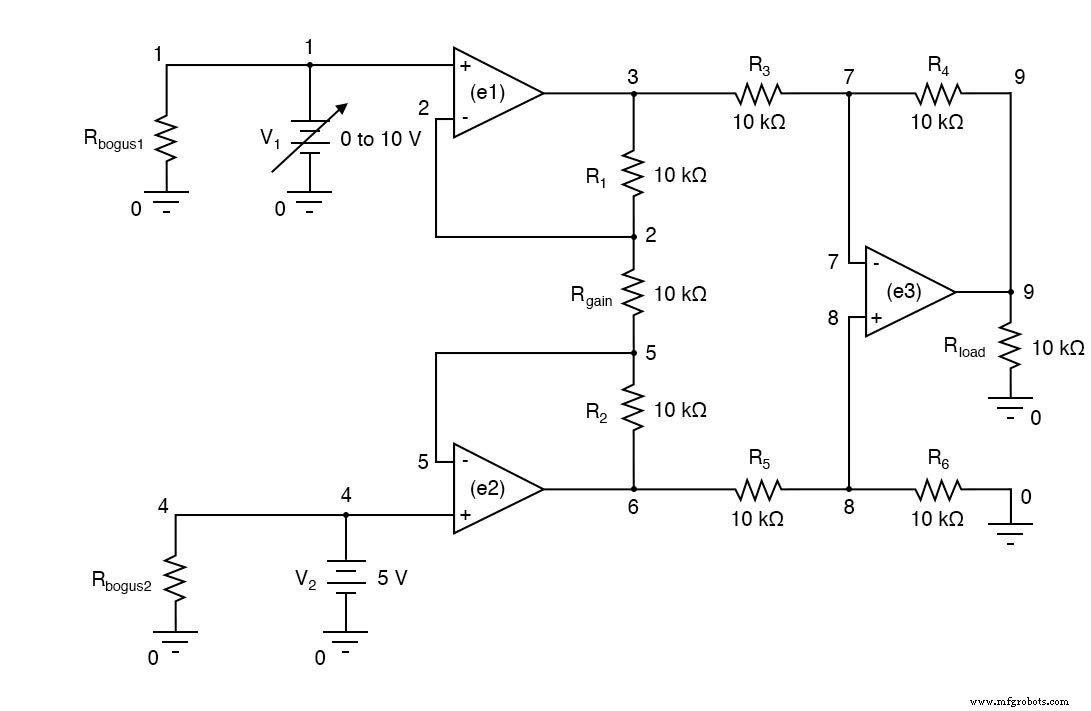

매우 높은 저항 Rbogus1에 주목하십시오. 및 Rbogus2 SPICE가 V1을 생각하지 못하도록 각 입력 전압 소스에 걸쳐 넷리스트의 저항(간결함을 위해 회로도에는 표시되지 않음) 및 V2 다른 연산 증폭기 회로 예제와 마찬가지로 개방 회로였습니다.

넷리스트:

계측 증폭기 v1 1 0 rbogus1 1 0 9e12 v2 4 0 dc 5 rbogus2 4 0 9e12 e1 3 0 1 2 999k e2 6in 0 4 5 999k e3 9 0 8 7 1 999k 10k r2 5 6 10k r3 3 7 10k r4 7 9 10k r5 6 8 10k r6 8 0 10k .dc v1 0 10 1 .print dc v(9) v(3,6) .end

출력:

<이전>v1 v(9) v(3,6) 0.000E+00 1.500E+01 -1.500E+01 1.000E+00 1.200E+01 -1.200E+01 2.000E+00 9.000E+00 -9 E+00 3.000E+00 6.000E+00 -6.000E+00 4.000E+00 3.000E+00 -3.000E+00 5.000E+00 9.955E-10 -9.956E-11 -9.956E-11 -9.956E-11 -9.956E-11 6.000E+00 -3.000E+00 00 3.000E+00 7.000E+00 -6.000E+00 6.000E+00 8.000E+00 -9.000E+00 9.000E+00 9.000E+00 -1.200E+01.001.2 E+01 1.500E+01

넷리스트:

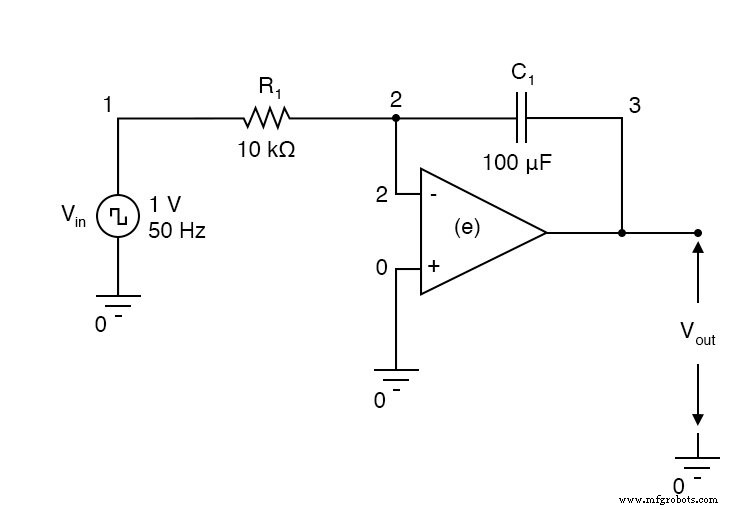

사인파 입력이 있는 적분기 vin 1 0 sin (0 15 60 0 0) r1 1 2 10k c1 2 3 150u ic=0 e 3 0 0 2 999k .tran 1m 30m uic .plot tran v(1,0) (3,0) .end

출력:

<사전>범례:*:v(1) +:v(3) 시간 v(1) (*)-------- -2.000E+01 -1.000E+01 0.000E+00 1.000E+ 01 (+)-------- -6.000E-02 -4.000E-02 -2.000E-02 0.000E+00 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 6.536E-08 . . * + . 1.000E-03 5.516E+00 . . . * +. . 2.000E-03 1.021E+01 . . . + * . 3.000E-03 1.350E+01 . . . + . * . 4.000E-03 1.495E+01 . . + . . *. 5.000E-03 1.418E+01 . . + . . * . 6.000E-03 1.150E+01 . + . . . * . 7.000E-03 7.214E+00 . + . . * . . 8.000E-03 1.867E+00 .+ . . * . . 9.000E-03 -3.709E+00 . + . * . . . 1.000E-02 -8.805E+00 . + . * . . . 1.100E-02 -1.259E+01 . * + . . . 1.200E-02 -1.466E+01 . * . + . . . 1.300E-02 -1.471E+01 . * . +. . . 1.400E-02 -1.259E+01 . * . . + . . 1.500E-02 -8.774E+00 . . * . + . . 1.600E-02 -3.723E+00 . . * . +. . 1.700E-02 1.870E+00 . . . * + . 1.800E-02 7.188E+00 . . . * + . . 1.900E-02 1.154E+01 . . . + . * . 2.000E-02 1.418E+01 . . .+ . * . 2.100E-02 1.490E+01 . . + . . *. 2.200E-02 1.355E+01 . . + . . * . 2.300E-02 1.020E+01 . + . . * . 2.400E-02 5.496E+00 . + . . * . . 2.500E-02 -1.486E-03 .+ . * . . 2.600E-02 -5.489E+00 . + . * . . . 2.700E-02 -1.021E+01 . + * . . . 2.800E-02 -1.355E+01 . * . + . . . 2.900E-02 -1.488E+01 . * . + . . . 3.000E-02 -1.427E+01 . * . .+ . . - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

넷리스트:

방형파 입력 vin 1 0 펄스가 있는 적분기(-1 1 0 0 0 10m 20m) r1 1 2 1k c1 2 3 150u ic=0 e 3 0 0 2 999k .tran 1m 50m uic(1,plot tran v 0) v(3,0) .end

출력: <(1) +:v(3) 시간 v(1) (*)————-1.000E+00 -5.000E-01 0.000E+00 5.000E-01 1.000E+00 (+)——— —-1.000E-01 -5.000E-02 0.000E+00 5.000E-02 1.000E-01 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 0.000E+00 -1.000E+00 * . + . . 1.000E-03 1.000E+00 . . + . * 2.000E-03 1.000E+00 . . + . . * 3.000E-03 1.000E+00 . . + . . * 4.000E-03 1.000E+00 . . + . . * 5.000E-03 1.000E+00 . . + . . * 6.000E-03 1.000E+00 . . + . . * 7.000E-03 1.000E+00 . . + . . * 8.000E-03 1.000E+00 . .+ . . * 9.000E-03 1.000E+00 . +. . . * 1.000E-02 1.000E+00 . + . . . * 1.100E-02 1.000E+00 . + . . . * 1.200E-02 -1.000E+00 * + . . . . 1.300E-02 -1.000E+00 * + . . . . 1.400E-02 -1.000E+00 * +. . . . 1.500E-02 -1.000E+00 * .+ . . . 1.600E-02 -1.000E+00 * . + . . . 1.700E-02 -1.000E+00 * . + . . . 1.800E-02 -1.000E+00 * . + . . . 1.900E-02 -1.000E+00 * . + . . . 2.000E-02 -1.000E+00 * . + . . . 2.100E-02 1.000E+00 . . + . . * 2.200E-02 1.000E+00 . . + . . * 2.300E-02 1.000E+00 . . + . . * 2.400E-02 1.000E+00 . . + . . * 2.500E-02 1.000E+00 . . + . . * 2.600E-02 1.000E+00 . .+ . . * 2.700E-02 1.000E+00 . +. . . * 2.800E-02 1.000E+00 . + . . . * 2.900E-02 1.000E+00 . + . . . * 3.000E-02 1.000E+00 . + . . . * 3.100E-02 1.000E+00 . + . . . * 3.200E-02 -1.000E+00 * + . . . . 3.300E-02 -1.000E+00 * + . . . . 3.400E-02 -1.000E+00 * + . . . . 3.500E-02 -1.000E+00 * + . . . . 3.600E-02 -1.000E+00 * +. . . . 3.700E-02 -1.000E+00 * .+ . . . 3.800E-02 -1.000E+00 * . + . . . 3.900E-02 -1.000E+00 * . + . . . 4.000E-02 -1.000E+00 * . + . . . 4.100E-02 1.000E+00 . . + . . * 4.200E-02 1.000E+00 . . + . . * 4.300E-02 1.000E+00 . . + . . * 4.400E-02 1.000E+00 . .+ . . * 4.500E-02 1.000E+00 . +. . . * 4.600E-02 1.000E+00 . + . . . * 4.700E-02 1.000E+00 . + . . . * 4.800E-02 1.000E+00 . + . . . * 4.900E-02 1.000E+00 . + . . . * 5.000E-02 1.000E+00 + . . . * - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

산업기술

높은 DC 전압 테스트 장비를 구축할 계획입니까? 이러한 장치는 전자레인지 및 음극선관과 같이 높은 DC 전압이 필요한 전자 제품 및 기기를 테스트하거나 구축하는 데 필요합니다. 이 작업을 위해 승압 변압기와 정류기를 사용할 수 있지만 변압기는 무겁고 값 비싼 구성 요소입니다. 따라서 최상의 솔루션을 제공하지 않습니다. 전압 더블은 조립하는 데 몇 가지 구성 요소만 필요한 더 나은 대안입니다. 프로젝트를 위해 하나를 구축하려는 경우 모든 세부 사항을 제시했습니다. 그러나 먼저 전압 더블러의 정의와 유형을 살펴보겠습니다. 전압 더블러

현재 패션 및 의류 소매업에서 RFID 채택의 거대한 물결이 일어나고 있습니다. 이러한 성장은 주로 정확한 재고 데이터의 필요성에 기반한 반면 RFID 배포 비용은 크게 감소했습니다. 이 도움말에서는 몇 가지 비용 지침을 제공합니다. 개선점 지적 미래 산업의 비용. 1. 태그 수동 태그 일반적으로 범위 20센트부터 가장 간단한 번호판 태그의 경우 몇 달러 열, 추위 또는 화학 물질로부터 태그를 보호하기 위해 열쇠 고리 또는 플라스틱 하우징에 내장된 응답기용. 그러나 일반 수동 RFID 태그는 금속 물체에서 제대로 작동하지