산업기술

직렬 입력, 직렬 출력 시프트 레지스터는 각 단계에 대해 한 클럭 시간만큼 데이터를 지연시킵니다.

그들은 각 레지스터에 대해 약간의 데이터를 저장합니다. 직렬 입력 직렬 출력 시프트 레지스터는 길이가 1~64비트일 수 있으며 레지스터 또는 패키지가 캐스케이드된 경우 더 길 수 있습니다.

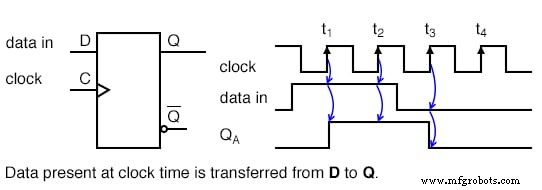

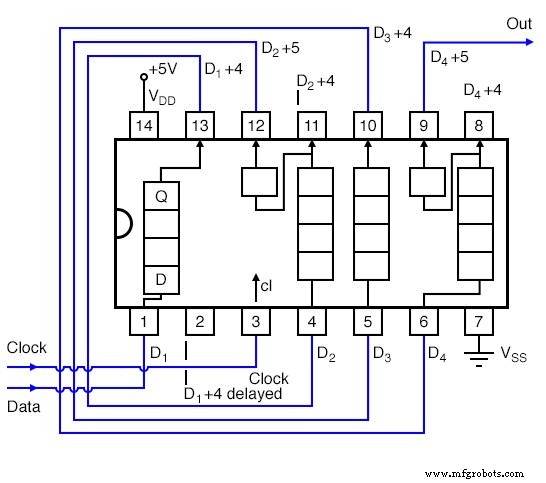

아래는 레지스터 클럭과 동기화되지 않은 데이터를 수신하는 단일 스테이지 시프트 레지스터입니다.

D의 "데이터 입력" D 유형의 핀 FF (Flip-Flop)은 클록이 낮음에서 높음으로 변경될 때 레벨을 변경하지 않습니다.

디지털 논리 회로의 신뢰성을 향상시키기 위해 회로 기판의 시스템 전체 클록에 데이터를 동기화할 수 있습니다.

위에 설명된 분명한 점(아래 그림과 비교)은 D에 있는 "데이터"가 무엇이든 간에 D 유형의 핀 FF는 클록 시간에 D에서 출력 Q로 전송됩니다.

예제 시프트 레지스터는 양의 에지 감지 저장 요소를 사용하므로 출력 Q D 다음에 위 다이어그램의 위쪽 화살표와 같이 클럭이 로우에서 하이로 전환될 때 입력합니다.

클럭 에지 전후에 데이터가 안정적이기 때문에 클럭 시간에 어떤 논리 레벨이 존재하는지 의심의 여지가 없습니다.

다단계 시프트 레지스터에서는 거의 발생하지 않습니다. 그러나 이것은 시작하기 쉬운 예였습니다. 우리는 포지티브(낮음에서 높음)의 클록 에지에만 관심이 있습니다.

하강 에지는 무시할 수 있습니다. Q를 매우 쉽게 볼 수 있습니다. D 팔로우 위의 시간에.

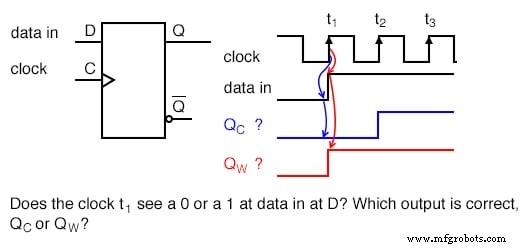

이를 "data in"이 양의 클록 에지로 변경되는 것으로 보이는 아래 다이어그램과 비교하십시오.

"data in"이 시계 시간 t1에 변경되는 것으로 나타나기 때문에 위의 D 유형은 FF 시계 시간에 봅니까?

짧게 지나치게 단순화한 대답은 D에 있던 데이터를 본다는 것입니다. 시계 전에.

이것이 Q로 전송되는 것입니다. 시계 시간 t1에 . 올바른 파형은 QC입니다. . t1에서 Q가 이미 0이 아니면 0이 됩니다.

D 레지스터는 시간 t2까지 1을 표시하지 않습니다. , 이때 Q가 높아집니다.

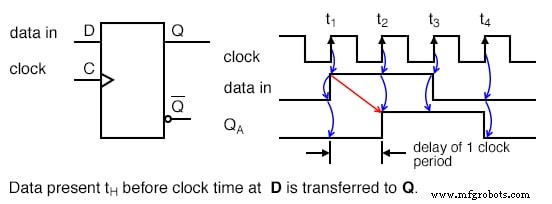

위의 데이터가 D에 있으므로 Q 시계 시계 시간 및 Q 다음 시계 시간, D까지 변경할 수 없습니다. FF는 데이터가 이미 클럭에 동기화되어 있는 경우 한 클럭 주기만큼 데이터를 지연시킵니다. QA 파형은 1클럭 주기 지연이 있는 "데이터 입력"과 동일합니다.

D 유형의 입력이 무엇인지 자세히 살펴보기 플립 플롭은 시계 시간에 다음을 봅니다.

아래 그림을 참조하십시오. "데이터 입력"은 시계 시간(위)에 변경되는 것으로 나타나므로 D FF가 보입니다.

"데이터 입력"이 다른 시프트 레지스터 단계에서 온 경우 다른 동일한 유형 D FF, 데이터 시트를 기반으로 몇 가지 결론을 도출할 수 있습니다. 정보.

디지털 로직 제조업체는 이전에는 데이터 북이라는 컬렉션에서만 사용할 수 있었던 데이터 시트에서 부품에 대한 정보를 제공합니다. .

데이터 북은 여전히 사용할 수 있습니다. 하지만 제조업체의 웹 사이트는 최신 소스입니다.

다음 데이터는 5VDC에서 작동하기 위해 CD4006b 데이터 시트에서 추출되었습니다. , 타이밍을 설명하기 위한 예시로 사용됩니다. [*]

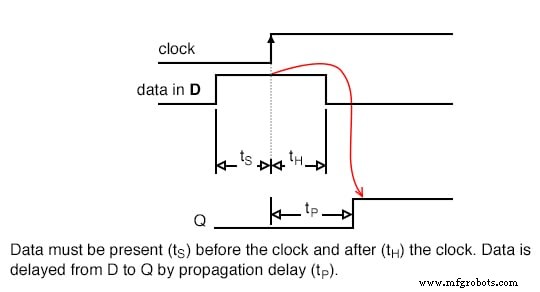

<울>tS 설정 시간입니다. , 시간 데이터는 시계 시간 이전에 있어야 합니다. 이 경우 데이터는 D에 있어야 합니다. 클럭 100ns 전입니다.

또한 데이터는 보류 시간 동안 유지되어야 합니다. tH =클럭 시간 후 60ns. D의 데이터를 안정적으로 시계에 표시하려면 이 두 가지 조건이 충족되어야 합니다. Q로 플립플롭.

D의 데이터로 60ns의 설정 시간을 맞추는 데 문제가 없습니다. 다른 시프트 레지스터 단계에서 온 경우 전체 이전 클록 기간 동안 거기에 있었습니다.

예를 들어, 1Mhz의 클록 주파수에서 클록 주기는 1000μs로 충분한 시간입니다.

데이터는 클록 이전에 실제로 1000µs 동안 존재하며, 이는 최소 요구 tS보다 훨씬 큽니다. 60ns.

유지 시간 tH 다른 단의 Q에 연결된 D는 이전 단의 전파 지연 tP보다 더 빠르게 변할 수 없기 때문에 =60ns가 충족됩니다. =200ns.

홀드 타임은 이전 D의 전파 지연만큼 충족됩니다. FF는 홀드 시간보다 큽니다.

D의 데이터 다른 단계에 의해 주도 Q CD4006b의 경우 200ns보다 빠르게 변경되지 않습니다.

요약하자면 출력 Q 플립플롭이 다단계 시프트 레지스터에 캐스케이드되면 거의 클록 시간에 입력 D를 따릅니다.

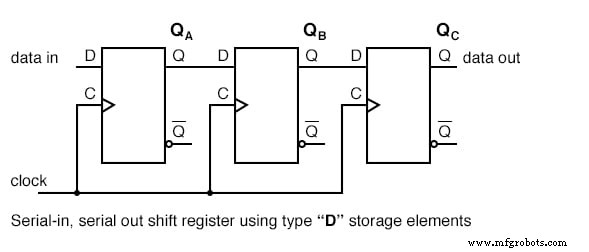

세 가지 유형 D 플립플롭은 Q에서 D로 캐스케이드되고 클럭은 병렬로 연결되어 위의 3단계 시프트 레지스터를 형성합니다.

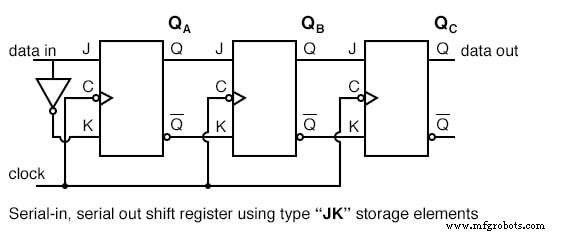

JK 입력 Flip Flopss는 위의 시프트 레지스터의 대체 형태를 생성하기 위해 병렬 클럭을 사용하여 Q에서 J, Q'에서 K로 캐스케이드되었습니다.

직렬 입력/직렬 출력 시프트 레지스터에는 클럭 입력, 데이터 입력 및 마지막 단계의 데이터 출력이 있습니다.

일반적으로 다른 스테이지 출력은 사용할 수 없습니다. 그렇지 않으면 직렬 입력, 병렬 출력 시프트 레지스터가 됩니다.

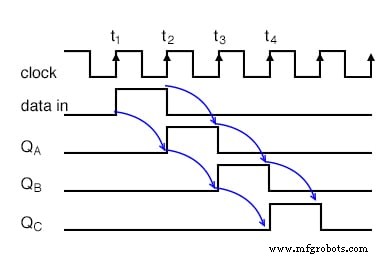

아래 파형은 직렬 입력, 직렬 출력 시프트 레지스터의 이전 두 버전 중 하나에 적용할 수 있습니다.

3쌍의 화살표는 3단계 시프트 레지스터가 3비트 데이터를 임시로 저장하고 입력에서 출력까지 3클록 주기만큼 지연시키는 것을 보여줍니다.

시계 시간 t1에 0의 "데이터" D부터 시계 Q로 세 단계 모두. 특히 D A 단계 논리 0을 봅니다. , QA로 클럭됩니다. 시간 t2까지 남아 있는 위치 .

시계 시간 t2에서 1의 "데이터" D부터 시계 QA에게 . B 단계에서 및 C , 0 , 이전 단계에서 공급된 것은 QB로 클럭됩니다. 및 QC .

시계 시간 t3에 0의 "데이터" D부터 시계 QA에게 . QA "data in"이 0이기 때문에 나머지 클럭 동안 낮게 유지되고 낮게 유지됩니다. . QB t3에서 높음 1로 인해 이전 단계에서. QC t3 이후에도 여전히 낮습니다. 이전 단계보다 낮았기 때문입니다.

QC 마침내 시계 t4에서 하이가 됩니다. D에게 높은 공급량으로 인해 이전 단계에서 QB . 모든 이전 단계에는 0이 있습니다. 그들로 이동했습니다. 그리고 t5에서 다음 클럭 펄스 이후 , 모든 논리 1 s가 제거되고 0으로 대체됩니다.

Texas Instruments에서 제공하는 집적 회로로 제공되는 다음 부품을 자세히 살펴보겠습니다.

전체 장치 데이터 시트를 보려면 링크를 따르십시오.

<울>다음 직렬 입력/직렬 출력 시프트 레지스터는 4000 시리즈 CMOS입니다. (상보성 금속 산화물 반도체) 제품군 부품.

따라서 VDD , 3볼트 ~ 15볼트의 양극 전원 공급 장치. VSS 핀이 접지되어 있습니다.

VDD에 따라 달라지는 시프트 클록의 최대 주파수 , 몇 메가헤르츠입니다.

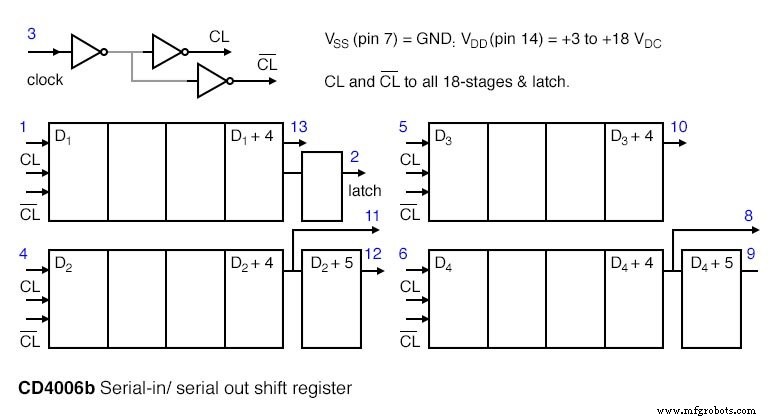

18비트 CD4006b는 4비트의 두 단계와 4비트의 출력 탭이 있는 5비트의 두 단계로 구성됩니다.

따라서 5비트 스테이지를 4비트 시프트 레지스터로 사용할 수 있습니다.

전체 18비트 시프트 레지스터를 얻으려면 한 시프트 레지스터의 출력을 다른 시프트 레지스터의 입력으로 계단식으로 배열해야 하며 모든 단계에서 아래와 같이 단일 시프트 레지스터를 생성할 때까지 계속됩니다.

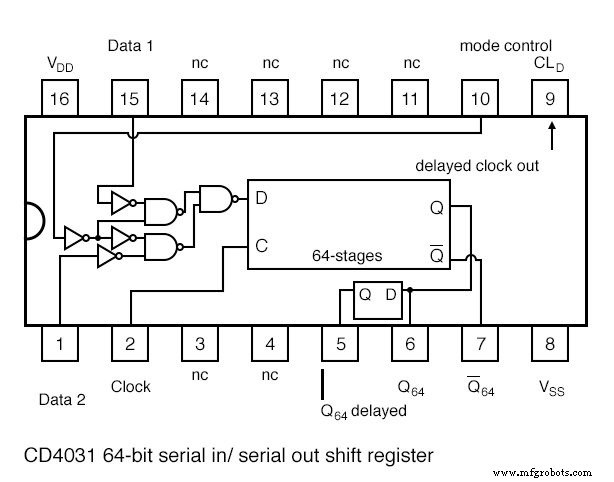

CD4031 64비트 직렬 입력/직렬 출력 시프트 레지스터는 아래와 같습니다.

여러 핀이 연결되지 않았습니다(nc). Q와 Q'는 모두 64단계부터 사용 가능하며 실제로는 Q64입니다. 및 Q'64 .

Q64도 있습니다. 클럭 사이클의 반만큼 지연되는 반 단계에서 "지연"됩니다. 주요 기능은 시프트 레지스터에 데이터 입력에 있는 데이터 선택기입니다.

"모드 제어"는 데이터 1과 데이터 2의 두 입력 중에서 선택합니다. "모드 제어"가 높으면 시프트 레지스터에 입력하기 위해 "데이터 2"에서 데이터가 선택됩니다.

"모드 제어"가 로직 로우인 경우 "데이터 1"이 선택됩니다. 이에 대한 예가 아래 두 그림에 나와 있습니다.

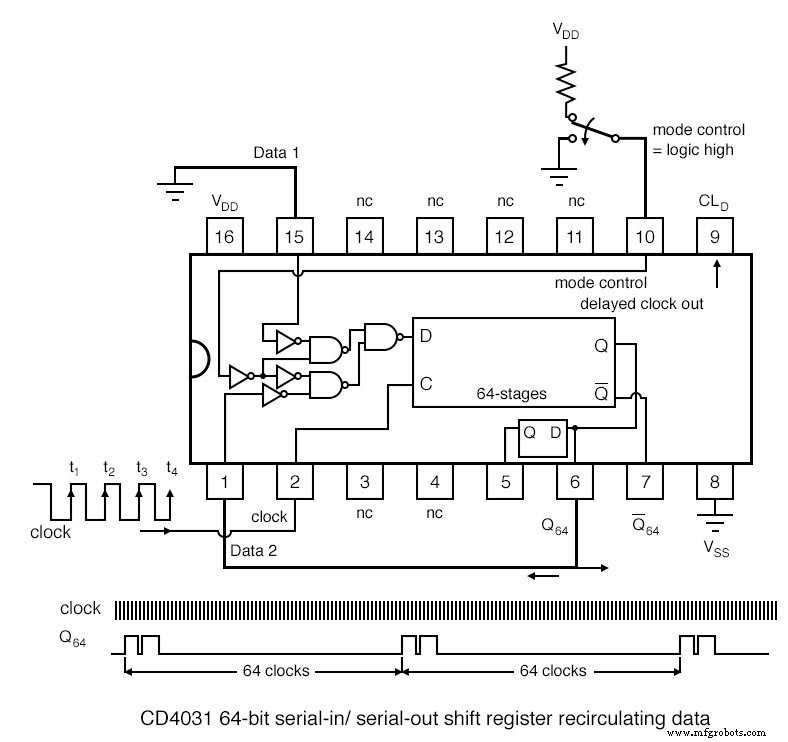

위의 "데이터 2"는 Q64에 연결됩니다. 시프트 레지스터의 출력. "모드 제어"가 높으면 Q64 출력은 시프터 데이터 입력 D로 다시 라우팅됩니다.

데이터가 재순환됩니다. 출력에서 입력으로. 데이터는 위와 같이 64 클럭 펄스마다 반복됩니다.

발생하는 질문은 이 데이터 패턴이 처음에 시프트 레지스터에 어떻게 들어갔습니까?

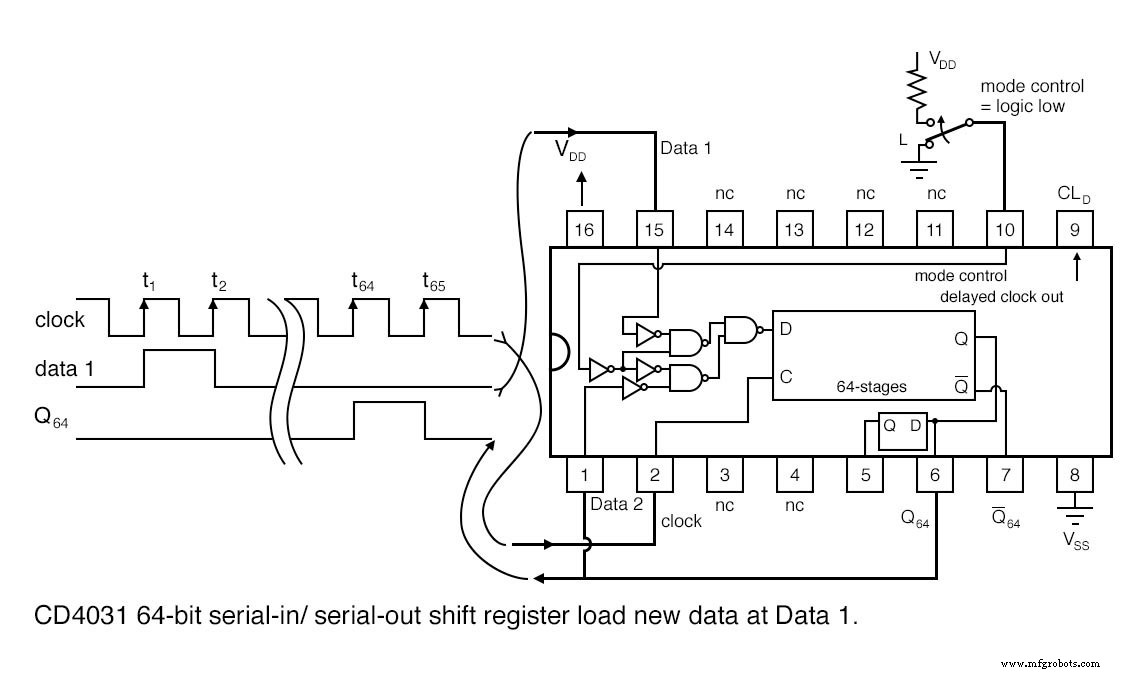

"mode control"이 낮으면 CD4031 "data 1"이 시프터에 대한 입력으로 선택됩니다.

출력, Q64 , 하위 데이터 선택기 게이트가 비활성화되어 있으므로 재순환되지 않습니다. .

비활성화라는 것은 낮은 NAND 게이트에서 낮은 논리로 두 번 반전된 논리 "모드 선택"이 낮은 핀(데이터 2)의 모든 신호를 게이트 출력으로 전달하는 것을 방지한다는 것을 의미합니다.

따라서 비활성화됩니다.

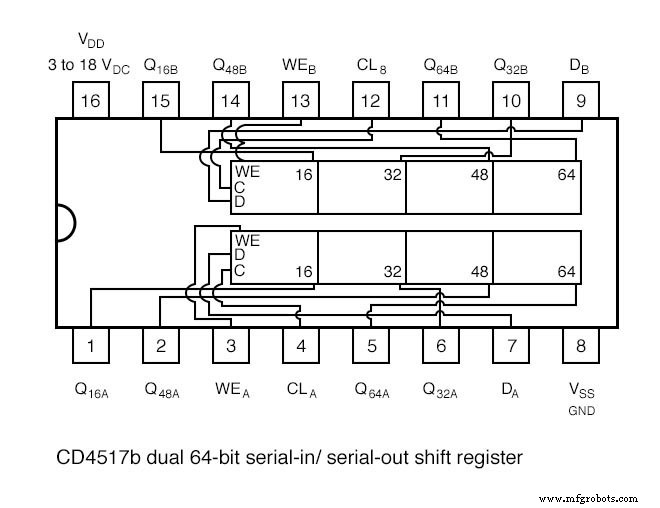

CD4517b 이중 64비트 시프트 레지스터가 위에 나와 있습니다. 16, 32, 48단계의 탭에 유의하세요.

즉, 64비트 시프터 중 하나에서 해당 길이의 시프트 레지스터를 구성할 수 있습니다.

물론 64비트 시프터를 계단식으로 연결하여 80비트, 96비트, 112비트 또는 128비트 시프트 레지스터를 생성할 수 있습니다.

시계 CLA 및 CLB 두 개의 시프터를 계단식으로 연결할 때 병렬로 연결해야 합니다. 우리B 그리고 WEB 정상적인 변속 작업을 위해 접지되어 있습니다.

시프트 레지스터 A 및 B에 대한 데이터 입력은 DA입니다. 및 DB 각각.

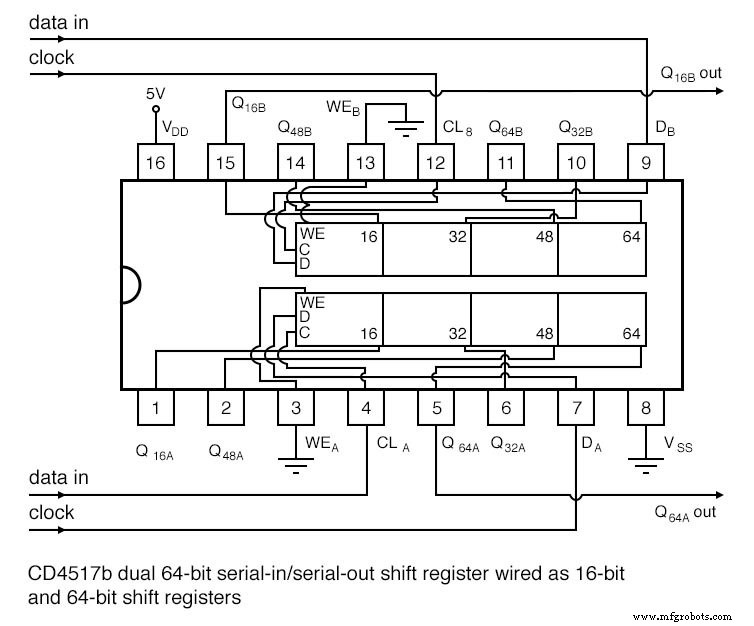

16비트 시프트 레지스터가 필요하다고 가정합니다.

CD4517b로 구성할 수 있습니까? 같은 부품의 64시프트 레지스터는 어떻습니까?

위에서 섹션 B에 대해 16비트 시프트 레지스터로 연결된 A CD4517b를 보여줍니다.

섹션 B의 시계는 CLB입니다. . 데이터는 CLB에서 클럭인됩니다. . 그리고 16클록 지연된 데이터는 Q16B에서 선택됩니다. . 우리B , 쓰기 활성화가 접지되어 있습니다.

위에서 우리는 또한 독립 섹션 A에 대한 64비트 시프트 레지스터로 연결된 동일한 CD4517b를 보여줍니다.

섹션 A의 시계는 CLA입니다. . 데이터는 CLA에 입력됩니다. . 64클럭 펄스만큼 지연된 데이터는 Q64A에서 선택됩니다. . 우리A , 섹션 A에 대한 쓰기 활성화가 접지되어 있습니다.

관련 워크시트:

<울>산업기술

Arduino 직렬:Arduino를 통한 직렬 통신 직렬 통신의 배경: 마이크로 컨트롤러 또는 마이크로 프로세서가 외부 세계와 통신해야 할 때 데이터를 8비트 패킷 형태로 제공하므로 한 시스템이 다른 시스템과 통신해야 하는 경우 총 8선 케이블이 사용되며 항상 그런 것은 아닙니다. 장거리 여행 시 신호가 왜곡되기 때문에 실용적인 솔루션입니다. 그것은 또한 8선 묶음의 높은 비용 때문에 비싸다 이 프로토콜은 새로운 프로토콜의 필요성이 각성된 이후에 병렬 통신으로 명명되었으며 설계자는 직렬 프로토콜로 명명된 새로운 프로토콜을 도입하여

easymon은 스마트폰 세계의 사용 편의성을 머신 컨트롤러 영역으로 가져오는 원격 모니터링 솔루션입니다. PLCnext 스토어에서 PLCnext 기능 확장을 설치하고 iOS 또는 Google Play 스토어에서 해당 스마트폰 앱을 설치하기만 하면 됩니다. 빠르고 쉬운 구성 후에 선택한 데이터 포인트 업데이트가 페어링된 스마트폰 앱 인스턴스에 전파됩니다. 현재 실행 중인 PLCnext 프로그램의 각 변수는 모니터링되는 데이터 포인트로 구성할 수 있습니다. 1. 디자인에 의한 개인정보 보호 사용 편의성 외에도 easymon을 개발하