산업기술

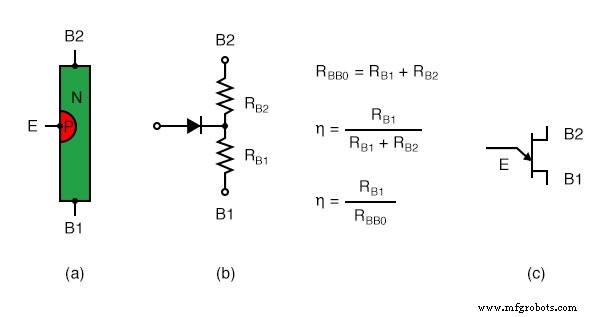

단접합 트랜지스터: 단접합 트랜지스터는 사이리스터가 아니지만 이 장치는 베이스 B1에서 펄스를 사용하여 더 큰 사이리스터를 트리거할 수 있습니다. 단접합 트랜지스터 중간에 P 형 연결이있는 N 형 실리콘 막대로 구성됩니다. 그림 (a)를 참조하십시오. 막대 끝의 연결은 베이스 B1 및 B2로 알려져 있습니다. P형 중간점은 이미 터입니다. 이미터가 분리된 상태에서 총 저항 RBBO , 데이터시트 항목은 RB1의 합계입니다. 및 RB2 그림 (b)와 같이. RBBO 다양한 장치 유형에 대해 4-12kΩ 범위입니다. 고유 스탠드오프 비율 η은 RB1의 비율입니다. RBBO로 . 다른 장치에 대해 0.4에서 0.8까지 다양합니다. 도식 기호는 그림(c)

입니다.

단접합 트랜지스터:(a) 구조, (b) 모델, (c) 기호

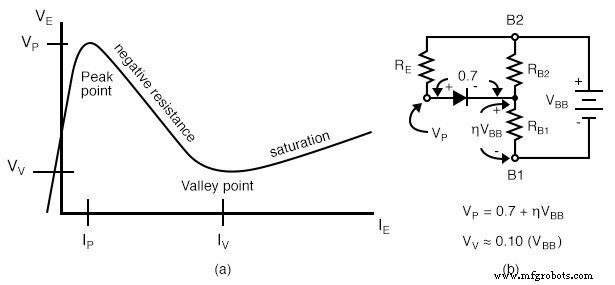

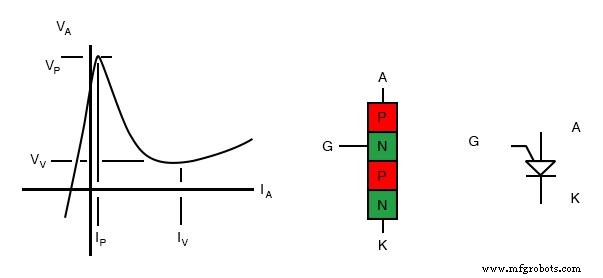

단접합 이미터 전류 대 전압 특성 곡선(아래 그림(a))은 VE 증가, 현재 IE IP 증가 정점에서. 피크 지점을 넘어서면 음의 저항 영역에서 전압이 감소함에 따라 전류가 증가합니다. 전압은 계곡 지점에서 최소값에 도달합니다. RB1의 저항 , 포화 저항은 계곡 지점에서 가장 낮습니다.

나P 그리고 나V , 데이터시트 매개변수입니다. 2n2647의 경우 IP 그리고 나V 각각 2μA 및 4mA입니다. [AMS] VP는 RB1 양단의 전압 강하에 0.7V 다이오드 강하를 더한 값입니다. 아래 그림(b)를 참조하십시오. VV는 VBB의 약 10%로 추정됩니다. .

단접합 트랜지스터:(a) 이미터 특성 곡선, (b) VP용 모델.

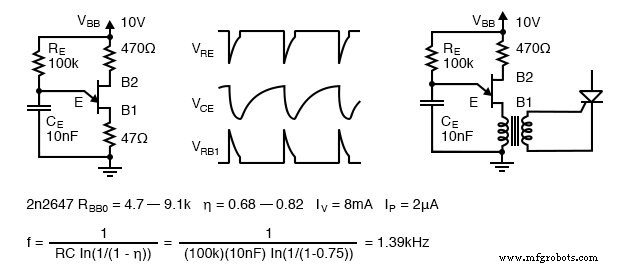

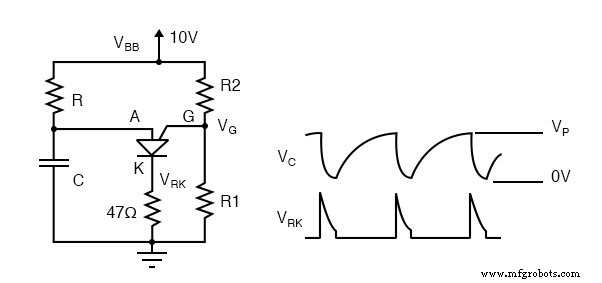

이완 발진기는 단접합 발진기를 응용한 것입니다. RE 요금 CE 정점까지. 단접합 이미터 단자는 이 지점에 도달할 때까지 커패시터에 영향을 미치지 않습니다. 일단 커패시터 전압, VE , 피크 전압 지점에 도달합니다. VP , 낮은 이미 터-베이스1 E-B1 저항은 커패시터를 빠르게 방전합니다. 커패시터가 밸리 포인트 VV 아래로 방전되면 , E-RB1 저항은 다시 높은 저항으로 돌아가고 커패시터는 다시 충전할 수 있습니다.

단접합 트랜지스터 이완 발진기 및 파형. 오실레이터는 SCR을 구동합니다.

E-B1 포화 저항을 통한 커패시터 방전 동안 외부 B1 및 B2 부하 저항에서 펄스를 볼 수 있습니다(위 그림). B1의 부하 저항은 방전 시간에 영향을 미치지 않도록 낮아야 합니다. B2의 외부 저항은 선택 사항입니다. 단락으로 대체될 수 있습니다. 대략적인 주파수는 1/f =T =RC로 표시됩니다. 주파수에 대한 보다 정확한 표현은 위의 그림과 같습니다.

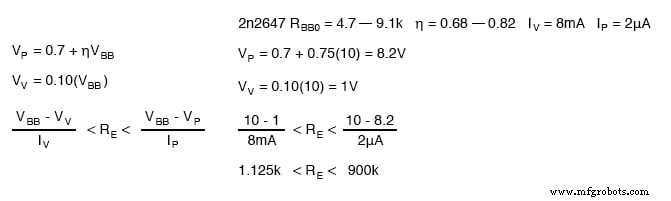

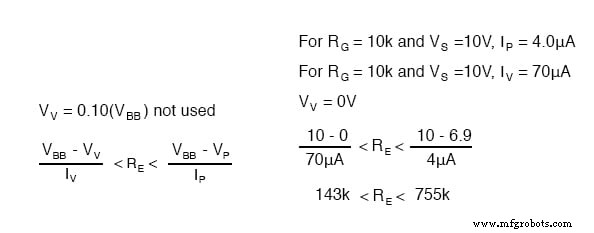

충전 저항 RE 특정 한계 내에 있어야 합니다. IP를 허용할 만큼 작아야 합니다. VBB를 기준으로 흐름 더 적은 공급 VP . IV를 공급하기에 충분히 커야 합니다. VBB 기반 더 적은 공급 VV . [MHW] 2n2647에 대한 방정식 및 예:

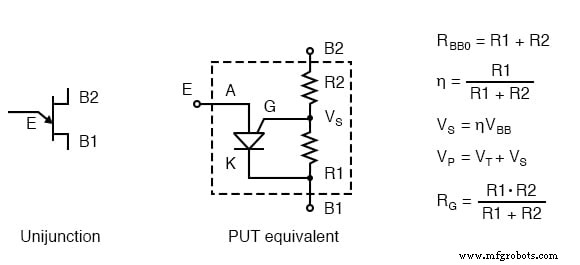

프로그래밍 가능한 단접합 트랜지스터(PUT): 단접합 트랜지스터가 더 이상 사용되지 않는 것으로 나열되어 있지만(구할 수 있으면 비싸게 읽음), 프로그래밍 가능한 단접합 트랜지스터는 살아 있고 잘 작동합니다. 저렴하고 생산중입니다. 단접합 트랜지스터와 유사한 기능을 하지만 PUT는 3단자 사이리스터입니다. PUT은 아래 그림에 표시된 사이리스터의 일반적인 4층 구조를 공유합니다. 양극 근처의 N형 층인 게이트를 "양극 게이트"라고 합니다. 또한, 회로도 기호의 게이트 리드는 기호의 양극 끝에 부착됩니다.

프로그래밍 가능한 단접합 트랜지스터:특성 곡선, 내부 구조, 도식 기호.

위의 그림에서 프로그래밍 가능한 단접합 트랜지스터의 특성 곡선은 단접합 트랜지스터의 특성 곡선과 유사합니다. 이것은 양극 전류 IA의 플롯입니다. 대 양극 전압 VA . 게이트 리드 전압 설정, 프로그램, 피크 양극 전압 VP . 애노드 전류가 증가함에 따라 전압은 피크 지점까지 증가합니다. 그 후 전류가 증가하면 전압이 감소하여 계곡 지점까지 내려갑니다.

단접합 트랜지스터에 해당하는 PUT은 아래 그림에 나와 있습니다. 외부 PUT 저항기 R1 및 R2는 단접합 트랜지스터 내부 저항기 RB1을 대체합니다. 및 RB2 , 각각. 이 저항을 사용하면 고유 스탠드오프 비율 η을 계산할 수 있습니다.

단접합 트랜지스터에 해당하는 PUT

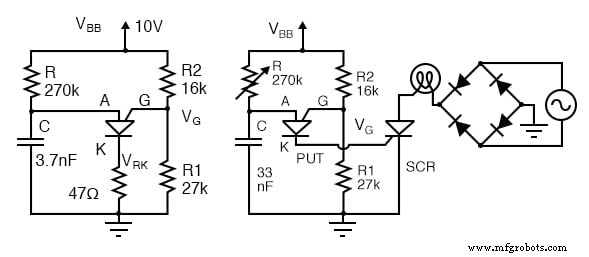

아래 그림은 단접합 완화 발진기의 PUT 버전을 보여줍니다. 저항 R은 피크 지점까지 커패시터를 충전한 다음 강한 전도로 작동 지점을 음의 저항 기울기 아래로 계곡 지점으로 이동합니다. 커패시터 방전 중에 전류 스파이크가 음극을 통해 흐르고 음극 저항에 전압 스파이크가 발생합니다. 커패시터 방전 후 동작점은 피크점까지의 기울기로 다시 재설정됩니다.

PUT 이완 발진기

문제: 이완 발진기 위의 그림에서 R에 적합한 값의 범위는 얼마입니까? 충전 저항은 양극을 VP로 올리기에 충분한 전류를 공급하기에 충분히 작아야 합니다. 커패시터를 충전하는 동안 피크 포인트. 한 번 VP 에 도달하면 전류가 증가함에 따라 양극 전압이 감소하고(음의 저항), 작동 지점을 계곡으로 이동합니다. 밸리 전류 IV를 공급하는 것이 커패시터의 역할입니다. . 일단 방전되면 작동점은 피크점까지 상승 기울기로 다시 재설정됩니다. 저항은 높은 밸리 전류 IP를 공급하지 않을 만큼 충분히 커야 합니다. . 충전 저항이 그렇게 많은 전류를 공급할 수 있다면 커패시터가 방전된 후 저항이 밸리 전류를 공급하고 동작 지점은 피크 지점 왼쪽의 높은 저항 조건으로 다시 재설정되지 않습니다.

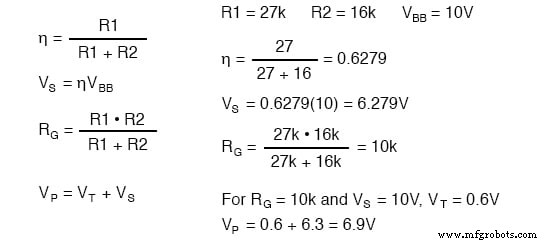

우리는 동일한 VBB를 선택합니다. =10V는 단접합 트랜지스터 예에 사용됩니다. η가 약 2/3이 되도록 R1과 R2의 값을 선택합니다. η와 VS를 계산합니다. R1의 병렬 등가물, R2는 RG입니다. , 아래 표에서 선택하는 데만 사용됩니다. VS와 함께 =10, 6.3에 가장 가까운 값, VT를 찾습니다. =0.6V 및 VP 계산 .

우리는 또한 IP를 찾습니다. 그리고 나V , 피크 및 밸리 전류는 각각 표에 나와 있습니다. 우리는 여전히 VV가 필요합니다 , 계곡 전압. VBB의 10%를 사용했습니다. =1V, 이전 단일접합 예에서. 데이터 시트를 참조하여 순방향 전압 VF를 찾습니다. IF에서 =0.8V =50mA. 계곡 전류 IV =70µA는 IF보다 훨씬 작습니다. =50mA. 따라서 VV VF보다 작아야 합니다. =0.8V. 얼마나 덜? 안전을 위해 VV를 설정합니다. =0V. 이렇게 하면 저항 범위의 하한이 약간 높아집니다.

R> 143k를 선택하면 커패시터가 방전된 후 작동 지점이 밸리 지점에서 재설정될 수 있습니다. R <755k는 VP까지 충전 가능 정점에서.

2n6027 데이터시트에서 채택한 선택된 2n6027 PUT 매개변수. [ON1]

아래 그림은 최종 저항 값이 있는 PUT 완화 발진기를 보여줍니다. SCR을 트리거하는 PUT의 실제 적용도 표시됩니다. 이 회로에는 VBB가 필요합니다. 필터링되지 않은 전원(표시되지 않음)은 각 전력 제로 크로싱 후 이완 발진기를 재설정하기 위해 브리지 정류기에서 분리됩니다. 가변 저항은 최소 저항을 직렬로 연결하여 낮은 냄비 설정이 계곡 지점에 걸리는 것을 방지해야 합니다.

구성 요소 값이 있는 PUT 이완 발진기. PUT은 SCR 램프 조광기를 구동합니다.

PUT 타이밍 회로는 10kHz까지 사용할 수 있다고 합니다. 지수 램프 대신 선형 램프가 필요한 경우 충전 저항을 FET 기반 정전류 다이오드와 같은 정전류 소스로 교체하십시오. 대체 PUT는 음극 게이트를 생략하고 양극 게이트를 사용하여 PNP 및 NPN 실리콘 트랜지스터에서 구축할 수 있습니다.

검토:

<울>관련 워크시트:

<울>산업기술

전기 매니아라면 BC547을 다른 방식으로 접하게 될 것입니다. 여기에서는 BC547 트랜지스터에 대해 알아야 할 모든 것에 대해 논의할 것입니다. 주제에 대해 더 알고 싶으십니까? 당신은 바로 이곳에 왔습니다! BC547은 스위치나 증폭기로 알고 이해하는데 필요한 트랜지스터입니다. 드라이버 모듈, 앰프 모듈 또는 Darlington 쌍으로 작업하는 경우 특히 중요합니다. 이 매혹적인 전자 부품에 대해 더 자세히 알아볼 준비가 되셨습니까? 시작하자! 트랜지스터란 무엇입니까? BC547 트랜지스터가 무엇인지 알아보기 전에

TIP31C Pinout 정보, Negative-Positive-Negative(NPN) 전력 트랜지스터는 바이폴라 접합 트랜지스터 아래에서 신호 또는 회로 애플리케이션을 증폭하고 3개의 레이어를 가지고 있습니다. 또한 전류가 작동을 제어합니다. NPN 트랜지스터 유형에는 TIP41C, 2N9401, BD435, TIP31C, BC107 등이 있습니다. 오늘 우리는 TIP31C 트랜지스터에 대해 알아야 할 모든 정보에 대해 자세히 설명합니다. TIP31C 핀 구성 (TIP31C NPN 트랜지스터 구조) TIP31C는