산업기술

차동 신호 라인에서 전송되는 신호에는 신호의 차동 모드 성분과 공통 모드 성분이 포함됩니다.

차동 신호의 양은 공식 Vdiff에 따라 두 신호 간의 차이를 나타냅니다. =V1 - V2 . 공통 모드 신호의 양은 다음 공식을 따르는 두 신호의 합계의 절반을 나타냅니다.  . 따라서 단일 라인의 전압 변화는 확실히 차동 모드 신호와 공통 모드 신호에 동시에 영향을 미칩니다. 다음으로, 그래프 소프트웨어를 적용하여 차동 모드 신호와 공통 모드 신호에 대한 영향을 각각 연구하기 위해 수학 함수 다이어그램을 그립니다. 연구의 편의를 위해 신호를 동일한 상한 시간과 하강 시간을 갖는 사다리꼴 파형으로 시뮬레이션하여 분석할 수 있습니다.

. 따라서 단일 라인의 전압 변화는 확실히 차동 모드 신호와 공통 모드 신호에 동시에 영향을 미칩니다. 다음으로, 그래프 소프트웨어를 적용하여 차동 모드 신호와 공통 모드 신호에 대한 영향을 각각 연구하기 위해 수학 함수 다이어그램을 그립니다. 연구의 편의를 위해 신호를 동일한 상한 시간과 하강 시간을 갖는 사다리꼴 파형으로 시뮬레이션하여 분석할 수 있습니다.

• 차동 신호에 대한 영향

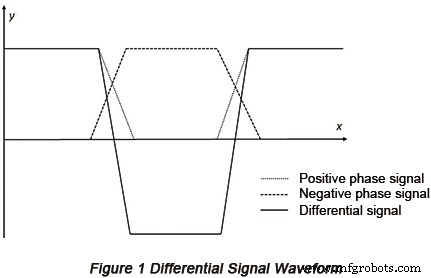

양의 위상 단자 신호, 음의 위상 단자 신호 및 차동 라인 쌍의 차동 신호는 아래 그림 1에 표시되며, 여기서 전체 라인은 차동 신호파를 나타냅니다.

위상 배치가 양의 위상 단자에서 음의 위상 단자로 발생하면 위 또는 아래 가장자리에서 양의 위상 단자 신호와 음의 위상 단자 신호 사이의 차이가 변경되며 이 변화는 위상의 변화에 따라 변경됩니다. Tr 상승 및 하강 시간 중 짧은 시간을 나타내는 데 사용됩니다. 위상 배치가 Tr의 두 번째 지점보다 작을 때 표시될 수 있습니다. , 신호 왜곡은 상대적으로 작고 위상 배치의 증가는 미분 파형의 강한 왜곡으로 이어집니다. 위상 배치가 Tr을 초과하는 경우 , 비단조 영역이 파형에 발생합니다. 여기서 비단조 영역은 직선입니다. 그러나 실제 신호의 경우 반사로 인해 비단조 영역에서 간섭 펄스가 형성되어 잘못된 트리거링으로 이어지는 큰 상승 및 하락이 발생할 수 있으므로 피해야 합니다. 또한, 차동 파형의 상단 에지는 위상 배치가 증가함에 따라 느려지므로 데이터 신호에 대한 설정 시간이 충분하지 않고 클럭 신호에 대한 유지 시간이 충분하지 않을 수 있습니다.

• 공통 모드 신호에 대한 영향

단일 단자 신호의 위상 배치는 차동 파형에 영향을 미치지 않지만 공통 모드 신호의 파형을 변경합니다. 위상 배치가 양극 단자 신호에서 발생하면 파형이 공통 모드 신호로 변경됩니다. 변동 범위는 위상 배치의 양과 관련이 있음을 나타낼 수 있습니다. 위상 배치량이 각각 0.05Tr일 때 , 0.1Tr , 0.2Tr 및 0.5Tr , 공통 모드의 변동 범위는 각각 원래 변동 범위의 5%, 10%, 20% 및 50%입니다. 위상이 Tr로 증가할 때 또는 그 이상이면 변동이 가장 높은 변동 범위인 약 100%까지 증가합니다. 공통 모드 신호의 변경은 EMI 문제로 이어질 수 있으며 많은 조건에서 공통 코드 신호가 터미널에서 수신되지 않기 때문에 수신 터미널에서 반사가 형성되어 신호 링잉이 발생합니다. 따라서 공통 모드 신호의 변동 범위를 최대한 줄여야 합니다.

결론적으로, 차동 쌍 간의 상대적 지연이 너무 크면 신호의 잘못된 트리거, 신호 반사, EMI 및 시간 순서 문제가 발생할 수 있습니다. 그러나 상대 지연 신호의 영향 정도는 신호 Tr과 호환되는 스케일 팩터에 따라 다릅니다. . 스케일 팩터가 0.05이면 차동 신호의 왜곡은 거의 무시할 수 있습니다. 그러나 공통 모드 신호의 경우 스케일 팩터가 0.05일 때 공통 모드 신호의 전압 변동은 약 5%로 제어될 수 있습니다. 그러면 전체 반사 상황에서도 신호 라인에 쌓인 반사 전압은 원래 변동의 10%에 불과하며 일반적으로 허용되는 값입니다. 따라서 고속 PCB 설계 과정에서 라우팅 규정 규칙에서 차동 신호 라인의 상대 지연을 0.05Tr로 설정할 수 있습니다. 신호 무결성 요구 사항을 충족할 수 있습니다.

위의 분석을 바탕으로 차동 아이소메트릭 범주 결정의 핵심, 즉 차동 쌍의 상대적 지연 결정은 Tr 결정에 있습니다. 차동 신호의 상한 및 하강 시간 중 가장 작은 값을 나타냅니다. 상승 시간과 하강 시간의 출력은 실제로 임피던스와 커패시턴스 조합의 출력입니다. 따라서 부하가 없는 상승/하강 시간은 실제로 고유의 상승/하강 시간입니다.

다음 세 가지 방법을 적용하여 Tr 값을 얻을 수 있습니다. :

• 상승/하강 시간은 구성품 설명서에서 직접 얻을 수 있습니다. 그러나 대부분의 경우 이 매개변수는 제공되지 않습니다.

• Tr 값 구성 요소 IBIS(Input/Output Buffer Informational Specification) 모델의 Ramp 키워드에서 얻을 수 있습니다. Ramp 키워드 아래의 상승/하강 시간 매개변수는 일반적으로 최종 전압 시간의 20% ~ 80%인 50Ω의 저항과 연결된 출력 포트에서 측정됩니다. 매개변수는 패키지의 영향을 고려하지 않고 얻어지기 때문에 상승/하강 시간을 Tr 값으로 사용하는 것이 엄격합니다. .

• Tr 값 출력 신호의 최소 클럭 주파수 또는 최대 클럭 주파수에 따라 추정할 수 있습니다. 분배 상승 에지는 대부분의 고속 디지털 시스템에서 클록 주파수의 약 10%이므로 Tr 값 다음 공식을 기반으로 제공된 최소 클록 주기 Tclk로 추정할 수 있습니다. Tr =T클릭 x 10%.

패키지 기생 매개변수 또는 구성 요소의 로딩으로 인해 트랜지스터의 고유한 상승/하강 시간이 크게 느려지기 때문에 클록 주기를 통해 얻은 추정 값은 일반적으로 엄격합니다.

실제 작업에서 대부분의 상황에서 회로 설계자는 Tr 정보를 제공하지 않습니다. 차동 아이소메트릭 제어 측면에서 모호한 요구 사항만 받는 PCB 레이아웃 엔지니어에게 적합합니다. 세 번째 방법은 의심할 여지 없이 신호 라인에서 가장 높은 클록 주파수를 얻는 한 PCB 레이아웃 엔지니어에게 간단한 방식을 제공합니다. 가장 높은 클럭 주파수는 회로 설계자에게 가장 신뢰할 수 있는 설계 매개변수로 간주되며 일반적으로 PCB 설계 초기에 PCB 레이아웃 엔지니어에게 제공됩니다.

세 번째 방법은 일반적으로 아래 표와 같이 차동 쌍 간의 상대 지연 제어 범주 내에서 참조 값 목록으로 이어집니다.

| 클럭 주파수/ns | 클럭 주파수/MHz | 상대 지연 범주/ps | 전송 라인 길이/mil |

| 3.75 | 266 | 18.8 | 105 |

| 3 | 333 | 15 | 84 |

| 2.5 | 400 | 12.5 | 70 |

| 1.87 | 533 | 9.4 | 52 |

| 1.5 | 667 | 7.5 | 42 |

| 1.25 | 800 | 6.3 | 35 |

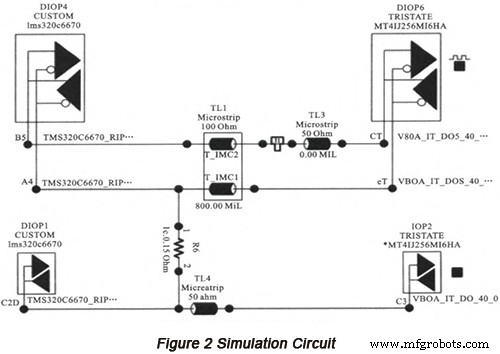

TSM320과 MT41J256M16 사이의 DQS(Data Strobe) 차동 신호를 예로 들면 Cadence 시뮬레이션 소프트웨어가 DOS 신호를 DRR3 메모리로 전송하여 메모리 제어 칩을 시뮬레이션하고 데이터 신호 설정 유지 시간에 미치는 영향을 분석하고 위의 분석을 검증합니다. 시뮬레이션 회로는 아래 그림 2와 같습니다.

그림 2에 따르면 출력 핀의 기준 전압은 1.5V입니다. 메모리 제어 칩은 800mil의 전송 라인으로 ODT(On-Die Termination) 모드를 통해 메모리 칩과 직접 연결됩니다. 차동 임피던스는 100Ω이고 시뮬레이션 클록 주파수는 800MHz입니다. 50Ω의 전송 라인은 차동 쌍의 불일치 현상을 시뮬레이션하기 위해 DQS 양극 위상 단자와 직렬로 연결됩니다. 아이소메트릭 차동의 상황에서 50Ω의 단일 단자 전송 라인의 길이는 0mil입니다.

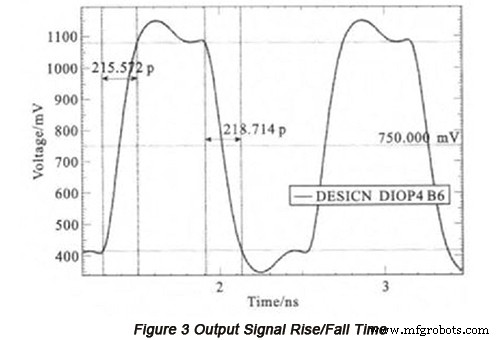

시뮬레이션은 차동 아이소메트릭 회로에 대해 수행됩니다. 그림 3은 차동 신호의 양의 위상 단자에서의 출력 신호를 보여줍니다. 측정을 통해 상승 시간은 약 216ps, 하강 시간은 219ps이므로 최소 상승/하강 시간 Tr 216ps이어야 합니다.

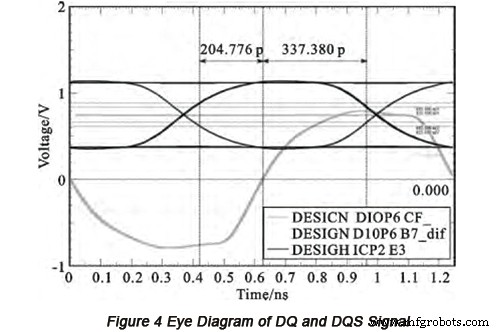

도 4는 설정 시간 205ps 및 유지 시간 337ps로 시뮬레이션을 통한 데이터 신호 DQ 및 게이팅 신호 DQS의 아이 다이어그램이다. 시뮬레이션을 통한 DQS 및 DQ 신호의 턴오버율과 데이터 매뉴얼에 따르면 수신단말에 의한 데이터 신호의 최소 설정 시간은 85ps, 최소 유지 시간은 95ps이다. 따라서 최소 설정 시간의 초과 측정은 120ps이고 유지 시간은 242ps입니다.

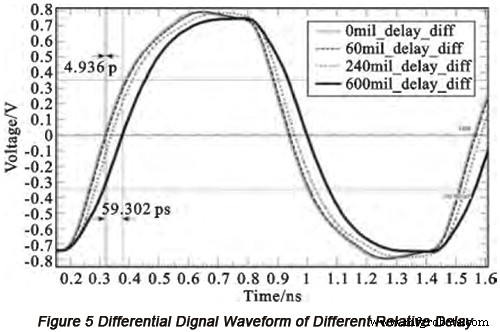

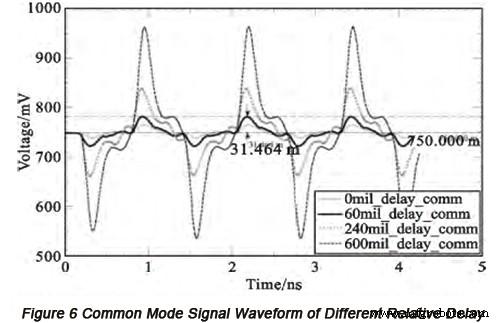

0.05Tr 존재 상황 위상 배치, 0.2Tr 위상 배치 및 0.5Tr 포지티브 위상 단자에서의 위상 배치를 고려해야 합니다. 회로는 각각 60mil, 240mil 및 600mil로 설정된 단일 터미널 전송 라인 길이로 시뮬레이션할 수 있습니다. 4번의 시뮬레이션을 통한 차동 신호 파형과 공통 모드 신호 파형은 그림 5와 6에 나와 있습니다.

그림 5에 따르면 왜곡은 상대 지연이 0.05Tr일 때 최소입니다. 및 0.2Tr 일어난다. 특히 상대 지연이 0.05Tr인 경우 , 상대적 지연 없이 차동 신호에서 차동 신호 파형까지 약 5ps만 배치하여 데이터 신호 설정 초과 측정이 약 5ps 증가하고 초과 측정 유지 시간이 5ps 감소합니다. 홀딩 오버 측정 시간은 줄어들지만, 이 배치량은 242ps의 홀딩 시간에 비해 너무 적습니다. 시간 순서를 피할 수 있습니다. 상대 지연이 0.5Tr인 경우 , DQS 신호 파형의 배치는 약 60ps에 도달했습니다. 이 배치는 여전히 초과 측정 범주에 속하지만 충분한 주의를 기울여야 합니다.

그림 6에 따르면 위상 배치의 증가는 파동의 주기적인 변동과 범위의 점진적인 증가로 이어집니다. 상대 지연이 각각 0.05Tr일 때 , 0.2Tr 및 0.5Tr , 공통 모드 신호의 측정된 피크 값은 각각 61mV, 176mV 및 430mV이며 그 중 가장 높은 값은 가장 낮은 값의 7배입니다. 가장 큰 변동폭은 각각 4.3%, 12%, 29%입니다.

결론적으로 시뮬레이션 결과는 수학 함수 다이어그램 분석을 통해 얻은 결과와 호환됩니다. 차동 쌍 간의 상대 지연이 0.05Tr 미만인 경우 , 신호에 대한 영향은 매우 작습니다.

상대적 지연 제어 범주를 추정하기 위해 출력 단자에서 출력 신호의 최소 클럭 주기가 적용됩니다. 부품 매뉴얼에 따르면 부품의 최소 클럭 주기는 1.25ns이며 클럭 주파수는 800MHz입니다. 표 1에 따르면 상대 지연은 35mil의 전송선로 길이에서 6.3ps 이내로 제어되어야 한다. 분명히 이 값은 0.05Tr의 상대적 지연의 제어 범주보다 훨씬 작습니다. 시뮬레이션을 통해 따라서 추정 상대 지연 제어 범주는 상대적으로 보수적이며 시뮬레이션 결과보다 더 구체적입니다.

유용한 리소스

• 임베디드 애플리케이션 시스템의 고속 PCB 설계에 대한 연구

• 고속 PCB용 이미지 평면 설계 방법

• 신호 무결성 및 솔루션에 대한 고속 PCB 설계 과제

• OrCAD PSpice를 사용한 시뮬레이션 PCB

• PCBCart의 전체 기능 PCB 제조 서비스 - 다양한 부가 가치 옵션

• PCBCart의 고급 PCB 조립 서비스 - 1개부터 시작

산업기술

오늘날 RF/Microwave PCB는 의료, 통신 등을 포함한 수많은 휴대용 무선 장치 및 상업 산업에서 광범위하게 적용되는 것을 목격했습니다. RF(무선 주파수)/Microwave 회로는 피부 효과 및 결합 효과, 간섭 및 회로의 방사선은 실제 인쇄 회로 기판(PCB) 설계에서 제어하기 어렵습니다. 일반적으로 발생하는 문제로는 디지털 회로와 아날로그 회로 간의 교차 간섭, 전원으로 인한 노이즈 간섭, 부조리한 레이아웃으로 인한 유사한 간섭 문제가 있습니다. 결과적으로 PCB 설계의 장점과 단점을 어떻게 균형을 잡고 간섭을 줄이려

2016년 3월 15일 PCB 제조 및 조립 서비스 제공업체는 누군가의 아이디어를 현실로 만드는 막중한 책임이 있습니다. PCB 설계 및 제조 프로세스의 여러 단계에는 다른 파일과 정보가 필요합니다. 따라서 PCB 문서는 클라이언트가 원하는 것을 정확히 제조업체에 전달하는 데 도움이 됩니다. 또한 필요한 정보를 미리 준비하면 전체 처리 시간을 단축할 수 있습니다. 이를 통해 더 쉽고 빠르고 정확한 견적을 얻을 수 있을 뿐만 아니라 오류 없는 PCB 설계 및 제조를 보장합니다. PCB 설계를 위한 중요한 문서 항목 인쇄 회