verilog

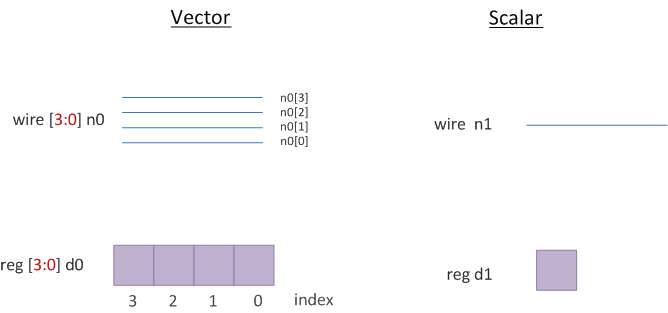

Verilog는 비트 그룹뿐만 아니라 개별 비트도 표현해야 합니다. 예를 들어, 단일 비트 순차 요소는 플립플롭입니다. 그러나 16비트 순차 요소는 16비트를 저장할 수 있는 레지스터입니다. 이를 위해 Verilog에는 scalar가 있습니다. 및 벡터 그물과 변수.

네트 또는 reg 범위 지정이 없는 선언은 1비트 너비로 간주되며 스칼라입니다. . 범위가 지정되면 net 또는 reg 벡터로 알려진 다중 비트 엔티티가 됩니다. .

wire o_nor; // single bit scalar net

wire [7:0] o_flop; // 8-bit vector net

reg parity; // single bit scalar variable

reg [31:0] addr; // 32 bit vector variable to store address

범위는 벡터의 개별 비트를 처리할 수 있는 기능을 제공합니다. 벡터의 최상위 비트는 범위에서 왼쪽 값으로 지정되어야 하고 벡터의 최하위 비트는 오른쪽에 지정되어야 합니다.

wire [msb:lsb] name;

integer my_msb;

wire [15:0] priority; // msb = 15, lsb = 0

wire [my_msb: 2] prior; // illegal

위의 예에서 우선순위라고 하는 16비트 폭의 네트가 생성됩니다. msb 및 lsb 상수 표현식이어야 하며 변수로 대체될 수 없습니다. 그러나 양수, 음수 또는 0과 같은 모든 정수 값이 될 수 있습니다. 및 lsb 값은 msb 값보다 크거나 같거나 작을 수 있습니다.

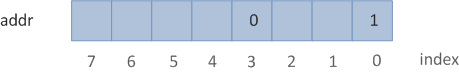

벡터 변수의 모든 비트는 아래와 같이 개별적으로 선택하고 새 값을 할당할 수 있습니다. 이것을 비트 선택이라고 합니다. . 비트 선택이 범위를 벗어나거나 비트 선택이 x인 경우 또는 z , 반환된 값은 x가 됩니다. .

<노스크립트>

reg [7:0] addr; // 8-bit reg variable [7, 6, 5, 4, 3, 2, 1, 0]

addr [0] = 1; // assign 1 to bit 0 of addr

addr [3] = 0; // assign 0 to bit 3 of addr

addr [8] = 1; // illegal : bit8 does not exist in addr

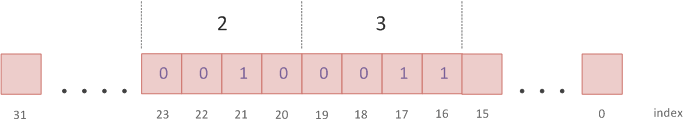

연속 비트 범위를 선택할 수 있으며 부분 선택이라고 합니다. . 부분 선택에는 두 가지 유형이 있습니다. 하나는 일정한 부분 선택을 사용하는 것이고 다른 하나는 색인화된 부분 선택을 사용하는 것입니다.

reg [31:0] addr;

addr [23:16] = 8'h23; // bits 23 to 16 will be replaced by the new value 'h23 -> constant part-select

가변 부분 선택을 사용하면 루프에서 벡터의 부분을 선택하는 데 효과적으로 사용할 수 있습니다. 시작 비트는 다양할 수 있지만 너비는 일정해야 합니다.

[<start_bit> +: <width>] // part-select increments from start-bit [<start_bit> -: <width>] // part-select decrements from start-bit

module des;

reg [31:0] data;

int i;

initial begin

data = 32'hFACE_CAFE;

for (i = 0; i < 4; i++) begin

$display ("data[8*%0d +: 8] = 0x%0h", i, data[8*i +: 8]);

end

$display ("data[7:0] = 0x%0h", data[7:0]);

$display ("data[15:8] = 0x%0h", data[15:8]);

$display ("data[23:16] = 0x%0h", data[23:16]);

$display ("data[31:24] = 0x%0h", data[31:24]);

end

endmodule

시뮬레이션 로그 ncsim> run data[8*0 +: 8] = 0xfe // ~ data [8*0+8 : 8*0] data[8*1 +: 8] = 0xca // ~ data [8*1+8 : 8*1] data[8*2 +: 8] = 0xce // ~ data [8*2+8 : 8*2] data[8*3 +: 8] = 0xfa // ~ data [8*3+8 : 8*3] data[7:0] = 0xfe data[15:8] = 0xca data[23:16] = 0xce data[31:24] = 0xfa ncsim: *W,RNQUIE: Simulation is complete.

module tb;

reg [15:0] data;

initial begin

$display ("data[0:9] = 0x%0h", data[0:9]); // Error : Reversed part-select index expression ordering

end

endmodule

verilog

매개변수는 다른 사양으로 모듈을 재사용할 수 있도록 하는 Verilog 구성입니다. 예를 들어, 4비트 가산기는 비트 수에 대한 값을 허용하도록 매개변수화될 수 있으며 모듈 인스턴스화 중에 새 매개변수 값이 전달될 수 있습니다. 따라서 N비트 가산기는 4비트, 8비트 또는 16비트 가산기가 될 수 있습니다. 함수 호출 중에 전달되는 함수에 대한 인수와 같습니다. parameter MSB = 7; // MSB is a parameter with a constant value 7 paramet

Verilog는 하드웨어 설명 언어이며 설계자가 RTL 설계를 시뮬레이션하여 논리 게이트로 변환할 필요가 없습니다. 시뮬레이션이 필요한 이유는 무엇입니까? 시뮬레이션은 RTL 코드가 의도한 대로 동작하는지 확인하기 위해 다른 시간에 다른 입력 자극을 설계에 적용하는 기술입니다. 기본적으로 시뮬레이션은 설계의 견고성을 검증하기 위해 잘 따라야 하는 기술입니다. 또한 가공된 칩이 실제 세계에서 사용되는 방식과 다양한 입력에 반응하는 방식과 유사합니다. 예를 들어, 위의 디자인은 출력 pe 보여진 바와 같이. 시뮬레이션을 통해