verilog

nand과 같은 표준 Verilog 프리미티브 및 not 복잡한 논리를 표현하기에는 항상 쉽거나 충분하지 않을 수 있습니다. UDP라는 새로운 기본 요소 또는 사용자 정의 프리미티브 조합 논리 또는 순차 논리를 모델링하도록 정의할 수 있습니다.

모든 UDP에는 0, 1 또는 X가 될 수 있고 Z가 될 수 없는 정확히 하나의 출력이 있습니다(지원되지 않음). Z 값을 갖는 모든 입력은 X로 처리됩니다.

Verilog 사용자 정의 프리미티브는 module과 동일한 수준에서 작성할 수 있습니다. 정의, 그러나 module 사이에는 없음 및 endmodule . 그들은 많은 입력 포트를 가질 수 있지만 항상 하나의 출력 포트를 가질 수 있으며 양방향 포트는 유효하지 않습니다. 모든 포트 신호는 스칼라여야 하며 이는 1비트 너비여야 함을 의미합니다.

하드웨어 동작은 기본으로 설명됩니다. table 내에서 가능한 입력과 해당 출력의 다양한 조합을 나열하는 상태 테이블 및 endtable . 입력 및 출력 신호의 값은 다음 기호를 사용하여 표시됩니다.

| 기호 | 댓글 |

|---|---|

| 0 | 논리 0 |

| 1 | 논리 1 |

| x | 알 수 없음, 논리 0 또는 1일 수 있습니다. 입력/출력 또는 순차 UDP의 현재 상태로 사용할 수 있습니다. |

| ? | 논리 0, 1 또는 x. 어떤 UDP도 출력할 수 없습니다. |

| - | 변경 없음, UDP 출력에서만 허용됨 |

| ab | a 또는 b가 0, 1 또는 x인 경우 값을 b에서 변경 |

| * | ??와 동일, 입력 값의 변경을 나타냄 |

| r | 01과 동일 -> 입력 시 상승 에지 |

| f | 10과 동일 -> 입력 시 하강 에지 |

| p | 입력 시 잠재적인 포지티브 에지; 0->1, 0->x 또는 x->1 |

| n | 입력 시 잠재적인 하강 에지; 1->0, x->0, 1->x | 중 하나

// Output should always be the first signal in port list

primitive mux (out, sel, a, b);

output out;

input sel, a, b;

table

// sel a b out

0 1 ? : 1;

0 0 ? : 0;

1 ? 0 : 0;

1 ? 1 : 1;

x 0 0 : 0;

x 1 1 : 1;

endtable

endprimitive

? 신호가 0, 1 또는 x일 수 있으며 최종 출력을 결정하는 데 중요하지 않음을 나타냅니다.

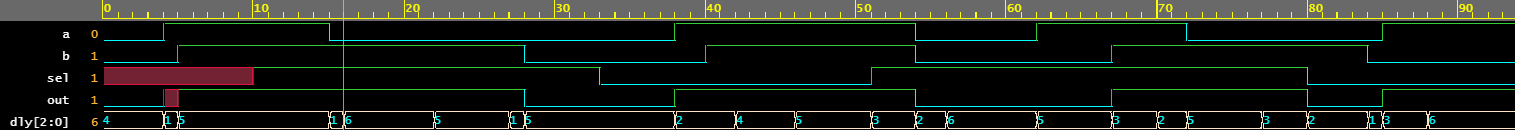

아래는 UDP를 인스턴스화하고 입력 자극을 적용하는 테스트벤치 모듈입니다.

module tb;

reg sel, a, b;

reg [2:0] dly;

wire out;

integer i;

// Instantiate the UDP - note that UDPs cannot

// be instantiated with port name connection

mux u_mux ( out, sel, a, b);

initial begin

a <= 0;

b <= 0;

$monitor("[T=%0t] a=%0b b=%0b sel=%0b out=%0b", $time, a, b, sel, out);

// Drive a, b, and sel after different random delays

for (i = 0; i < 10; i = i + 1) begin

dly = $random;

#(dly) a <= $random;

dly = $random;

#(dly) b <= $random;

dly = $random;

#(dly) sel <= $random;

end

end

endmodule

<노스크립트>  시뮬레이션 로그

시뮬레이션 로그 xcelium> run [T=0] a=0 b=0 sel=x out=0 [T=4] a=1 b=0 sel=x out=x [T=5] a=1 b=1 sel=x out=1 [T=10] a=1 b=1 sel=1 out=1 [T=15] a=0 b=1 sel=1 out=1 [T=28] a=0 b=0 sel=1 out=0 [T=33] a=0 b=0 sel=0 out=0 [T=38] a=1 b=0 sel=0 out=1 [T=40] a=1 b=1 sel=0 out=1 [T=51] a=1 b=1 sel=1 out=1 [T=54] a=0 b=0 sel=1 out=0 [T=62] a=1 b=0 sel=1 out=0 [T=67] a=1 b=1 sel=1 out=1 [T=72] a=0 b=1 sel=1 out=1 [T=80] a=0 b=1 sel=0 out=0 [T=84] a=0 b=0 sel=0 out=0 [T=85] a=1 b=0 sel=0 out=1 xmsim: *W,RNQUIE: Simulation is complete.

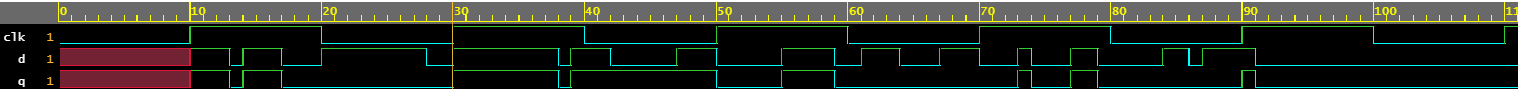

순차 논리는 레벨에 민감하거나 가장자리에 민감할 수 있으므로 두 가지 종류의 순차 UDP가 있습니다. 출력 포트도 reg으로 선언해야 합니다. UDP 정의 내에서 유형을 지정하고 initial 내에서 선택적으로 초기화할 수 있습니다. 성명서.

순차 UDP에는 입력 필드와 출력 필드 사이에 :로 구분되는 추가 필드가 있습니다. 현재 상태를 나타냅니다.

primitive d_latch (q, clk, d);

output q;

input clk, d;

reg q;

table

// clk d q q+

1 1 : ? : 1;

1 0 : ? : 0;

0 ? : ? : -;

endtable

endprimitive

위 표에서 하이픈 - 표의 마지막 행은 q+ 값에 변화가 없음을 나타냅니다.

module tb;

reg clk, d;

reg [1:0] dly;

wire q;

integer i;

d_latch u_latch (q, clk, d);

always #10 clk = ~clk;

initial begin

clk = 0;

$monitor ("[T=%0t] clk=%0b d=%0b q=%0b", $time, clk, d, q);

#10; // To see the effect of X

for (i = 0; i < 50; i = i+1) begin

dly = $random;

#(dly) d <= $random;

end

#20 $finish;

end

endmodule

<노스크립트>  시뮬레이션 로그

시뮬레이션 로그 xcelium> run [T=0] clk=0 d=x q=x [T=10] clk=1 d=1 q=1 [T=13] clk=1 d=0 q=0 [T=14] clk=1 d=1 q=1 [T=17] clk=1 d=0 q=0 [T=20] clk=0 d=1 q=0 [T=28] clk=0 d=0 q=0 [T=30] clk=1 d=1 q=1 [T=38] clk=1 d=0 q=0 [T=39] clk=1 d=1 q=1 [T=40] clk=0 d=1 q=1 [T=42] clk=0 d=0 q=1 [T=47] clk=0 d=1 q=1 [T=50] clk=1 d=0 q=0 [T=55] clk=1 d=1 q=1 [T=59] clk=1 d=0 q=0 [T=60] clk=0 d=0 q=0 [T=61] clk=0 d=1 q=0 [T=64] clk=0 d=0 q=0 [T=67] clk=0 d=1 q=0 [T=70] clk=1 d=0 q=0 [T=73] clk=1 d=1 q=1 [T=74] clk=1 d=0 q=0 [T=77] clk=1 d=1 q=1 [T=79] clk=1 d=0 q=0 [T=80] clk=0 d=0 q=0 [T=84] clk=0 d=1 q=0 [T=86] clk=0 d=0 q=0 [T=87] clk=0 d=1 q=0 [T=90] clk=1 d=1 q=1 [T=91] clk=1 d=0 q=0 [T=100] clk=0 d=0 q=0 [T=110] clk=1 d=0 q=0 Simulation complete via $finish(1) at time 111 NS + 0

D 플립플롭은 아래에 표시된 예에서 Verilog 사용자 정의 프리미티브로 모델링됩니다. 클록의 상승 에지는 01로 지정됩니다. 또는 0?

primitive d_flop (q, clk, d);

output q;

input clk, d;

reg q;

table

// clk d q q+

// obtain output on rising edge of clk

(01) 0 : ? : 0;

(01) 1 : ? : 1;

(0?) 1 : 1 : 1;

(0?) 0 : 0 : 0;

// ignore negative edge of clk

(?0) ? : ? : -;

// ignore data changes on steady clk

? (??): ? : -;

endtable

endprimitive

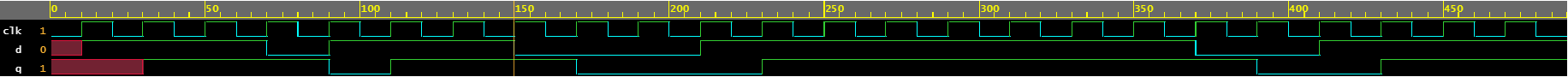

테스트벤치에서 UDP는 임의의 수의 클럭 이후에 임의의 d 입력 값으로 인스턴스화되고 구동됩니다.

module tb;

reg clk, d;

reg [1:0] dly;

wire q;

integer i;

d_flop u_flop (q, clk, d);

always #10 clk = ~clk;

initial begin

clk = 0;

$monitor ("[T=%0t] clk=%0b d=%0b q=%0b", $time, clk, d, q);

#10; // To see the effect of X

for (i = 0; i < 20; i = i+1) begin

dly = $random;

repeat(dly) @(posedge clk);

d <= $random;

end

#20 $finish;

end

endmodule

D 플립플롭에 대해 원하는 동작인 1 클럭 지연 후에 출력 q가 입력 d를 따르는 것을 이미지에서 볼 수 있습니다.

<노스크립트> 시뮬레이션 로그

시뮬레이션 로그 xcelium> run [T=0] clk=0 d=x q=x [T=10] clk=1 d=1 q=x [T=20] clk=0 d=1 q=x [T=30] clk=1 d=1 q=1 [T=40] clk=0 d=1 q=1 [T=50] clk=1 d=1 q=1 [T=60] clk=0 d=1 q=1 [T=70] clk=1 d=0 q=1 [T=80] clk=0 d=0 q=1 [T=90] clk=1 d=1 q=0 [T=100] clk=0 d=1 q=0 [T=110] clk=1 d=1 q=1 [T=120] clk=0 d=1 q=1 [T=130] clk=1 d=1 q=1 [T=140] clk=0 d=1 q=1 [T=150] clk=1 d=0 q=1 [T=160] clk=0 d=0 q=1 [T=170] clk=1 d=0 q=0 [T=180] clk=0 d=0 q=0 [T=190] clk=1 d=0 q=0 [T=200] clk=0 d=0 q=0 [T=210] clk=1 d=1 q=0 [T=220] clk=0 d=1 q=0 [T=230] clk=1 d=1 q=1 [T=240] clk=0 d=1 q=1 [T=250] clk=1 d=1 q=1 [T=260] clk=0 d=1 q=1 [T=270] clk=1 d=1 q=1 [T=280] clk=0 d=1 q=1 [T=290] clk=1 d=1 q=1 [T=300] clk=0 d=1 q=1 [T=310] clk=1 d=1 q=1 [T=320] clk=0 d=1 q=1 [T=330] clk=1 d=1 q=1 [T=340] clk=0 d=1 q=1 [T=350] clk=1 d=1 q=1 [T=360] clk=0 d=1 q=1 [T=370] clk=1 d=0 q=1 [T=380] clk=0 d=0 q=1 [T=390] clk=1 d=0 q=0 [T=400] clk=0 d=0 q=0 [T=410] clk=1 d=1 q=0 [T=420] clk=0 d=1 q=0 [T=430] clk=1 d=1 q=1 [T=440] clk=0 d=1 q=1 [T=450] clk=1 d=1 q=1 [T=460] clk=0 d=1 q=1 [T=470] clk=1 d=1 q=1 [T=480] clk=0 d=1 q=1 Simulation complete via $finish(1) at time 490 NS + 0

verilog

매개변수는 다른 사양으로 모듈을 재사용할 수 있도록 하는 Verilog 구성입니다. 예를 들어, 4비트 가산기는 비트 수에 대한 값을 허용하도록 매개변수화될 수 있으며 모듈 인스턴스화 중에 새 매개변수 값이 전달될 수 있습니다. 따라서 N비트 가산기는 4비트, 8비트 또는 16비트 가산기가 될 수 있습니다. 함수 호출 중에 전달되는 함수에 대한 인수와 같습니다. parameter MSB = 7; // MSB is a parameter with a constant value 7 paramet

Verilog는 하드웨어 설명 언어이며 설계자가 RTL 설계를 시뮬레이션하여 논리 게이트로 변환할 필요가 없습니다. 시뮬레이션이 필요한 이유는 무엇입니까? 시뮬레이션은 RTL 코드가 의도한 대로 동작하는지 확인하기 위해 다른 시간에 다른 입력 자극을 설계에 적용하는 기술입니다. 기본적으로 시뮬레이션은 설계의 견고성을 검증하기 위해 잘 따라야 하는 기술입니다. 또한 가공된 칩이 실제 세계에서 사용되는 방식과 다양한 입력에 반응하는 방식과 유사합니다. 예를 들어, 위의 디자인은 출력 pe 보여진 바와 같이. 시뮬레이션을 통해