VHDL

모듈은 VHDL 코드의 독립된 단위입니다. 모듈은 엔티티를 통해 외부 세계와 통신합니다. . 항구 지도 모듈의 입력과 출력이 연결될 로컬 신호를 선언하는 모듈 인스턴스화의 일부입니다.

이 시리즈의 이전 자습서에서는 기본 VHDL 파일에 모든 코드를 작성했지만 일반적으로 그렇게 하지 않습니다. 시뮬레이터가 아닌 FPGA 또는 ASIC 설계에 사용할 목적으로 로직을 생성합니다.

시뮬레이터에서 실행하기 위해 생성된 VHDL 모듈에는 일반적으로 입력 또는 출력 신호가 없습니다. 완전히 독립적입니다. 그래서 우리 디자인의 엔터티가 비어 있습니다. entity 사이에 아무 것도 없었습니다. 태그 및 end entity; 태그.

이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다.

입력 또는 출력 신호가 없는 모듈은 실제 설계에 사용할 수 없습니다. 유일한 목적은 시뮬레이터에서 VHDL 코드를 실행할 수 있도록 하는 것입니다. 따라서 이를 테스트벤치라고 합니다. . 입력 및 출력 신호가 있는 모듈을 시뮬레이션하려면 인스턴스화해야 합니다. 테스트벤치에 있습니다.

모듈과 테스트벤치는 종종 쌍으로 제공되며 서로 다른 파일에 저장됩니다. 일반적인 이름 지정 체계는 테스트벤치에 "Tb"가 추가된 모듈 이름을 호출하고 아키텍처 이름을 "sim"으로 지정하는 것입니다. 모듈이 "MyModule"이라고 하면 테스트벤치는 "MyModuleTb"라고 합니다. 결과적으로 파일 이름은 "MyModuleTb.vhd" 및 "MyModule.vhd"가 됩니다.

테스트벤치 코드의 도움으로 모듈이 시뮬레이션 환경에서 올바르게 작동하는지 확인할 수 있습니다. 테스트 중인 모듈은 일반적으로 테스트 중인 기기라고 합니다. (DUT).

모듈은 다른 모듈 내에서 인스턴스화될 수도 있습니다. 코드를 모듈로 분할하면 여러 번 인스턴스화할 수 있습니다. 동일한 디자인 내에서 모듈의 여러 인스턴스를 생성할 수 있으며 여러 디자인에서 재사용할 수 있습니다.

VHDL에 포트가 있는 엔터티의 구문은 다음과 같습니다.entity <entity_name> is

port(

<entity_signal_name> : in|out|inout <signal_type>;

...

);

end entity;

다른 VHDL 파일에서 이러한 모듈을 인스턴스화하는 구문은 다음과 같습니다.<label> : entity <library_name>.<entity_name>(<architecture_name>) port map(

<entity_signal_name> => <local_signal_name>,

...

);

<label> 임의의 이름이 될 수 있으며 ModelSim의 계층 창에 표시됩니다. <library_name> 모듈은 VHDL 코드가 아니라 시뮬레이터에서 설정됩니다. 기본적으로 모든 모듈은 work로 컴파일됩니다. 도서관. <entity_name> 및 <architecture_name> 인스턴스를 생성하는 모듈과 일치해야 합니다. 마지막으로 각 엔티티 신호는 로컬 신호 이름에 매핑되어야 합니다.

VHDL에서 모듈을 인스턴스화하는 다른 방법이 있지만 이것이 명시적 인스턴스화의 기본 구문입니다.

이 비디오 자습서에서는 VHDL에서 모듈을 만들고 인스턴스화하는 방법을 배웁니다.

MUX testbench의 최종 코드 :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_PortMapTb is

end entity;

architecture sim of T15_PortMapTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output : unsigned(7 downto 0);

begin

-- An instance of T15_Mux with architecture rtl

i_Mux1 : entity work.T15_Mux(rtl) port map(

Sel => Sel,

Sig1 => Sig1,

Sig2 => Sig2,

Sig3 => Sig3,

Sig4 => Sig4,

Output => Output);

-- Testbench process

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

end architecture;

MUX 모듈의 최종 코드 :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_Mux is

port(

-- Inputs

Sig1 : in unsigned(7 downto 0);

Sig2 : in unsigned(7 downto 0);

Sig3 : in unsigned(7 downto 0);

Sig4 : in unsigned(7 downto 0);

Sel : in unsigned(1 downto 0);

-- Outputs

Output : out unsigned(7 downto 0));

end entity;

architecture rtl of T15_Mux is

begin

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output <= Sig1;

when "01" =>

Output <= Sig2;

when "10" =>

Output <= Sig3;

when "11" =>

Output <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output <= (others => 'X');

end case;

end process;

end architecture;

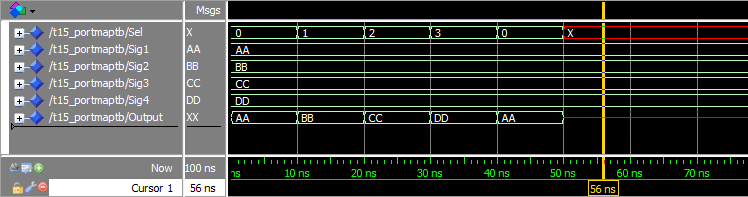

실행을 누르고 타임라인을 확대한 후 ModelSim의 파형 창:

파형에서 볼 수 있듯이 멀티플렉서(MUX) 모듈은 예상대로 작동합니다. 파형은 모듈을 사용하지 않고 생성한 이전 자습서의 파형과 동일합니다.

이제 디자인 모듈과 테스트벤치 사이에 명확한 구분이 있습니다. MUX를 포함하는 모듈은 우리가 설계에 사용하려는 것이며 테스트벤치의 유일한 목적은 시뮬레이터에서 실행할 수 있도록 하는 것입니다. 테스트벤치에 wait을 사용하는 프로세스가 있습니다. 시뮬레이션에서 인위적인 시간 지연을 생성하기 위한 명령문. 디자인 모듈은 시간 개념이 없으며 외부 자극에만 반응합니다.

테스트벤치의 아키텍처 이름을 sim로 지정했습니다. , 시뮬레이션용. 디자인 모듈의 아키텍처는 rtl로 명명되었습니다. , 레지스터 전송 수준을 나타냅니다. 이들은 단지 명명 규칙입니다. 이러한 이름의 파일을 보면 테스트벤치인지 디자인 모듈인지 즉시 알 수 있습니다. 회사마다 명명 규칙이 다를 수 있습니다.

다음 튜토리얼로 이동 »

VHDL

이전 자습서에서 For-Loop를 사용하여 정수 범위를 반복하는 방법을 배웠습니다. 그러나 고정된 정수 범위보다 루프를 더 자세히 제어하려면 어떻게 해야 할까요? 이를 위해 While 루프를 사용할 수 있습니다. While 루프는 테스트하는 표현식이 true로 평가되는 한 계속해서 동봉된 코드를 반복합니다. . 따라서 While-Loop는 얼마나 많은 반복이 필요한지 미리 알 수 없는 상황에 적합합니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. While 루프의 구문은 다음과 같습니다. while <

이 Arduino 튜토리얼에서는 PIR 센서가 작동하는 방식과 모션 감지를 위해 Arduino 보드와 함께 사용하는 방법을 배웁니다. 다음 비디오를 보거나 아래에 작성된 튜토리얼을 읽을 수 있습니다. 작동 방식 먼저 작동 원리를 설명하겠습니다. 모듈은 실제로 열에 노출될 때 에너지를 생성하는 초전기 센서로 구성됩니다. 즉, 사람이나 동물의 몸이 센서 범위에 들어가면 사람이나 동물의 몸이 적외선 형태의 열 에너지를 방출하기 때문에 움직임을 감지합니다. 여기서 센서의 이름인 수동적외선(Passive Infra-Red) 센서