VHDL

Case-When 문은 신호, 변수 또는 표현식의 값에 따라 프로그램이 여러 경로 중 하나를 선택하도록 합니다. 여러 Elsif가 있는 If-Then-Elsif-Else 문에 대한 보다 우아한 대안입니다.

다른 프로그래밍 언어는 switch와 같은 키워드를 사용하여 유사한 구조를 가지고 있습니다. , 대소문자 , 또는 선택 . 무엇보다도 Case-When 문은 VHDL에서 멀티플렉서를 구현하는 데 일반적으로 사용됩니다. 계속 읽으시거나 동영상을 시청하여 방법을 알아보세요!

이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다.

Case-When 문의 기본 구문은 다음과 같습니다.case <expression> is

when <choice> =>

code for this branch

when <choice> =>

code for this branch

...

end case;

<expression> 일반적으로 변수 또는 신호입니다. Case 문에는 여러 when이 포함될 수 있습니다. 선택사항이지만 하나의 선택사항만 선택됩니다.

<choice> "11"와 같은 고유한 값일 수 있습니다. :when "11" =>

또는 5 to 10과 같은 범위일 수 있습니다. :when 5 to 10 =>

1|3|5과 같은 여러 값을 포함할 수 있습니다. :when 1|3|5 =>

그리고 가장 중요한 것은 others 선택. 다른 선택 항목이 일치하지 않을 때마다 선택됩니다.when others =>

others 선택 항목은 Else과 동일합니다. If-Then-Elsif-Else 문의 분기.

이 비디오 자습서에서는 VHDL에서 Case-When 문을 사용하여 멀티플렉서를 만드는 방법을 배웁니다.

이 튜토리얼에서 만든 최종 코드:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T14_CaseWhenTb is

end entity;

architecture sim of T14_CaseWhenTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output1 : unsigned(7 downto 0);

signal Output2 : unsigned(7 downto 0);

begin

-- Stimuli for the selector signal

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

-- MUX using if-then-else

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

if Sel = "00" then

Output1 <= Sig1;

elsif Sel = "01" then

Output1 <= Sig2;

elsif Sel = "10" then

Output1 <= Sig3;

elsif Sel = "11" then

Output1 <= Sig4;

else -- 'U', 'X', '-' etc.

Output1 <= (others => 'X');

end if;

end process;

-- Equivalent MUX using a case statement

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output2 <= Sig1;

when "01" =>

Output2 <= Sig2;

when "10" =>

Output2 <= Sig3;

when "11" =>

Output2 <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output2 <= (others => 'X');

end case;

end process;

end architecture;

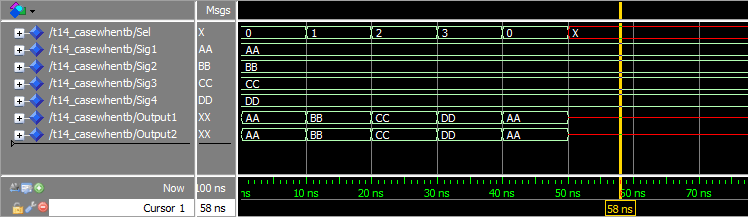

실행을 누르고 타임라인을 확대한 후 ModelSim의 파형 창:

ModelSim에서 실행 버튼을 눌렀을 때 시뮬레이터 콘솔에 대한 출력:

VSIM 2> run # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb

먼저 If-Then-Elsif-Else를 사용하여 Sig1 신호 중 하나를 전달하는 프로세스를 만들었습니다. , Sig2 , Sig3 , 또는 Sig4 , 선택기 신호 Sel의 값을 기반으로 합니다. .

그런 다음 Case-When 문을 사용하여 정확히 동일한 작업을 수행하는 프로세스를 만들었습니다. 두 프로세스의 출력 신호가 파형에서 알 수 있습니다. Output1 및 Output2 , 정확히 동일하게 행동합니다.

이 예에서 Sel signal에는 4개의 법적 값만 있습니다. 그러나 가능성이 더 많았다면 Case-When 문이 코드를 더 읽기 쉽게 만드는 데 도움이 될 수 있음을 쉽게 알 수 있습니다. 이것은 대부분의 VHDL 디자이너가 이러한 구성 요소를 만드는 데 선호하는 방법입니다.

멀티플렉서에 대한 이해 이 운동의 보너스 포인트였습니다. 멀티플렉서, 줄여서 MUX는 디지털 디자인의 핵심 구성 요소입니다. 단순히 여러 입력 중 하나를 선택하여 출력으로 전달하는 스위치입니다.

이것은 MUX가 선택한 입력 신호를 전달하는 방법을 보여줍니다.

others을 사용했습니다. Sel의 모든 값을 잡는 절 1도 0도 아닌 것. std_logic 튜토리얼에서 배웠듯이 이러한 신호는 '0'이 아닌 여러 값을 가질 수 있습니다. 또는 '1' . 'X'을 출력하여 이러한 값을 처리하는 것은 좋은 디자인 관행입니다. . 이것은 이 신호의 알 수 없는 값을 나타내며 다운스트림 로직에서도 볼 수 있습니다.

파형을 보면 Sel 신호가 빨간색으로 바뀌었습니다. Output1 및 Output2 또한 "XX"로 변경됨 . when others =>입니다. 실행 중입니다.

또한 ModelSim의 콘솔 출력은 Sel 때문에 경고를 표시합니다. 신호가 "UU"로 설정됨 . "** 경고:NUMERIC_STD."=":메타값이 감지되어 FALSE를 반환함" 메시지가 50ns 시뮬레이션 시간에 나타납니다. 이 메시지는 신호가 빨간색으로 변하는 정확한 시간입니다.

when others => 기본 선택을 구현하는 데 사용할 수 있습니다.다음 튜토리얼로 이동 »

VHDL

이전 자습서에서 For-Loop를 사용하여 정수 범위를 반복하는 방법을 배웠습니다. 그러나 고정된 정수 범위보다 루프를 더 자세히 제어하려면 어떻게 해야 할까요? 이를 위해 While 루프를 사용할 수 있습니다. While 루프는 테스트하는 표현식이 true로 평가되는 한 계속해서 동봉된 코드를 반복합니다. . 따라서 While-Loop는 얼마나 많은 반복이 필요한지 미리 알 수 없는 상황에 적합합니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. While 루프의 구문은 다음과 같습니다. while <

이전 튜토리얼에서 wait for를 사용하여 시간을 지연시키는 방법을 배웠습니다. 성명. 프로세스 루프에 대해서도 배웠습니다. 이제 허용하면 프로세스 스레드가 프로세스 내에서 영원히 반복된다는 것을 알고 있습니다. 그러나 프로세스의 시작 부분에서 한 번만 무언가를 하고 싶다면 어떻게 해야 할까요? 그런 다음 끝에 다른 코드를 반복합니까? VHDL에서 가장 단순한 종류의 루프는 loop을 사용하여 생성할 수 있습니다. 성명서. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. 단순 루프의 구문은 다음과 같습니다.