VHDL

펄스 폭 변조(PWM)는 순수 디지털 FPGA 핀에서 아날로그 전자 장치를 제어하는 효율적인 방법입니다. 아날로그 전압을 조절하는 대신 PWM은 아날로그 장치에 최대 전력으로 공급 전류를 빠르게 켜고 끕니다. 이 방법을 사용하면 소비자 기기에 제공되는 에너지의 이동 평균을 정밀하게 제어할 수 있습니다.

PWM의 좋은 후보가 되는 사용 사례의 예로는 오디오 변조(스피커), 광도 제어(램프 또는 LED) 및 유도 모터가 있습니다. 후자는 서보 모터, 컴퓨터 팬, 펌프, 전기 자동차용 브러시리스 DC 모터를 포함하며 그 목록은 계속됩니다.

참조:

FPGA 핀에서 PWM을 사용하는 RC 서보 컨트롤러

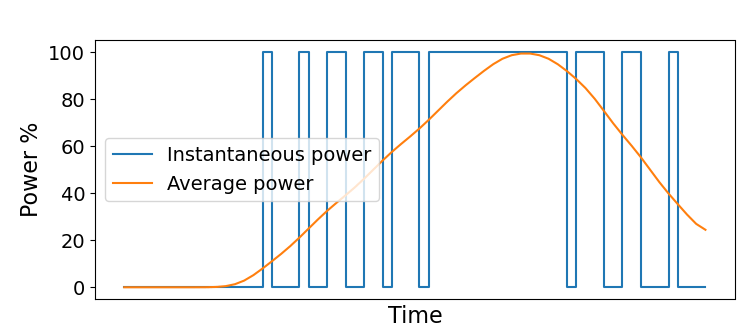

고주파 장치의 전원을 켜고 끄면 장치에 흐르는 평균 전류를 정확하게 제어할 수 있습니다. 아래 그림은 PWM 작동 방식의 기본 사항을 보여줍니다. PWM 출력은 전력을 100% 또는 0%로 설정할 수 있는 바이너리 스위치를 제어합니다. 두 극단 사이를 빠르게 번갈아 가며 슬라이딩 윈도우 평균은 각 상태에서 보낸 시간의 함수가 됩니다.

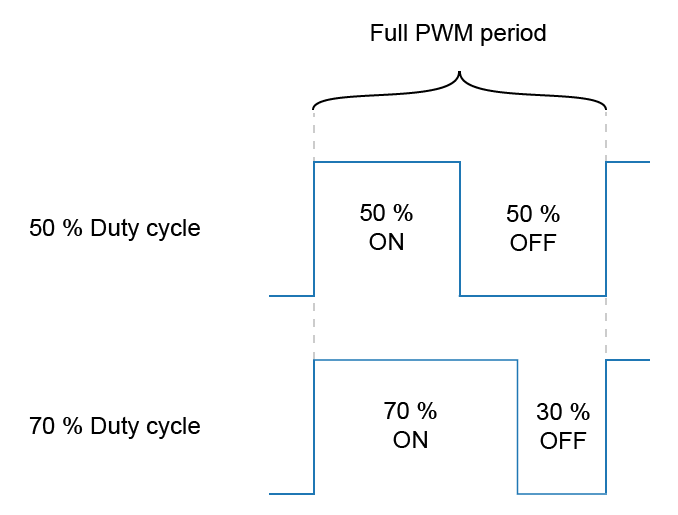

듀티 사이클은 PWM에서 아날로그 장치에 제공되는 전력을 제어하는 데 중요합니다. 듀티 사이클이라는 용어 PWM 출력이 ON 위치에서 소비하는 시간을 의미합니다. 아래 이미지와 같이 듀티 사이클을 백분율로 설명하는 것이 일반적입니다. 그러나 내 VHDL 예제에서는 이 기사 뒷부분에서 부호 없는 이진수를 사용할 것입니다. VHDL 구현에서 듀티 사이클의 전체 해상도를 나타낼 수 있는 이진수를 사용하는 것이 더 합리적입니다.

듀티 사이클이 0이면 PWM 출력은 계속해서 OFF 위치를 유지하고 100%에서는 ON 위치에서 논스톱으로 유지됩니다. PWM 컨트롤러가 페이로드 효과에 발휘할 수 있는 정확도의 정도는 PWM 카운터의 길이와 직접적인 관련이 있습니다. 이 기사 뒷부분에서 PWM 컨트롤러를 구현할 때 VHDL 코드에서 이것이 어떻게 작동하는지 살펴보겠습니다.

듀티 사이클의 이진 표현을 백분율로 변환하는 공식은 다음과 같습니다.

\mathit{duty\_cycle\_percentage} =\frac{\mathit{commanded\_duty\_cycle} * 100}{2^\mathit{pwm\_bits} - 1}PWM 스위칭 주파수에 대해 이야기할 때 우리는 PWM 출력이 ON과 OFF 상태 사이에서 얼마나 자주 교대하는지, PWM 카운터가 래핑되는 데 걸리는 시간을 의미합니다. 항상 그렇듯이 주파수는 전체 PWM 주기의 역수입니다.

\mathit{pwm\_freq} =\frac{1}{\mathit{pwm\_period}}이상적인 PWM 주파수는 제어하는 장치의 종류에 따라 다릅니다. 수백 헤르츠보다 큰 숫자는 소비자가 LED인 경우 육안으로 볼 때 안정적인 광원처럼 보일 것입니다. 브러시리스 DC 모터의 경우 스위트 스폿은 수십 킬로헤르츠 범위에 있습니다. 주파수를 너무 낮게 설정하면 물리적 진동이 발생할 수 있습니다. 너무 빠른 진동으로 전력을 낭비하게 됩니다.

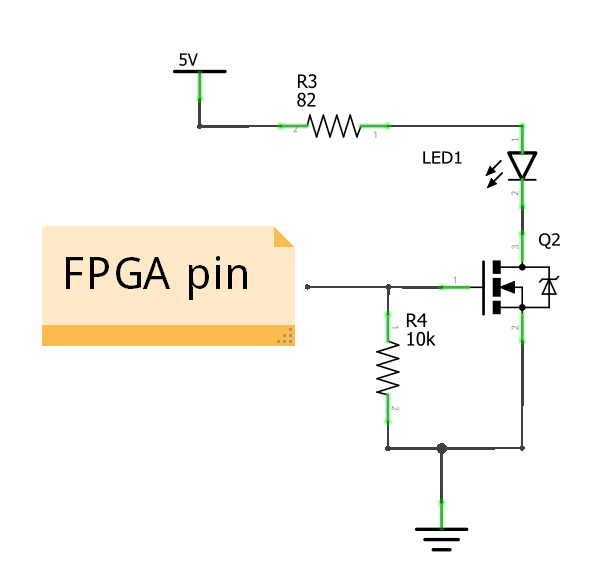

명심해야 할 문제는 아날로그 전력 전자 장치가 디지털 FPGA 핀만큼 빠르지 않다는 것입니다. 일반적인 PWM 설정은 전력 MOSFET을 스위치로 사용하여 아날로그 장치를 통해 흐르는 전류를 제어합니다.

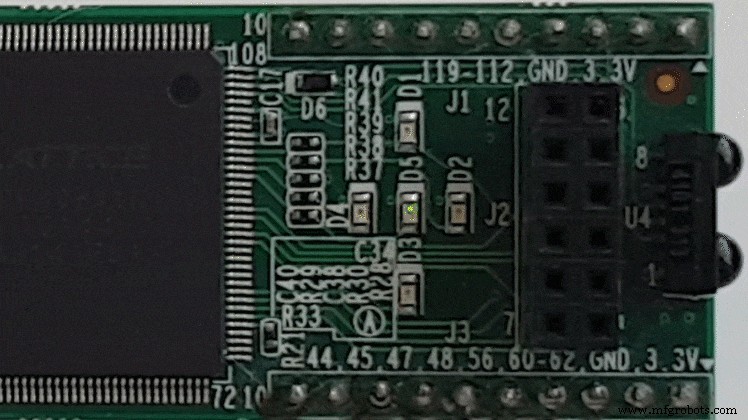

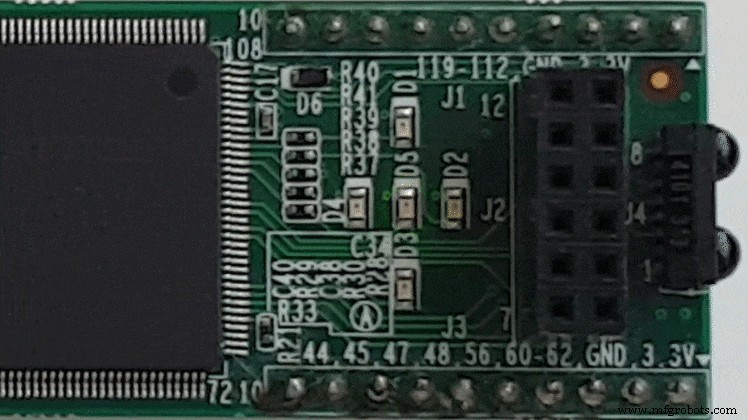

이미지에 표시된 회로도를 고려하십시오. 고급 Dot Matrix VHDL 과정에서 사용되는 LED 드라이버 회로의 일부입니다. FPGA 핀은 MOSFET의 게이트를 제어하여 직렬 LED에 대한 회로 차단기 역할을 합니다. 스위칭 주파수가 높을수록 트랜지스터는 완전히 열리지 않거나 완전히 닫히지 않은 상태에서 더 많은 시간을 소비합니다. 이는 MOSFET에서 낭비되는 전력과 과도한 열 생성으로 해석됩니다.

VHDL에서 PWM 컨트롤러의 표준적이고 일반적인 구현을 만들어 보겠습니다. 표준이 의미하는 것 이것은 VHDL로 PWM 컨트롤러를 작성하도록 요청하는 경우 대부분의 숙련된 VHDL 설계자가 생성하는 것과 유사하다는 것입니다. 일반입니다. PWM 주파수는 대부분의 애플리케이션에 맞게 사용자 정의할 수 있습니다.

실제 FPGA에서 PWM 생성기를 테스트하려면 PWM 컨트롤러 외에 몇 가지 모듈이 더 필요합니다. 나중에 PWM 모듈을 사용하여 Lattice iCEstick FPGA 개발 보드에서 LED 조명을 제어할 때 이를 설명하겠습니다. 하지만 먼저 PWM 제너레이터 모듈에 대해 이야기합시다.

모듈을 사용자 정의할 수 있도록 인스턴스화 시 두 개의 상수를 지정할 수 있는 일반 포트를 추가했습니다.

첫 번째 이름은 pwm_bits입니다. , 내부 PWM 카운터의 길이를 결정합니다. 이 상수는 최대 카운터 값이 아닌 비트 길이를 설정합니다. PWM 주파수를 특정 수의 클록 주기로 지정할 수 없습니다. 그러나 일반적으로 PWM 주파수를 100% 정확도로 설정할 필요는 없습니다. 이상적인 PWM 주파수는 하나의 정확한 숫자보다 잘 작동하는 범위입니다.

다른 일반 상수의 이름은 clk_cnt_len입니다. . PWM 주파수를 효과적으로 낮추는 두 번째 카운터의 길이를 지정합니다. 클럭 분배기 역할을 하지만 실제로 파생된 클럭 신호를 생성하지 않습니다. 기본값 1이 할당되어 있습니다. 이 상수를 1로 설정하면 클록 분배기가 비활성화되고 이를 처리하는 추가 논리도 제거됩니다.

이에 대해 설명하고 기사 뒷부분에서 정확한 PWM 주파수를 계산하는 공식을 제시하겠습니다.

entity pwm is

generic (

pwm_bits : integer;

clk_cnt_len : positive := 1

);

port (

clk : in std_logic;

rst : in std_logic;

duty_cycle : in unsigned(pwm_bits - 1 downto 0);

pwm_out : out std_logic

);

end pwm;

이것은 완전히 동기식 모듈이기 때문에 처음 두 신호는 클럭과 리셋입니다.

포트 선언 목록의 세 번째 입력은 듀티 사이클입니다. 위의 VHDL 코드에서 볼 수 있듯이 duty_cycle의 길이는 신호는 pwm_bits를 따릅니다. 일반 상수. 즉, pwm_bits 상수는 아날로그 장치에 대한 전력을 얼마나 정확하게 조절할 수 있는지를 결정합니다.

엔티티의 최종 신호는 pwm_out입니다. . 이것이 PWM 변조 제어 신호이며 FPGA 핀으로 라우팅하고 MOSFET의 게이트에 연결합니다.

PWM 모듈에는 두 개의 내부 신호만 포함됩니다. 첫 번째는 duty_cycle과 동일한 PWM 카운터입니다. 입력. 후자와 마찬가지로 pwm_bits 상수는 또한 이 신호의 길이를 결정합니다.

signal pwm_cnt : unsigned(pwm_bits - 1 downto 0); signal clk_cnt : integer range 0 to clk_cnt_len - 1;

두 번째 내부 신호의 이름은 clk_cnt입니다. , 그리고 이름에서 알 수 있듯이 클럭 사이클을 계산하기 위한 것입니다. 정수형이며 clk_cnt_len을 설정하면 1로 설정하면 계산 범위는 (0 ~ 0)으로 평가됩니다. —숫자 0만.

시계 카운터를 구현하는 프로세스는 간단합니다. 모듈이 재설정되지 않은 경우 로직은 계속해서 클록 사이클을 계산하고 clk_cnt 정수를 담을 수 있습니다.

CLK_CNT_PROC : process(clk)

begin

if rising_edge(clk) then

if rst = '1' then

clk_cnt <= 0;

else

if clk_cnt < clk_cnt_len - 1 then

clk_cnt <= clk_cnt + 1;

else

clk_cnt <= 0;

end if;

end if;

end if;

end process;

clk_cnt_len에 기본값 1을 사용한 경우 일반적으로 이 과정은 합성 중에 증발해야 합니다. 0 < 1 - 1 때문에 내부 if 문은 항상 거짓입니다. 거짓입니다. clk_cnt 값 그러면 는 항상 0입니다. 대부분의 합성 도구는 이를 인식하고 전체 프로세스를 최적화합니다.

PWM 출력 신호를 설정하는 프로세스는 PWM 카운터도 제어합니다. 클럭 사이클 카운터가 0일 때 PWM 카운터를 증가시킵니다. 이것이 PWM 주파수 제한 메커니즘이 작동하는 방식입니다.

처음에는 if clk_cnt = 0 then만 작성하려고 했습니다. 9번 줄에 있지만 기본 clk_cnt_len을 사용할 때 합성 도구가 클록 카운터와 관련된 모든 논리를 제거하지 않는다는 것을 발견했습니다. 값 1. 그러나 clk_cnt_len 포함 if 문에서 트릭을 수행했습니다. clk_cnt_len 때문에 합성에 부정적인 영향을 미치지 않아야 합니다. 상수입니다. 합성 도구는 컴파일 시간에 그 값을 파악한 다음 프로세스의 내용이 중복되는지 여부를 결정할 수 있습니다.

PWM_PROC : process(clk)

begin

if rising_edge(clk) then

if rst = '1' then

pwm_cnt <= (others => '0');

pwm_out <= '0';

else

if clk_cnt_len = 1 or clk_cnt = 0 then

pwm_cnt <= pwm_cnt + 1;

pwm_out <= '0';

if pwm_cnt = unsigned(to_signed(-2, pwm_cnt'length)) then

pwm_cnt <= (others => '0');

end if;

if pwm_cnt < duty_cycle then

pwm_out <= '1';

end if;

end if;

end if;

end if;

end process;

clk_cnt_len일 때 1보다 크면 pwm_cnt signal은 clk_cnt 때 증가하는 자유 실행 카운터처럼 작동합니다. 0입니다. 서명되지 않은 유형으로 오버플로가 발생하면 자동으로 0으로 되돌아갑니다. 그러나 0으로 래핑하기 전에 가장 높은 값을 건너뛰는지 확인해야 합니다.

위 코드의 14행에서 카운터가 두 번째로 높은 값에 있는지 확인하고 있습니다. 그렇다면 이 시점에서 0으로 설정합니다. pwm_cnt 시간에 관계없이 작동하는 트릭을 사용하고 있습니다. 신호는. to_signed를 사용하여 함수에서 pwm_cnt와 같은 길이의 부호 있는 상수를 새로 만들고 있습니다. , 그러나 값이 -2입니다.

VHDL 및 일반적으로 컴퓨터에서 부호 있는 숫자 -2는 항상 일련의 1이고 가장 오른쪽 위치에 0이 있습니다. 그것은 부호 확장이 작동하는 방식 때문입니다. 이에 대한 자세한 내용은 이전 튜토리얼에서 읽어보세요:

VHDL에서 서명된 것과 서명되지 않은 것을 사용하는 방법

마지막으로 서명된 유형을 서명되지 않은 유형으로 캐스팅하여 pwm_cnt 보유할 수 있습니다.

라인 18에서 우리는 자유 실행 PWM 카운터가 듀티 사이클 입력보다 큰지 확인하고 있습니다. 그것이 사실이라면 우리는 듀티 사이클의 ON 기간에 있기 때문에 PWM 출력을 '1'로 설정합니다.

이것이 PWM 카운터를 두 번째로 높은 값에서 0으로 다시 래핑해야 하는 이유입니다. PWM 카운터가 듀티 사이클이 가질 수 있는 가장 높은 값에 도달할 수 있다면 듀티 사이클을 100%로 설정할 수 없습니다. pwm_cnt < duty_cycle 행은 pwm_cnt일 때 항상 거짓입니다. 최대값이었습니다.

중간 듀티 사이클 단계 외에 완전히 OFF 및 ON 상태를 나타내야 하기 때문에 의미가 있습니다. pwm_bits 는 2로 설정되어 있고 내가 의미하는 바를 알아보기 위한 정신 훈련으로 전체 계산 순서를 실행합니다!

\mathit{pwm\_hz} =\frac{\mathit{clk\_hz}}{(2^\mathit{pwm\_bits} - 1) * \mathit{clk\_cnt\_len}}이러한 사실을 고려하여 정확한 PWM 주파수를 계산하기 위해 위에 표시된 공식을 도출할 수 있습니다. 동안 clk_hz 는 FPGA 시스템 클록의 주파수이고 다른 두 변수는 일반 입력 상수입니다.

실제 하드웨어에서 PWM 모듈을 테스트하기 위해 Lattice iCEstick의 전원 켜짐 LED 조명을 조절하는 구현을 만들었습니다. 저는 VHDL Fast-Track 초급 과정과 고급 Dot Matrix FPGA 과정 모두에서 이 저렴한 FPGA 개발 보드를 사용하고 있습니다.

위의 이미지는 화살표로 표시된 전원 LED가 있는 USB 연결 가능 iCEstick의 전면을 보여줍니다. iCEstick에는 별 모양으로 배열된 5개의 LED가 있습니다. 전원이 켜진 LED는 녹색이고 다른 LED는 빨간색 빛을 방출합니다. iCEstick에는 각 LED에 대한 전용 FPGA 핀이 있습니다. 정확한 제어 핀 번호는 iCEstick 사용 설명서를 참조하세요.

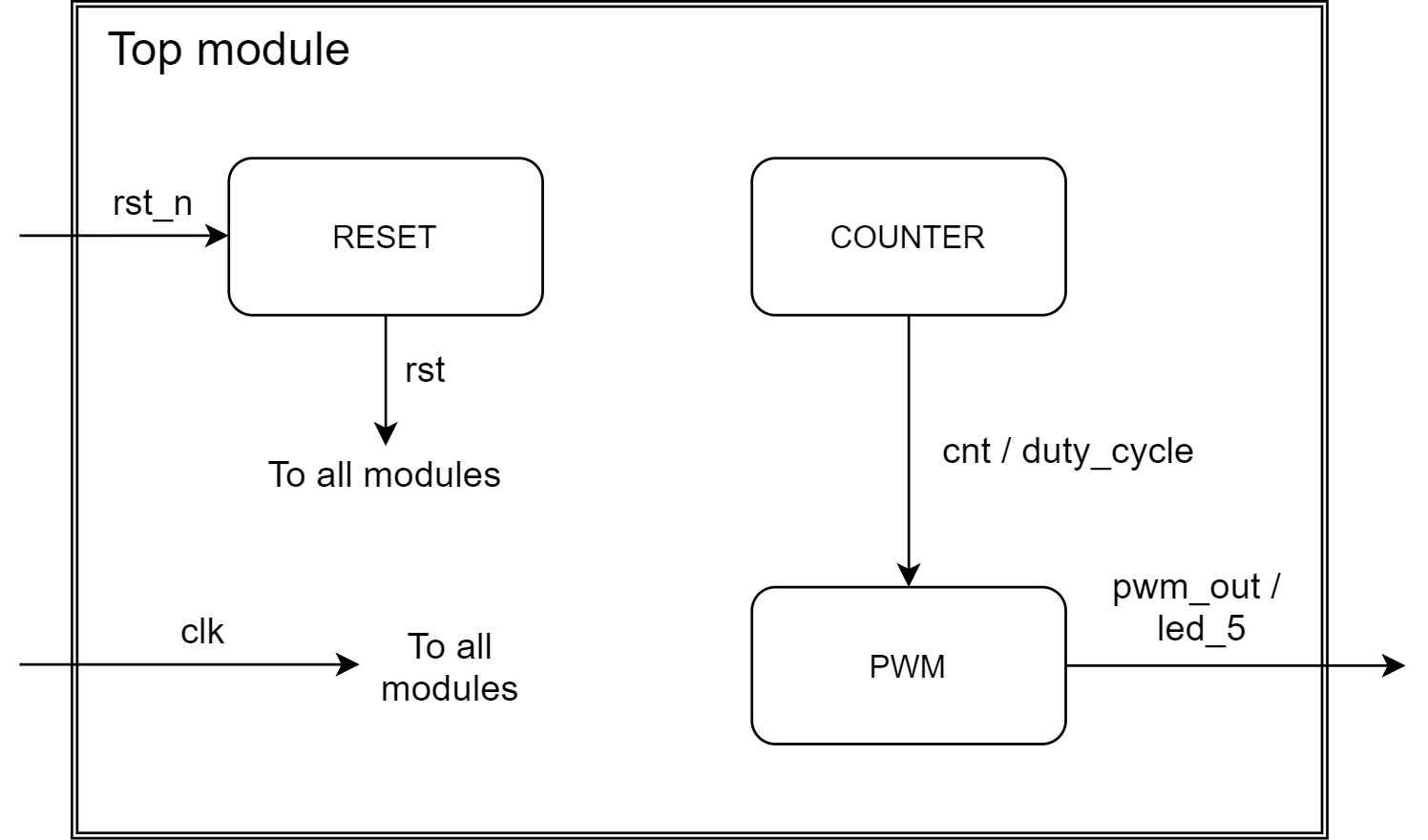

아래 다이어그램은 상위 모듈의 하위 모듈이 연결되는 방식을 보여줍니다. 우리는 이미 PWM 모듈에 대해 이야기했으며 이 기사 뒷부분에서 카운터 및 리셋 모듈에 대해 간략하게 설명하겠습니다.

최상위 모듈 내부에 상수를 하드코딩하는 대신 최상위 엔티티에서 제네릭으로 선언합니다. 그런 다음 iCEstick에 적합한 기본값을 할당합니다. 이 접근 방식의 한 가지 이점은 테스트벤치에서 이러한 값을 재정의하여 시뮬레이션 속도를 높일 수 있다는 것입니다. 디자인을 합성할 때 제네릭에 아무 것도 할당하지 않습니다. 따라서 올바른 기본값은 라우팅된 디자인에서 끝납니다.

pwm_bits를 전달합니다. 및 clk_cnt_len 동일한 이름을 가진 PWM 모듈 엔티티의 제네릭에. iCEstick 발진기의 클럭 주파수는 12Mhz입니다. 앞에서 제시된 공식을 사용하여 다음 값을 연결하여 PWM 주파수를 계산할 수 있습니다. \frac{12e6}{(2^8 - 1) * 47} \approx 1 \mathit{kHz}

entity pwm_led is

generic (

pwm_bits : integer := 8;

cnt_bits : integer := 25;

clk_cnt_len : positive := 47

);

port (

clk : in std_logic;

rst_n : in std_logic; -- Pullup

led_1 : out std_logic;

led_2 : out std_logic;

led_3 : out std_logic;

led_4 : out std_logic;

led_5 : out std_logic

);

end pwm_led;

세 번째 상수인 cnt_bits가 있다는 것을 눈치채셨을 것입니다. , 위 코드의 제네릭 선언에서. 셀프 랩핑 톱니 카운터의 길이를 제어합니다. 이 추가 카운터를 사용하여 전원이 켜진 LED의 점진적인 조명을 만들어 PWM 모듈이 실시간으로 작동하는 것을 관찰할 수 있습니다.

이 새로운 카운터의 상위 비트를 PWM 모듈의 듀티 사이클 입력에 연결합니다. 이 카운터는 클록 주기를 계산하므로 cnt_bits 일반은 전원 켜기 LED의 펄스 주파수를 결정합니다. 클럭 주파수와 카운터 길이의 함수인 공식은 다음과 같습니다.

\frac{2^{\mathit{cnt\_bits}}}{\mathit{clk\_hz}} =\frac{2^{25}}{12e6} \약 2.8 \mathit{Hz}포트 선언에서 재설정 입력을 _n으로 접미사로 붙였습니다. , 외부 리셋이 음의 극성을 가짐을 나타냅니다. 이 핀에서 내부 풀업 저항을 사용하도록 Lattice FPGA를 구성합니다.

마지막으로, 포트 선언에서 iCEstick에 있는 모든 LED를 나열한 것을 볼 수 있습니다. LED 번호 5만 사용하지만 다른 LED를 적극적으로 구동해야 합니다. 연결되지 않은 상태로 두면 희미한 빨간색으로 켜집니다.

VHDL 코드 및 제약 조건 파일을 자세히 살펴보고 싶다면 아래 양식에 이메일을 입력하세요. ModelSim 및 Lattice iCEcube2 프로젝트의 전체 코드가 포함된 Zip 파일을 받게 됩니다.

나는 RTL 로직이 없는 상위 모듈을 유지하는 것을 좋아합니다. 구조적 모듈이라는 개념입니다. . 제 경험상 RTL 로직과 인터커넥트를 분리할 때 구조화된 VHDL 프로젝트를 유지하는 것이 더 쉽습니다. 아래 코드는 상위 모듈의 신호 선언과 동시 신호 할당을 보여줍니다.

architecture str of pwm_led is signal rst : std_logic; signal cnt : unsigned(cnt_bits - 1 downto 0); signal pwm_out : std_logic; alias duty_cycle is cnt(cnt'high downto cnt'length - pwm_bits); begin led_1 <= '0'; led_2 <= '0'; led_3 <= '0'; led_4 <= '0'; led_5 <= pwm_out;

먼저 외부 리셋의 비반전 동기 버전이 될 리셋 신호를 선언합니다.

cnt라는 두 번째 선언된 신호 , 무한 래핑 클록 사이클 카운터입니다. 주어진 시간에 LED 강도 톱니파의 상태를 유지하는 unsigned 유형입니다.

다음은 pwm_out입니다. 신호. pwm_out을 연결할 수 있었습니다. PWM 모듈에서 led_5로 직접 신호 출력하지만 pwm_out을 관찰하고 싶었습니다. 시뮬레이터에서. 합성 도구는 두 신호가 동일한 네트에 속한다는 것을 알아낼 것입니다. 추가 리소스가 필요하지 않습니다.

마지막으로 duty_cycle 선언이 나옵니다. 벡터 - 이번에는 별칭을 사용했습니다. 새로운 신호를 생성하는 대신 키워드. VHDL 별칭은 C의 매크로처럼 작동합니다. duty_cycle을 사용할 때 이제부터 컴파일러는 cnt의 상위 비트를 대체합니다. 벡터.

시작 후 키워드로 pwm_out을 할당합니다. led_5에 신호 산출. 다른 모든 LED는 '0'으로 고정 배선되어 빨간색 빛이 켜지는 것을 방지합니다.

FPGA 내부의 외부 신호를 사용하기 전에 항상 내부 시스템 클록과 동기화해야 합니다. 그렇지 않으면 디버깅하기 어려운 준안정성 문제가 발생할 수 있습니다.

RESET : entity work.reset(rtl)

port map (

clk => clk,

rst_n => rst_n,

rst => rst

);

외부 리셋도 예외는 아니지만 최상위 구조 모듈에서 RTL 로직을 허용하지 않기 때문에 리셋 싱크로나이저를 독립형 모듈로 구현합니다.

다음 인스턴스화는 아래 코드 스니펫에 표시된 것처럼 PWM 모듈입니다. PWM 모듈 인스턴스화에서 duty_cycle을 사용하고 있습니다. cnt의 최상위 비트를 할당하기 위한 별칭 duty_cycle에 대한 벡터 입력. 그러면 카운터가 최대 값에 도달할 때까지 LED의 밝기가 강화됩니다. cnt일 때 다시 0으로 돌아가고 LED가 잠시 꺼지고 주기가 반복됩니다.

PWM : entity work.pwm(rtl)

generic map (

pwm_bits => pwm_bits,

clk_cnt_len => clk_cnt_len

)

port map (

clk => clk,

rst => rst,

duty_cycle => duty_cycle,

pwm_out => pwm_out

);

맨 위 모듈의 세 번째이자 마지막 인스턴스는 아래와 같이 클럭 주기 카운터입니다. 이 모듈을 보다 일반적으로 만들기 위해 count_enable 신호. 그러나 이 디자인에서는 모든 클록 주기를 계산하기 때문에 상수 '1'로 설정합니다.

COUNTER : entity work.counter(rtl)

generic map (

counter_bits => cnt'length

)

port map (

clk => clk,

rst => rst,

count_enable => '1',

counter => cnt

);

이 프로젝트에 대한 전체 VHDL 코드가 필요한 경우 아래 양식에 이메일 주소를 남겨주세요.

제네릭을 통해 카운터 길이를 사용자 정의할 수 있는 중요한 이점은 시뮬레이션 속도를 높일 수 있다는 것입니다. 대부분의 경우 로직에서 전환 및 이벤트를 테스트하는 데 관심이 있습니다. 우리는 디자인에서 아무 일도 일어나지 않는 동안 매우 긴 카운터를 통과하는 데 열중하지 않습니다.

제네릭을 사용하면 테스트벤치에서 비침습적인 방식으로 이러한 것들을 변경할 수 있습니다. 아래 코드는 테스트벤치에서 PWM 모듈을 인스턴스화할 때 일반 맵에 할당한 값을 보여줍니다.

DUT : entity work.pwm_led(str)

generic map (

pwm_bits => 8,

cnt_bits => 16,

clk_cnt_len => 1

)

ModelSim에서 이러한 상수를 사용하여 시뮬레이션할 때 100MHz에서 1400마이크로초 동안 실행하여 두 개의 전체 PWM 주기를 나타내면 충분합니다. 실제 값을 사용했다면 6초에 가까운 시뮬레이션을 해야 했습니다. 그것은 3,200만 클럭 사이클에 해당하는 것입니다. ModelSim에서는 영원히 걸릴 것입니다.

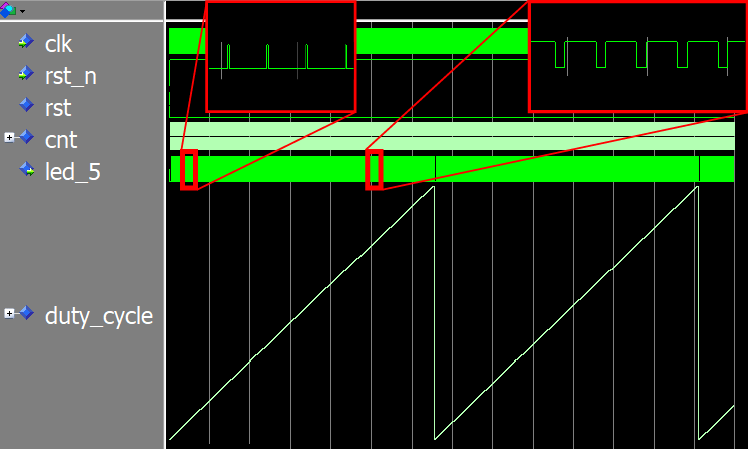

아래 이미지는 ModelSim에서 PWM 시뮬레이션의 파형을 보여줍니다. duty_cycle 형식을 변경했습니다. 기본 번호 유형에서 아날로그 웨이브 프레젠테이션으로 신호. 파형의 신호를 마우스 오른쪽 버튼으로 클릭하고 형식->아날로그(사용자 정의)…를 선택하여 ModelSim에서 이 작업을 수행할 수 있습니다. , 신호의 최소값 및 최대값과 일치하도록 픽셀 높이와 데이터 범위를 설정합니다.

파형에서 톱니파 신호라고 하는 이유를 알 수 있습니다. 자유롭게 움직이는 래핑 카운터는 톱날의 이빨과 비슷합니다.

PWM 출력의 높은 기간(led_5 ) 듀티 사이클이 증가함에 따라 증가합니다. led_5 톱니 끝에서 아주 짧게 연속 '1'입니다. 듀티 사이클이 최대값인 255일 때입니다.

PWM 모듈에 추가 if 문을 추가하지 않았다면 pwm_cnt 두 번째로 높은 값에서 다시 0으로 신호를 보내면 이것을 볼 수 없습니다. 우리는 최대 출력에 도달할 수 없습니다. PWM 생성기를 구현할 때 흔히 발생하는 오류입니다. 나도 한두 번 해봤다.

Lattice의 디자인 소프트웨어인 iCEcube2를 사용하여 Lattice iCEstick에 디자인을 구현했습니다. 아래 목록은 장소 및 경로 이후에 보고된 리소스 사용량을 보여줍니다. iCE40 FPGA는 작지만 PWM 및 지원 모듈은 사용 가능한 LUT의 5%만 사용합니다.

Resource Usage Report for pwm_led Mapping to part: ice40hx1ktq144 Cell usage: GND 3 uses SB_CARRY 31 uses SB_DFF 5 uses SB_DFFSR 39 uses SB_GB 1 use VCC 3 uses SB_LUT4 64 uses I/O ports: 7 I/O primitives: 7 SB_GB_IO 1 use SB_IO 6 uses I/O Register bits: 0 Register bits not including I/Os: 44 (3%) Total load per clock: pwm_led|clk: 1 @S |Mapping Summary: Total LUTs: 64 (5%)

iCEcube2에서 프로그래밍 비트스트림을 생성한 후 Lattice Diamond 독립형 프로그래머를 사용하여 USB를 통해 FPGA를 구성했습니다.

아래 GIF 애니메이션은 톱니파 듀티 사이클 신호가 iCEstick의 전원 켜기 LED가 어떻게 동작하는지 보여줍니다. cnt 카운터 랩. 그러면 듀티 사이클이 모두 0이 되고 LED가 잠시 꺼집니다. 그 후, 주기가 무한 반복됩니다.

iCEstick은 저렴하고 다재다능한 FPGA 개발 보드입니다. 초보자에게 좋지만 고급 임베디드 프로젝트에도 적합합니다. 또한 Lattice 소프트웨어는 복잡하지 않고 사용하기 쉽습니다. 그래서 초급 VHDL 과정과 고급 FPGA 과정에서 iCEstick을 사용하고 있습니다.

이미 iCEstick을 소유하고 있다면 아래 양식을 사용하여 iCEcube2 프로젝트를 다운로드할 수 있습니다.

이제 PWM을 사용하여 LED 조명을 제어하는 방법을 알게 되었습니다.

톱니파 패턴으로 맥동하는 LED는 단순한 ON/OFF 깜박임 응용 프로그램보다 틀림없이 더 시원합니다. 이것은 VHDL 학생들의 일반적인 첫 번째 작업이며, 어느 시점에서 LED를 깜박였을 것입니다.

그러나 사인파를 사용하여 듀티 사이클을 제어하면 LED 깜박임이 훨씬 더 인상적입니다. 아래 GIF 애니메이션은 시간에 따른 사인파 강도 변화로 LED를 펄스하는 PWM 모듈을 보여줍니다.

이전에 LED에서 이러한 종류의 "호흡" 효과를 본 적이 있을 것입니다. 제 휴대폰의 알림 LED가 이렇게 동작하고, 광량의 급격한 변화가 없어서 자연스럽게 보이는 것 같아요.

다음 블로그 게시물에서는 FPGA에서 블록 RAM을 사용하여 사인파 생성기를 만드는 방법을 보여 드리겠습니다. 그리고 pwm_led iCEstick의 LED를 사인파 강도로 펄스하는 모듈입니다.

다음 블로그 게시물로 이동하려면 여기를 클릭하십시오.

블록 RAM에 저장된 사인파를 사용하여 호흡 LED 효과를 만드는 방법

참조:

FPGA 핀에서 PWM을 사용하는 RC 서보 컨트롤러

VHDL

PID 또는 비례 적분 미분(PID) 컨트롤러는 압력, 유량, 기타 프로세스 변수 및 온도 제어에 사용됩니다. 비례 적분 미분 제어기의 목적은 피드백이 온도 설정을 기반으로 특정 설정점과 일치하도록 강제하는 것입니다. PID 온도 컨트롤러는 주로 프로세스에 추가된 에너지 변화에 빠르게 반응하는 시스템에서 많이 사용됩니다. 이는 일정한 부하 변화가 있는 시스템에서 매우 유용하며 약간 작은 질량으로 구성됩니다. 요컨대, PID 컨트롤러는 설정값을 확인한 후 온도를 원하는 설정값으로 변환하는 장치입니다. 그렇다면 PID 온도 컨트롤러를

3D 프린팅에는 항상 사용자에 따라 달라지는 일련의 요소가 있습니다. , 인쇄가 만족스럽거나 실패하는 경우가 많습니다. 각 사용자가 각 3D 프린트에서 사용하는 프린트 프로필에 모든 요소가 수집됩니다. 3D FDM 인쇄 프로필에서 무한한 수의 매개변수를 수정할 수 있습니다. :프린팅 온도 및 속도, 내부 및 외부 부품 제조 방법 및 3D 프린팅에 영향을 미치는 나머지 모든 매개변수. 이러한 이유로 가장 중요한 정보는 인쇄 프로필을 만들 때 아래에서 설명합니다. 고려할 측면 인쇄 매개변수를 수정하기 전에 직접적으로 영향을 미치