VHDL

시뮬레이션이 완료되면 VHDL 시뮬레이터를 어떻게 중지합니까? 여러 가지 방법이 있습니다. 이 기사에서는 성공적인 테스트벤치 실행을 종료하는 가장 일반적인 방법을 살펴보겠습니다.

여기에 제시된 VHDL 코드는 보편적이며 가능한 모든 VHDL 시뮬레이터에서 작동해야 합니다. Tcl과 관련된 방법의 경우 ModelSim 및 Vivado 시뮬레이터에 대한 명령을 나열하겠습니다.

ModelSim이 설치된 경우 이 기사에서 4개의 다른 테스트벤치가 있는 예제 프로젝트를 다운로드할 수 있습니다. Zip 파일을 받으려면 아래 양식에 이메일 주소를 입력하십시오!

VHDL 마감 절차는 오류 없이 완료되는 VHDL 테스트벤치를 중지하는 가장 좋아하는 방법입니다. STD.ENV 패키지에서 "finish"를 가져와야 하고 테스트벤치를 VHDL-2008 이상으로 컴파일해야 사용이 가능합니다.

아래 코드는 테스트벤치 시퀀서 프로세스의 마지막 라인에 도달하면 시뮬레이션을 종료합니다.

use std.env.finish; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'finish'"; finish; end process;

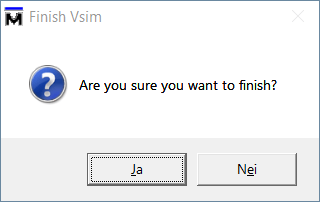

참고 마침 기본적으로 시뮬레이션을 종료합니다. GUI 버전에서 ModelSim을 실행 중인 경우 "종료하시겠습니까?"라는 팝업이 나타납니다. 예를 클릭하면 ModelSim이 종료됩니다.

그것은 아마도 당신이 원하는 것이 아닙니다. 다행히도 아래와 같이 vsim 명령에 "-onfinish stop" 옵션을 추가하여 이 동작을 방지할 수 있습니다. 이렇게 하면 마침 절차는 중지와 같은 방식으로 작동합니다. 이 문서의 다음 섹션에서 논의할 절차입니다.

vsim -onfinish stop work.using_finish_tb

마감 사용의 이점 배치 모드에서 시뮬레이션할 때 기본 동작을 사용할 수 있다는 것입니다. 스크립트를 사용하여 시뮬레이션을 시작하는 경우 시뮬레이션이 완료된 후 호출 스크립트에 제어를 반환하려고 합니다.

아래 예는 마감을 사용하는 테스트벤치를 보여줍니다. Linux의 ModelSim 배치 모드에서 시작된 절차. 테스트벤치가 완료되면 시뮬레이터가 종료되고 마지막 줄에서 Linux 셸로 돌아갑니다.

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_finish_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_finish_tb # vsim work.using_finish_tb # Start time: 22:58:31 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_finish_tb(sim) # run -all # ** Note: Calling 'finish' # Time: 1 ms Iteration: 0 Instance: /using_finish_tb # End time: 22:58:31 on Jun 21,2020, Elapsed time: 0:00:00 # Errors: 0, Warnings: 8 jonas@ubuntu:~/stop_tb$

VHDL 마감 절차는 표준 ENV 패키지에 정의되어 있습니다. 아래 코드에서 볼 수 있듯이 두 가지 오버로드된 특징이 있습니다. 매개변수가 없는 버전이 있는데 제가 항상 사용하는 버전과 상태 정수를 상수 입력으로 사용하는 버전이 있습니다.

procedure FINISH (STATUS: INTEGER); procedure FINISH;

Linux 셸에서 호출하면 상태 정수가 종료 코드가 된다고 생각할 수 있지만 적어도 ModelSim에서는 그렇지 않습니다. 이 상태 코드를 사용할 때의 문제는 수행하는 작업이 시뮬레이터에 따라 다르다는 것입니다. VHDL-2008 표준의 문구는 "STATUS 매개변수의 값은 호스트 시뮬레이터에 의해 정의된 방식으로 구현에 사용될 수 있음입니다. ".

그러나 Tcl 명령 exit -code <value>을 사용하여 ModelSim에서 Linux 종료 코드 값을 제어할 수 있습니다. 하지만 그건 또 다른 이야기입니다.

VHDL 중지 절차로 인해 시뮬레이션이 일시 중지됩니다. 신호 값을 수동으로 검사하거나 나중에 시뮬레이션을 계속하려는 경우 유용할 수 있습니다. 시뮬레이터는 이를 중단점처럼 취급합니다.

아래 예는 stop을 가져오고 사용하는 방법을 보여줍니다. 절차.

use std.env.stop; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'stop'"; stop; end process;

stop 사용 문제 스크립트 기반 설정에서는 시뮬레이션을 종료하지 않습니다. 호출자에게 제어권을 반환하는 대신 ModelSim은 Tcl 명령 셸을 열어 호출 스크립트를 무기한 중단합니다.

아래 목록은 stop을 사용하는 테스트벤치를 실행한 결과를 보여줍니다. 배치 모드의 절차. 시뮬레이션이 중지된 후에도 여전히 ModelSim에 있습니다. Tcl 쉘에서 나가려면 "exit"를 입력해야 합니다.

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_stop_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_stop_tb # vsim work.using_stop_tb # Start time: 22:58:56 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_stop_tb(sim) # run -all # ** Note: Calling 'stop' # Time: 1 ms Iteration: 0 Instance: /using_stop_tb # Break in Process SEQUENCER_PROC at ~/stop_tb/src/using_stop_tb.vhd line 23 # Stopped at ~/stop_tb/src/using_stop_tb.vhd line 23 VSIM 3>

마무리처럼 절차, 중지 VHDL-2008 이상이 필요합니다. 아래와 같이 프로시저의 오버로드된 버전이 존재합니다. 정수 상태 값을 취하지만 시뮬레이터마다 동작이 다릅니다.

procedure STOP (STATUS: INTEGER); procedure STOP;

VHDL 테스트벤치를 중지하는 안전하고 보편적인 방법은 어설션 실패를 생성하는 것입니다. 그것이 내가 대학에서 VHDL을 배울 때 누군가가 시뮬레이션 종료를 가르쳐준 첫 번째 방법이었습니다.

추가 가져오기가 필요하지 않으며 모든 VHDL 버전에서 작동합니다. 심각도 수준 실패를 사용해야 합니다. , 아래 예와 같이.

SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; assert false report "Test: OK" severity failure; end process;

그리고 성공적인 시뮬레이션을 중단하는 이러한 방식이 싫은 이유는 무엇입니까?

우선 위의 예에서 출력된 내용을 보면 이상하고 혼란스러워 보입니다.

# ** Failure: Test: OK

그것은 "실패"라고 말하지만 테스트는 동시에 "OK"입니다. 그 이유는 주장 명령문은 시뮬레이션의 성공적인 완료가 아니라 오류 조건을 표시해야 합니다.

내가 생각할 수 있는 또 다른 성가신 문제는 시뮬레이션이 성공했는지 프로그래밍 방식으로 찾기가 어려워진다는 것입니다.

대부분의 VHDL 전문가는 예를 들어 대규모 회귀 테스트 계획의 일부로 스크립트에서 시뮬레이션을 시작합니다. 테스트벤치도 아무 문제가 없는데 assertion 실패에서 멈추면 이를 VHDL 모듈의 상태를 결정하는 마커로 사용할 수 없습니다.

내가 다룰 시뮬레이션을 중지하는 마지막 방법은 Tcl을 VHDL과 함께 사용하는 것입니다. VHDL 파일에서 테스트벤치를 중지하는 대신 중지할 시간이 되면 일반 VHDL 신호를 설정합니다. 그리고 미리 이 트리거 신호의 변경 사항을 수신하도록 시뮬레이터를 구성합니다.

또한 읽기:

Tcl을 배워야 하는 이유

stop_condition이라는 신호를 설정하는 아래 예를 보십시오. 모든 테스트 케이스가 완료되었을 때.

signal stop_condition : boolean;

begin

-- Replace this line with your DUT instantiation

stop_condition <= not stop_condition after 1 ms;

SEQUENCER_PROC : process

begin

-- Put your testbench logic here

-- Pause this process forever after all tests are done

wait;

end process;

한 번의 대기로 작업을 완료한 테스트벤치 프로세스를 절전 모드로 전환할 수 있습니다. 프로세스 종료 전의 문 꼬리표. 그러면 다시 시작되지 않습니다. 실제로 시뮬레이션을 중지하기 위한 Tcl 코드는 시뮬레이터마다 다릅니다.

우리가 원하는 것은 stop_condition VHDL 신호가 true가 됩니다. . VHDL 테스트벤치를 실행하기 전에 Tcl에서 콜백을 설정하면 됩니다.

ModelSim 명령 참조 설명서에 따르면 Tcl when을 사용하여 이를 달성할 수 있습니다. 명령. 아래 Tcl 코드에서 이러한 콜백을 등록한 다음 run -all을 사용하여 시뮬레이터를 시작합니다. .

when {stop_condition} {

stop

echo "Test: OK"

}

run -all

중괄호 안의 코드는 콜백이 발생할 때까지 실행되지 않습니다. VHDL 코드가 stop_condition을 변경할 때 true 신호 , 시뮬레이터는 두 줄을 일시 중지하고 실행합니다. 예제에서는 시뮬레이션을 중지하고 콘솔에 "Test:OK"를 인쇄합니다. Tcl exit도 있을 수 있습니다. VHDL 마침과 같이 시뮬레이터를 종료하는 명령 절차.

# vsim # Start time: 22:31:11 on Jun 22,2020 # Loading std.standard # Loading work.using_tcl_tb(sim) # Test: OK # Simulation stop requested.

위의 목록은 Tcl / VHDL 테스트벤치가 완료될 때 ModelSim 콘솔에 출력되는 출력을 보여줍니다. 컴퓨터에서 시도하려면 아래 양식을 사용하여 이 기사의 모든 예제가 포함된 ModelSim 프로젝트를 다운로드하십시오!

Vivado Design Suite Tcl Command Reference Guide에 따르면 add_condition을 사용하여 Tcl 콜백을 등록할 수 있습니다. 명령. 아래 코드는 이전에 논의된 ModelSim 버전에 해당하는 Xilinx를 보여줍니다.

set sim_fileset sim_1

launch_simulation -simset [get_filesets $sim_fileset]

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

run all

-notrace switch는 콜백 함수의 코드 라인이 실행될 때 터미널에 에코되는 것을 방지합니다. 콘솔에 불필요한 것을 더 많이 두지 않는 것이 좋습니다.

아래 목록은 Vivado 시뮬레이터 콘솔에서 실행 중인 시뮬레이션에서 발췌한 내용을 보여줍니다.

launch_simulation: ...

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

condition8

run all

Test: OK

지금까지 살펴본 것처럼 VHDL 시뮬레이션을 종료하는 방법에는 여러 가지가 있습니다. 그러나 내가 사용하는 유일한 것은 VHDL-2008 마감입니다. 절차.

현재 모든 시뮬레이터는 VHDL-2008을 지원하며 2008년에는 RTL 코드를 컴파일할 필요가 없고 테스트벤치만 있으면 됩니다. 마침 절차는 가장 이식 가능한 방법이며 GUI 모드에서 실행할 때 시뮬레이터를 중지하거나 배치 모드에서 실행할 때 종료할 수 있습니다. 내가 대부분의 시간에 정확히 원하는 동작입니다.

그러나 이 기사의 범위를 벗어나는 Tcl 방법의 장점이 있습니다. Tcl 콜백에서 시뮬레이터를 일시 중지하면 시뮬레이터를 중지하고 종료하는 것 이상의 작업을 수행할 수 있습니다. 콜백에 있는 동안 VHDL 신호를 검사하고 Tcl을 사용하여 조작할 수도 있습니다. Tcl을 사용한 확인입니다.

VHDL

이전 자습서에서 For-Loop를 사용하여 정수 범위를 반복하는 방법을 배웠습니다. 그러나 고정된 정수 범위보다 루프를 더 자세히 제어하려면 어떻게 해야 할까요? 이를 위해 While 루프를 사용할 수 있습니다. While 루프는 테스트하는 표현식이 true로 평가되는 한 계속해서 동봉된 코드를 반복합니다. . 따라서 While-Loop는 얼마나 많은 반복이 필요한지 미리 알 수 없는 상황에 적합합니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. While 루프의 구문은 다음과 같습니다. while <

이전 튜토리얼에서 wait for를 사용하여 시간을 지연시키는 방법을 배웠습니다. 성명. 프로세스 루프에 대해서도 배웠습니다. 이제 허용하면 프로세스 스레드가 프로세스 내에서 영원히 반복된다는 것을 알고 있습니다. 그러나 프로세스의 시작 부분에서 한 번만 무언가를 하고 싶다면 어떻게 해야 할까요? 그런 다음 끝에 다른 코드를 반복합니까? VHDL에서 가장 단순한 종류의 루프는 loop을 사용하여 생성할 수 있습니다. 성명서. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. 단순 루프의 구문은 다음과 같습니다.