VHDL

VHDL에는 의사 난수 생성기가 내장되어 있지만 0과 1 사이의 부동 소수점 수만 생성할 수 있습니다. 다행히도 이로부터 필요한 다른 임의의 데이터 형식을 파생할 수 있습니다. 이 기사를 계속 읽고 real를 생성하는 방법을 알아보세요. 또는 integer 임의의 std_logic_vector 뿐만 아니라 모든 범위의 값 시퀀스 및 time 가치.

uniform IEEE MATH_REAL 패키지의 절차는 이 기사에서 설명하는 알고리즘의 기초입니다. uniform 난수를 생성하는 소프트웨어에 의존합니다. 따라서 이러한 알고리즘 중 어느 것도 합성할 수 없습니다. 테스트벤치에서만 사용할 수 있습니다.

procedure UNIFORM(variable SEED1, SEED2 : inout POSITIVE;

variable X : out REAL);

위의 목록은 uniform의 프로토타입을 보여줍니다. 절차. 작동하려면 두 개의 시드 변수가 필요하며 프로시저를 호출할 때마다 수정됩니다. 출력 X는 항상 0과 1 사이의 값을 갖는 난수입니다.

다른 의사 난수 생성기와 마찬가지로 uniform 동일한 초기 시드 값으로 호출될 때 동일한 숫자 시퀀스를 생성합니다. 이 동작으로 인해 테스트 벤치를 다시 실행하고 동일한 seed 값을 사용할 때 동일한 결과를 얻을 수 있습니다.

이 알고리즘의 작동 방식에 대한 자세한 설명은 Pierre L'Ecuyer의 Efficient and Portable Combined Random Number Generators 문서를 참조하십시오. GHDL 오픈 소스 VHDL 시뮬레이터에서 알고리즘의 실제 구현을 볼 수도 있습니다.

이 문서의 모든 예제에서는 두 시드에 대해 값 999를 사용합니다. 프로세스의 선언적 영역에서 아래와 같이 시드 변수를 선언합니다. 그런 다음 동일한 프로세스 내에서 순수하지 않은 함수로 사용자 지정 무작위 알고리즘을 구현합니다.

variable seed1, seed2 : integer := 999;

아래 양식을 사용하여 이 기사의 모든 예제가 포함된 완전한 테스트벤치를 다운로드할 수 있습니다. Zip 파일에는 시뮬레이션을 컴파일하고 실행하는 스크립트가 포함된 ModelSim 프로젝트도 포함되어 있습니다.

uniform 프로시저는 임의의 real를 생성합니다. 0.0과 1.0 사이의 값. real type은 VHDL의 부동 소수점 형식입니다. 그러나 난수가 다른 범위에 있기를 원할 가능성이 있습니다.

impure function rand_real(min_val, max_val : real) return real is variable r : real; begin uniform(seed1, seed2, r); return r * (max_val - min_val) + min_val; end function;

다행히도 uniform의 출력을 쉽게 번역할 수 있습니다. 스케일을 곱하고 오프셋을 추가합니다. 위의 코드는 임의의 real을 반환하는 함수를 보여줍니다. 최소/최대 범위 내의 값입니다.

임의의 integer를 생성하려면 지정된 범위 내에서 값을 얻으려면 눈금을 곱하고 오프셋을 추가해야 합니다. 그러나 피해야 할 함정이 있습니다. 단순히 임의의 real를 생성할 수 없습니다. 범위 내에서 값을 반환하고 integer으로 반올림 .

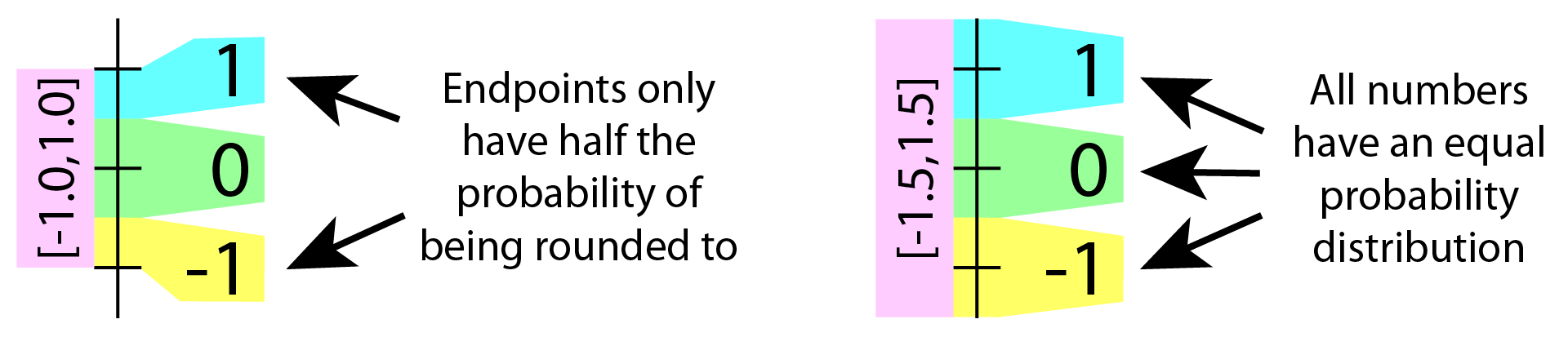

위의 그림은 문제를 보여줍니다. 이 예에서는 임의의 integer을 생성하려고 합니다. -1에서 1 사이의 값입니다. integer을 기반으로 하는 경우 임의의 real에서 정확히 끝점으로 이동하면 최소 및 최대 정수가 선택될 확률의 절반만 얻습니다. 0 integer로 반올림 3개의 숫자 선택이 있더라도 가치는 절반으로 발생합니다.

impure function rand_int(min_val, max_val : integer) return integer is

variable r : real;

begin

uniform(seed1, seed2, r);

return integer(

round(r * real(max_val - min_val + 1) + real(min_val) - 0.5));

end function;

위의 코드에서 임의의 real를 조정하여 끝점 반올림 문제를 수정합니다. 끝점 위와 아래에 추가로 0.5를 포함하는 값입니다.

임의의 값으로 벡터를 채우는 방법에는 여러 가지가 있지만 이 방법은 모든 길이의 벡터에서 작동합니다. 저는 for 루프를 사용하여 벡터를 탐색하고 모든 비트에 대해 임의의 값을 선택합니다. 아래 코드에서 len 매개변수는 임의의 std_logic_vector 길이를 결정합니다. 반환합니다.

impure function rand_slv(len : integer) return std_logic_vector is

variable r : real;

variable slv : std_logic_vector(len - 1 downto 0);

begin

for i in slv'range loop

uniform(seed1, seed2, r);

slv(i) := '1' when r > 0.5 else '0';

end loop;

return slv;

end function;

때때로 임의의 time를 생성해야 합니다. 테스트 벤치의 가치. 무작위로 데이터 버스트를 기록하는 외부 인터페이스를 시뮬레이션하고 싶을 수 있습니다. 이유가 무엇이든 임의의 time 값을 생성하기 쉽습니다.

impure function rand_time(min_val, max_val : time; unit : time := ns) return time is variable r, r_scaled, min_real, max_real : real; begin uniform(seed1, seed2, r); min_real := real(min_val / unit); max_real := real(max_val / unit); r_scaled := r * (max_real - min_real) + min_real; return real(r_scaled) * unit; end function;

임의의 time을 생성하려면 VHDL의 값을 사용하려면 먼저 원하는 최소값과 최대값을 real으로 변환해야 합니다. 유형. 그런 다음 임의화 공식이 마법을 수행한 후 결과를 다시 VHDL time으로 변환합니다. 유형. 위의 코드와 같이 시뮬레이터에서 사용하는 시뮬레이션 시간 단위를 이 함수에 대한 인수로 지정해야 합니다.

마지막으로 무작위화 알고리즘을 손으로 만드는 대신 OSVVM 라이브러리에서 Random 패키지를 사용할 수 있습니다. 모든 종류의 VHDL 유형에 대해 임의 값을 생성하기 위한 여러 오버로드된 기능이 있습니다.

OSVVM(Open Source VHDL Verification Methodology)은 구조화된 테스트벤치를 만들기 위한 VHDL 라이브러리입니다. Random 패키지는 이 라이브러리에 있는 많은 유용한 패키지 중 하나일 뿐입니다.

library osvvm; use osvvm.RandomPkg.all;

위의 코드는 OSVVM 패키지를 가져오는 방법을 보여줍니다. ModelSim에는 기본 제공되는 라이브러리가 포함되어 있으므로 이 시뮬레이터용으로 다운로드할 필요가 없습니다. OSVVM GitHub 리포지토리에서 RandomPck.vhd 파일을 참조하여 필요에 적합한 무작위화 기능을 찾으십시오.

VHDL

이전 자습서에서 For-Loop를 사용하여 정수 범위를 반복하는 방법을 배웠습니다. 그러나 고정된 정수 범위보다 루프를 더 자세히 제어하려면 어떻게 해야 할까요? 이를 위해 While 루프를 사용할 수 있습니다. While 루프는 테스트하는 표현식이 true로 평가되는 한 계속해서 동봉된 코드를 반복합니다. . 따라서 While-Loop는 얼마나 많은 반복이 필요한지 미리 알 수 없는 상황에 적합합니다. 이 블로그 게시물은 기본 VHDL 자습서 시리즈의 일부입니다. While 루프의 구문은 다음과 같습니다. while <

이전 튜토리얼에서 우리는 프로세스를 프로그램 스레드로 생각할 수 있다는 것을 배웠습니다. 또한 wait; 문으로 인해 프로그램이 무기한 일시 중지됩니다. 하지만 프로그램이 영원히가 아닌 다른 시간 값을 기다리게 하는 방법이 있습니까? wait;을 제거하면 프로그램을 컴파일하려고 하면 컴파일러는 무한 루프에 대해 불평할 것입니다. 컴파일러가 참조하는 루프는 프로세스 루프입니다. . VHDL의 프로세스 스레드는 절대 종료되지 않으며 begin 사이에서 계속 반복됩니다. 및 end process; 진술. wait이 있어야 합니다. 프로