임베디드

제어 장치는 프로세서/컴퓨터가 프로그램을 실행하는 동안 작업을 지시할 수 있는 컴퓨터의 중앙 처리 장치(CPU)의 주요 구성 요소입니다. 제어 장치의 주요 기능은 컴퓨터의 메모리에서 명령을 가져와 실행하는 것입니다. 사용자로부터 입력 명령/정보를 수신하고 이를 제어 신호로 변환한 다음 추가 실행을 위해 CPU에 제공합니다. John Neumann이 개발한 Von Neumann 아키텍처의 일부로 포함되어 있습니다. 타이밍 신호와 제어 신호를 제공하고 CPU에 의한 프로그램 실행을 지시하는 역할을 합니다. 그것은 현대 컴퓨터에서 CPU의 내부 부품으로 포함됩니다. 이 문서에서는 제어 장치에 대한 전체 정보를 설명합니다.

사용자로부터 입력 신호/정보/명령을 받아 CPU에서 실행을 위한 제어 신호로 변환하는 구성 요소. 메인 메모리, 산술 및 논리 장치(ALU), 입력 및 출력 장치를 제어하고 지시하며 컴퓨터의 CPU로 전송되는 명령도 담당합니다. 프로세서의 주 메모리에서 명령어를 가져와 레지스터 내용을 포함하는 프로세서 명령어 레지스터로 보냅니다.

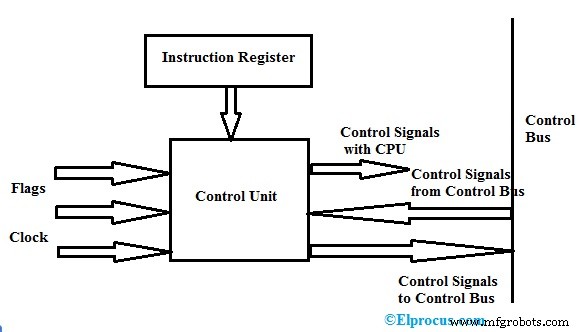

제어 장치는 입력을 제어 신호로 변환한 다음 프로세서로 보내 프로그램 실행을 지시합니다. 수행해야 하는 작업은 컴퓨터의 프로세서에서 지시합니다. 주로 중앙 처리 장치(CPU)와 그래픽 처리 장치(GPU)는 내부 부품으로 제어 장치가 필요합니다. 컨트롤 유닛의 블록도는 위와 같습니다.

이 장치의 구성 요소는 명령 레지스터, CPU 내의 제어 신호, 버스로/로부터의 제어 신호, 제어 버스, 입력 플래그 및 클럭 신호입니다.

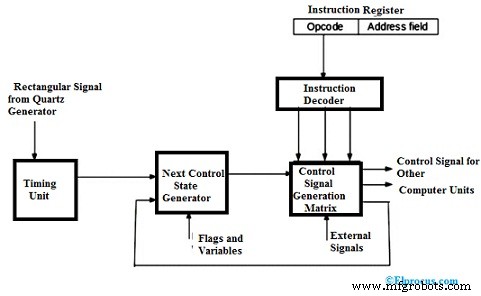

Hardwired 제어 장치의 구성 요소는 명령 레지스터(opcode 및 주소 필드 포함), 타이밍 장치, 제어 상태 생성기, 제어 신호 생성 매트릭스 및 명령 디코더입니다.

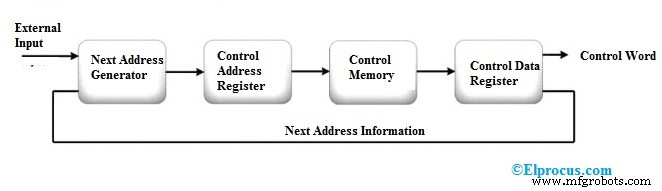

마이크로 프로그래밍된 제어 장치의 구성 요소는 다음 주소입니다. 제너레이터, 제어 주소 레지스터, 제어 메모리 및 제어 데이터 레지스터.

제어 장치의 기능 다음을 포함하십시오.

<울>이 디자인은 두 가지 제어 장치를 사용하여 수행할 수 있습니다. 다음을 포함합니다.

<울>유선 제어 장치의 기본 설계는 위에 나와 있습니다. 이 유형에서 제어 신호는 회로 구조의 변경 없이 특수 하드웨어 논리 회로에 의해 생성됩니다. 이 때 생성된 신호는 프로세서에서 실행되도록 수정할 수 없습니다.

연산 코드의 기본 데이터(명령의 연산 코드는 디코딩을 위해 명령어 디코더로 전송됩니다. 명령어 디코더는 연산 코드에서 다양한 유형의 데이터를 디코딩하기 위한 디코더 세트입니다. 이는 활성 신호 값을 포함하는 출력 신호를 생성합니다. 컴퓨터 프로세서에 의한 프로그램 실행을 위한 제어 신호를 생성하기 위해 매트릭스 생성기에 대한 입력으로 제공됩니다.

매트릭스 생성기는 제어 장치의 상태와 프로세서에서 나오는 신호(인터럽트 신호)를 제공합니다. Matrix는 프로그래밍 가능한 논리 어레이로 구축됩니다. 행렬 생성기에서 생성된 제어 신호는 다음 생성기 행렬의 입력으로 주어지며 직사각형 패턴을 포함하는 타이밍 유닛의 타이밍 신호와 결합됩니다.

새로운 명령어를 가져오기 위해 컨트롤 유닛은 새로운 명령어를 실행하기 위한 초기 단계가 된다. 제어 장치는 타이밍 신호, 입력 신호 및 컴퓨터의 명령 상태가 변경되지 않는 한 초기 단계 또는 첫 번째 단계에 남아 있습니다. 생성된 신호 중 하나라도 변경되면 제어 장치의 상태 변경이 발생할 수 있습니다.

외부 신호 또는 인터럽트가 발생하면 제어 장치는 다음 상태로 이동하여 인터럽트 신호의 처리를 수행합니다. 플래그와 상태는 명령의 실행 주기를 수행하기 위해 원하는 상태를 선택하는 데 사용됩니다.

마지막 상태에서 제어 장치는 다음 명령어를 가져와서 프로그램 카운터, 메모리 주소 레지스터, 버퍼 레지스터, 명령어 레지스터로 출력을 전송하여 명령어를 읽습니다. 마지막으로 제어 장치가 가져온 마지막 명령이 종료 명령이면 프로세서의 작동 상태로 이동하여 사용자가 다음 프로그램을 지시할 때까지 기다립니다.

이 유형에서 제어 저장소는 프로그램 실행 중에 인코딩된 제어 신호를 저장하는 데 사용됩니다. 마이크로 프로그램이 주소 필드를 제어 저장소에 저장하기 때문에 제어 신호가 즉시 생성되지 않고 디코딩됩니다. 전체 프로세스는 단일 레벨입니다.

마이크로 연산은 프로그램에서 마이크로 명령어를 실행하기 위해 수행됩니다. 마이크로 프로그래밍된 제어 장치의 블록 다이어그램은 위에 나와 있습니다. 다이어그램에서 마이크로 명령어의 주소는 제어 메모리 주소 레지스터에서 가져옵니다. 제어 장치의 모든 정보는 ROM이라는 제어 메모리에 영구적으로 저장됩니다.

제어 메모리의 마이크로 명령은 제어 레지스터에 의해 유지됩니다. 마이크로 명령어는 데이터 처리를 위해 1개 이상의 마이크로 연산을 수행해야 하는 제어 단어(바이너리 제어 값 포함) 형태이기 때문입니다.

마이크로 명령어를 실행하는 동안 다음 주소 생성기는 마이크로 명령어의 다음 주소를 계산한 다음 제어 주소 레지스터로 보내 다음 마이크로 명령어를 읽습니다.

마이크로 명령어의 마이크로 연산 순서 -프로그램은 다음 주소 생성기에 의해 수행되고 시퀀스 주소를 가져오는 마이크로프로그램 시퀀서 역할을 합니다. 즉, 제어 메모리에서 읽습니다.

Control Unit의 Verilog 코드는 아래와 같습니다.

`"prj_definition.v" 포함

모듈 CONTROL_UNIT(MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, REP, MEM_READ, MEM_WRITE, RF_DATA_R1, RF_DATA_R2)

// 출력 신호

// 레지스터 파일에 대한 출력

출력 [`DATA_INDEX_LIMIT:0] RF_DATA_W;

출력 [`ADDRESS_INDEX_LIMIT:0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2;

출력 RF_READ, RF_WRITE;

// ALU용 출력

출력 [`DATA_INDEX_LIMIT:0] ALU_OP1, ALU_OP2;

출력 [`ALU_OPRN_INDEX_LIMIT:0] ALU_OPRN;

// 메모리용 출력

출력 [`ADDRESS_INDEX_LIMIT:0] MEM_ADDR;

출력 MEM_READ, MEM_WRITE;

// 입력 신호

입력 [`DATA_INDEX_LIMIT:0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT;

ZERO, CLK, RST 입력;

// 입력 신호

입력 [`DATA_INDEX_LIMIT:0] MEM_DATA;

// 상태 네트

wire [2:0] proc_state;

//프로그램 카운터 값, 현재 명령어 저장, 스택 포인터 레지스터

reg MEM_READ, MEM_WRITE;

reg MEM_ADDR;

reg ALU_OP1, ALU_OP2;

reg ALU_OPRN;

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2;

reg RF_DATA_W;

reg [1:0] 상태, next_state;

PROC_SM state_machine(.STATE(proc_state),.CLK(CLK),.RST(RST));

항상 @ (posge CLK)

시작

if (RST)

상태 <=RST;

else

상태 <=next_state;

끝

항상 @(상태)

시작

MEM_READ =1'b0; MEM_WRITE =1'b0; MEM_ADDR =1'b0;

ALU_OP1 =1'b0; ALU_OP2 =1'b0; ALU_OPRN =1'b0;

RF_ADDR_R1 =1'b0; RF_ADDR_R2 =1'b0; RF_ADDR_W =1'b0; RF_DATA_W =1'b0;

케이스( 상태 )

`PROC_FETCH :시작

next_state =`PROC_DECODE;

MEM_READ =1'b1;

RF_ADDR_R1 =1'b0; RF_ADDR_R2 =1'b0;

RF_ADDR_W =1'b1;

끝

`PROC_DECODE :시작

next_state =`PROC_EXE;

MEM_ADDR =1'b1;

ALU_OP1 =1'b1; ALU_OP2 =1'b1; ALU_OPRN =1'b1;

MEM_WRITE =1'b1;

RF_ADDR_R1 =1'b1; RF_ADDR_R2 =1'b1;

끝

`PROC_EXE :시작

next_state =`PROC_MEM;

ALU_OP1 =1'b1; ALU_OP2 =1'b1; ALU_OPRN =1'b1;

RF_ADDR_R1 =1'b0;

끝

`PROC_MEM:시작

next_state =`PROC_WB;

MEM_READ =1'b1; MEM_WRITE =1'b0;

끝

`PROC_WB:시작

next_state =`PROC_FETCH;

MEM_READ =1'b1; MEM_WRITE =1'b0;

끝

종료

끝

endmodule;

모듈 PROC_SM(STATE,CLK,RST);

// 입력 목록

입력 CLK, RST;

// 출력 목록

출력 [2:0] STATE;

// 리스트 입력

CLK, RST 입력;

// 리스트 출력

STATE 출력;

reg [2:0] STATE;

reg [1:0] state;

reg [1:0] next_state;

reg PC_REG, INST_REG, SP_REF;

`define PROC_FETCH 3'h0

`define PROC_DECODE 3'h1

`define PROC_EXE 3'h2

`define PROC_MEM 3'h3

`define PROC_WB 3'h4

// 상태 시작

초기

begin

state =2'bxx;

next_state =`PROC_FETCH;

end

// 리셋 신호 처리

항상 @ (posedge RST)

begin

state =`PROC_FETCH;

next_state =`PROC_FETCH;

end

항상 @ ( 포즈 CLK)

시작

상태 =next_state;

끝

항상 @(상태)

시작

if (상태 ===`PROC_FETCH)

시작

next_state =`PROC_DECODE;

print_instruction(INST_REG);

종료

if (상태 ===`PROC_DECODE)

시작

next_state =`PROC_EXE;

끝

if (상태 ===`PROC_EXE)

시작

next_state =`PROC_MEM;

print_instruction(SP_REF);

종료

if (상태 ===`PROC_MEM)

시작

next_state =`PROC_WB;

끝

if (상태 ===`PROC_WB)

시작

next_state =`PROC_FETCH;

print_instruction(PC_REG);

종료

종료

작업 인쇄 명령;

입력 [`DATA_INDEX_LIMIT:0] inst;

reg [5:0] opcode;

reg [4:0] rs;

reg [4:0] rt;

reg [4:0] rd;

reg [ 4:0] 샴; reg [5:0] 기능; reg [15:0] 즉시; reg [25:0] 주소;

시작

// 명령어 파싱

// R-type

{opcode, rs, rt, rd, shamt, 기능} =inst;

// I-유형

{opcode, rs, rt, 즉시 } =inst;

// J-type

{opcode, address} =inst;

$write(“ @ %6dns -> [0X%08h] “, $time, inst);

case(opcode) // R-Type

6'h00 :시작

case(함수)

6'h20:$write("r[%02d], r[%02d], r[%02d];", rs, rt, rd 추가);

6'h22:$write("서브 r [%02d], r[%02d], r[%02d];”, rs, rt, rd);

6'h2c:$write("mul r[%02d], r[%02d] , r[%02d];", rs, rt, rd);

6'h24:$write("및 r[%02d], r[%02d], r[%02d];", rs , rt, rd);

6'h25:$write("또는 r[%02d], r[%02d], r[%02d];", rs, rt, rd);

6'h27:$write("r[%02d], r[%02d], r[%02d];", rs, rt, rd);

6'h2a:$write("slt r [%02d], r[%02d], r[%02d];”, rs, rt, rd);

6'h00:$write(“sll r[%02d], %2d, r[ %02d];", rs, shamt, rd);

6'h02:$write("srl r[%02d], 0X%02h, r[%02d];", rs, shamt, rd);

6'h08:$write(“jr r[%02d];”, rs);

기본값:$write(“”);

endcase

end

// I형

6'h08 :$write("추가 r[%02d], r[%02d], 0X%04h;", rs, rt, 즉시);

6'h1d :$write("멀리 r[% 02d], r[%02d], 0X%04h;", rs, rt, 즉시);

6'h0c :$write("andi r[%02d], r[%02d], 0X%04h;", rs, rt, 즉시);

6'h0d :$write("ori r[%02d], r[%02d], 0X%04h;", rs, rt, 즉시);

6'h0f :$write(“루이 r[%02d], 0X%04h;”, rt, 즉시);

6'h0a :$write(“슬티 r[%02d], r[% 02d], 0X%04h;", rs, rt, 즉시);

6'h04 :$write("beq r[%02d], r[%02d], 0X%04h;", rs, rt , 즉시);

6'h05 :$write("bne r[%02d], r[%02d], 0X%04h;", rs, rt, 즉시);

6'h23 :$write("lw r[%02d], r[%02d], 0X%04h;", rs, rt, 즉시);

6'h2b :$write("sw r[%02d], r [%02d], 0X%04h;”, rs, rt, 즉시);

// J형

6'h02 :$write(“jmp 0X%07h;”, 주소);

6'h03 :$write(“jal 0X%07h;”, 주소);

6'h1b :$write (“푸시;”);

6'h1c :$write(“팝;”);

기본값:$write(“”);

endcase

$write(“ \n”);

끝

endtask

모듈 끝;

1). 제어 장치의 작업은 무엇입니까?

제어 장치의 작업은 컴퓨터 프로세서에 의한 실행을 위한 데이터 또는 명령의 흐름을 지시하는 것입니다. 메인 메모리, ALU, 레지스터, 입력 및 출력 장치를 제어, 관리 및 조정합니다. 명령을 가져오고 실행을 위한 제어 신호를 생성합니다.

2). 제어 메모리란 무엇입니까?

제어 메모리는 일반적으로 제어 레지스터의 주소와 데이터를 저장하는 RAM 또는 ROM입니다.

3). Wilkes 제어 장치는 무엇입니까?

유선 제어 장치의 순차 및 조합 회로는 Wilkes 제어 장치로 대체됩니다. 저장 장치를 사용하여 마이크로 프로그램의 명령 시퀀스를 저장합니다.

4). 유선 제어 장치란 무엇입니까?

유선 제어 장치는 회로의 물리적 변경 없이 모든 클록 펄스에서 한 상태에서 다른 상태로 변경하여 제어 신호를 생성합니다. 제어 신호의 생성은 명령어 레지스터, 디코더 및 인터럽트 신호에 따라 다릅니다.

5). 제어 메모리란 무엇입니까?

제어 장치의 정보나 데이터는 제어 메모리에 일시적 또는 영구적으로 저장됩니다.

제어 메모리에는 두 가지 유형이 있습니다. RAM(Random Access Memory)과 ROM(Read-Only Memory)이 있습니다.

따라서 이것은 제어 장치의 정의, 구성 요소, 디자인, 다이어그램, 기능 및 유형에 관한 모든 것입니다. 다음은 "제어 주소 레지스터의 목적은 무엇입니까?"입니다.

임베디드

전체론적 설계는 설계되는 시스템을 더 큰 것의 일부인 상호 연결된 전체로 간주하는 설계 접근 방식입니다. 전체론적 개념은 건축뿐만 아니라 기계 장치의 설계, 공간 배치 등에 적용될 수 있습니다. 이러한 디자인 접근 방식은 종종 환경에 대한 우려를 포함하며, 전체적인 디자이너는 디자인이 환경에 미치는 영향을 고려하고 디자인에서 환경 영향을 줄이려고 시도합니다. 미학은 또한 전체적인 디자인에서 중요한 고려 사항이 될 수 있습니다. 디자이너는 사람들이 디자인을 보는 다양한 방식에 대해 생각하면서 디자인이 전체적으로 어떻게 보일지 고려할

유압 동력 장치는 유압 유체의 에너지를 기계적 동력으로 변환하는 기계입니다. 광업, 건설, 석유 및 가스 추출, 선박 추진 및 농업 관개와 같은 산업에서 널리 사용됩니다. 유압 동력 장치는 유압 유체의 압력을 기계적 동력으로 변환하는 펌프, 밸브 및 기타 기계로 구성됩니다. 이 힘은 물체를 움직이거나 기어를 돌리는 데 사용할 수 있습니다. 유압 동력 장치는 다양한 산업 분야의 기계 또는 장치에 동력을 공급하는 데 사용할 수 있습니다. 광업, 건설, 석유 및 가스 추출, 선박 추진 및 농업용 관개에 자주 사용됩니다. 수력 장치 작