임베디드

편집자 주:스마트 제품 설계를 위한 고급 알고리즘이 계속 등장함에 따라 개발자는 종종 이러한 알고리즘의 관련 처리 요구를 충족할 수 있는 임베디드 시스템을 구현하는 데 어려움을 겪고 있습니다. FPGA는 필요한 성능을 제공할 수 있지만 FPGA를 사용한 설계는 오랫동안 FPGA 프로그래밍 전문가의 범위에 국한된 것으로 여겨져 왔습니다. 그러나 오늘날에는 더욱 강력한 FPGA와 보다 효과적인 개발 환경을 이용할 수 있게 되면서 FPGA 개발에 폭넓게 접근할 수 있게 되었습니다. Architecting High-Performance Embedded Systems 책의 4장에서 발췌한 내용에서 저자는 FPGA 디바이스, 구현 언어, FPGA 개발 프로세스에 대한 포괄적인 검토와 FPGA 구현을 시작하는 방법에 대한 자세한 설명을 제공합니다. 설계. 전체 발췌 내용은 다음 시리즈로 제공됩니다.

편집자 주:스마트 제품 설계를 위한 고급 알고리즘이 계속 등장함에 따라 개발자는 종종 이러한 알고리즘의 관련 처리 요구를 충족할 수 있는 임베디드 시스템을 구현하는 데 어려움을 겪고 있습니다. FPGA는 필요한 성능을 제공할 수 있지만 FPGA를 사용한 설계는 오랫동안 FPGA 프로그래밍 전문가의 범위에 국한된 것으로 여겨져 왔습니다. 그러나 오늘날에는 더욱 강력한 FPGA와 보다 효과적인 개발 환경을 이용할 수 있게 되면서 FPGA 개발에 폭넓게 접근할 수 있게 되었습니다. Architecting High-Performance Embedded Systems 책의 4장에서 발췌한 내용에서 저자는 FPGA 디바이스, 구현 언어, FPGA 개발 프로세스에 대한 포괄적인 검토와 FPGA 구현을 시작하는 방법에 대한 자세한 설명을 제공합니다. 설계. 전체 발췌 내용은 다음 시리즈로 제공됩니다.

1:하드웨어 리소스

2:구현 언어

3:개발 프로세스

4:프로젝트 구축(이 문서)

5:구현

Jim Ledin의 Architecting High-Performance Embedded Systems에서 각색

첫 FPGA 프로젝트 개발

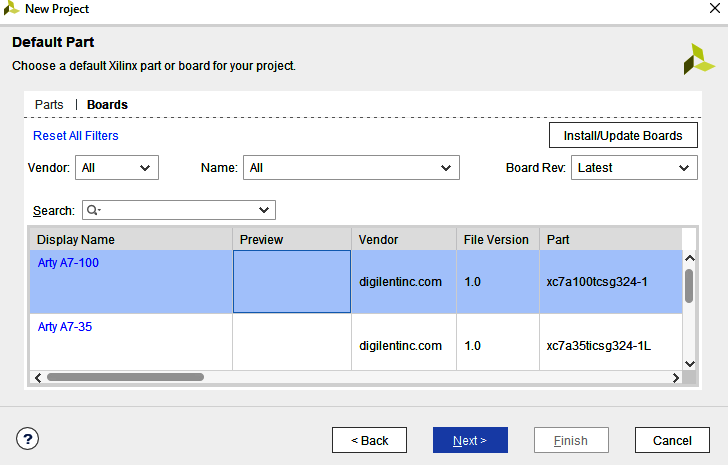

이 섹션에서는 Digilent Arty A7 개발 보드에 설치된 Xilinx Artix-7 FPGA 장치를 사용하여 간단하지만 완전한 프로젝트를 개발하고 구현합니다. 이 보드는 모델 번호가 -35T로 끝나는 저렴한 버전(US $129)과 -100T로 끝나는 모델 번호가 있는 더 기능이 있지만 더 비싼 버전(US $249)의 두 가지 변형으로 제공됩니다. 두 보드의 유일한 차이점은 보드에 설치된 Artix-7 FPGA 모델입니다. 예상대로 -35T는 -100T보다 사용 가능한 리소스가 적습니다.

이 프로젝트에 -35T 또는 -100T 변형을 사용할 수 있습니다. 개발 프로세스의 유일한 차이점은 필요할 때마다 올바른 보드 모델을 지정하는 것입니다. 그러나 이후 장에서는 예시 디지털 오실로스코프 프로젝트 설계의 리소스 요구 사항으로 인해 -100T 변형이 필요하므로 더 성능이 좋은 보드를 권장합니다.

Arty A7 보드는 https://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/ 및 Amazon과 같은 다른 출처에서 구입할 수 있습니다.

이 프로젝트의 목적을 위해 관심 있는 보드의 리소스는 FPGA 장치 자체뿐만 아니라 4개의 스위치, 4개의 푸시버튼 및 5개의 LED입니다. 이 프로젝트는 Vivado 도구 모음을 설치하고, 프로젝트를 만들고, HDL 코드를 입력하고, 코드를 테스트하고, 궁극적으로 비트스트림을 생성하고 보드에 다운로드하는 방법을 보여줍니다. 비트스트림을 보드에 다운로드한 후 시스템 작동을 수동으로 테스트할 수 있습니다. 또한 FPGA 이미지를 Arty A7 보드의 플래시 메모리에 프로그래밍하여 보드 전원을 켤 때마다 로드 및 실행되도록 하는 방법도 볼 수 있습니다.

프로젝트 설명

이 프로젝트는 FPGA에서 4비트 바이너리 가산기를 구현합니다. 여기에서는 복잡한 HDL 모델을 구현하는 것이 아니라 도구를 설정하고 사용하는 방법을 배우는 데 중점을 두고 있기 때문에 이것은 의도적으로 매우 단순한 디자인입니다.

보드에 있는 4개의 스위치는 하나의 4비트 2진수를 나타내고 4개의 푸시버튼은 또 다른 4비트 숫자를 나타냅니다. FPGA 로직은 이 두 숫자 사이에 계속해서 더하기 연산을 수행하고 캐리 비트를 나타내는 다섯 번째 LED와 함께 4개의 LED에 4비트 이진수로 결과를 표시합니다.

4비트 가산기 코드는 하드웨어 설계 언어에 설명된 단일 비트 전가산기 회로를 기반으로 합니다. 1장 섹션 , 고성능 임베디드 시스템 설계 .

Vivado 도구 설치

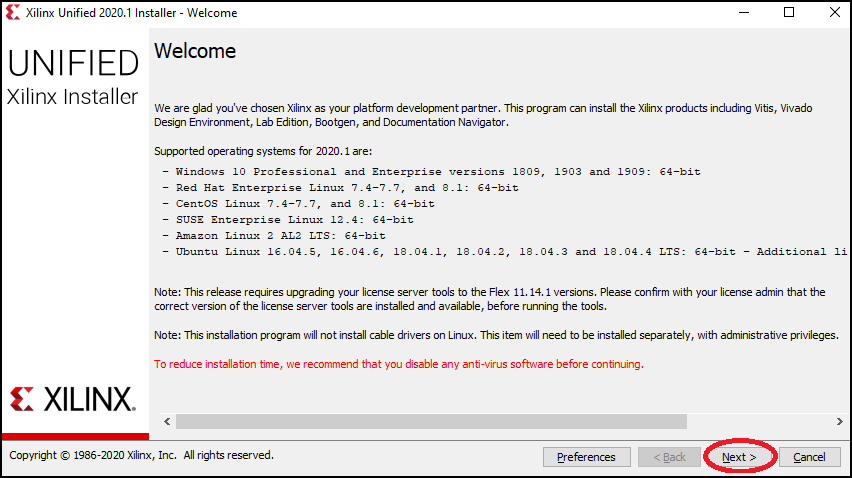

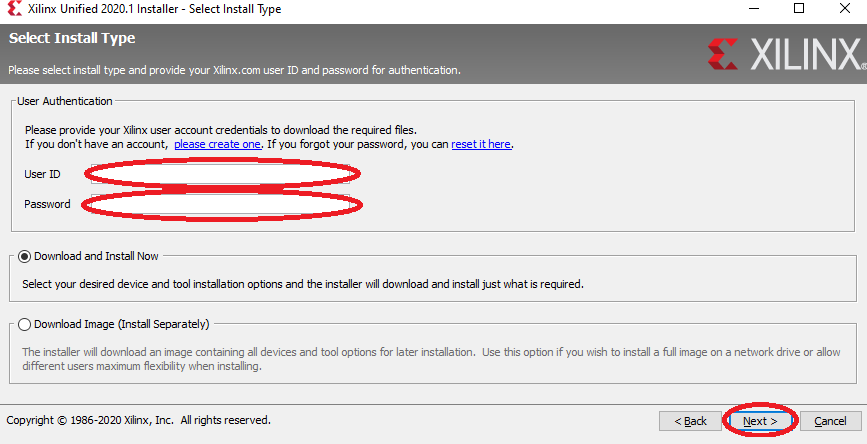

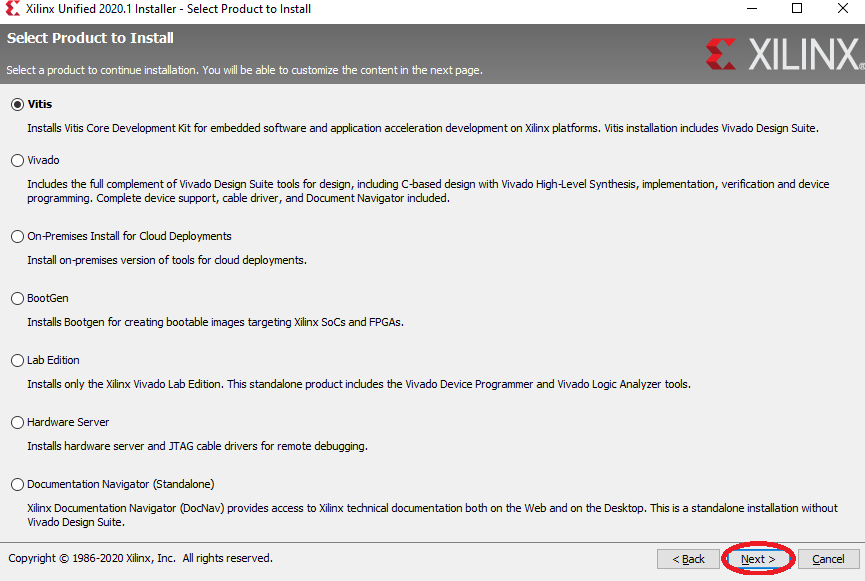

우리는 이 프로젝트와 향후 챕터의 프로젝트에 Xilinx Vivado FPGA 개발 도구 제품군을 사용할 것입니다. 이러한 도구는 무료로 제공되며 Windows 및 Linux 운영 체제에서 지원됩니다. 두 운영 체제 중 하나에 도구를 설치할 수 있습니다. 이 섹션의 설명은 Windows 버전의 도구를 다루지만 Linux에 설치하는 경우 차이점이 분명해야 합니다. Vivado 도구로 작업하는 것은 서로 다른 운영 체제에서 거의 동일해야 합니다.

<올>

그림 4.3 – 설치 프로그램 시작 대화 상자

그림 4.4 – 설치 프로그램 로그인 대화 상자

그림 4.5 – 설치 프로그램 제품 선택 대화 상자

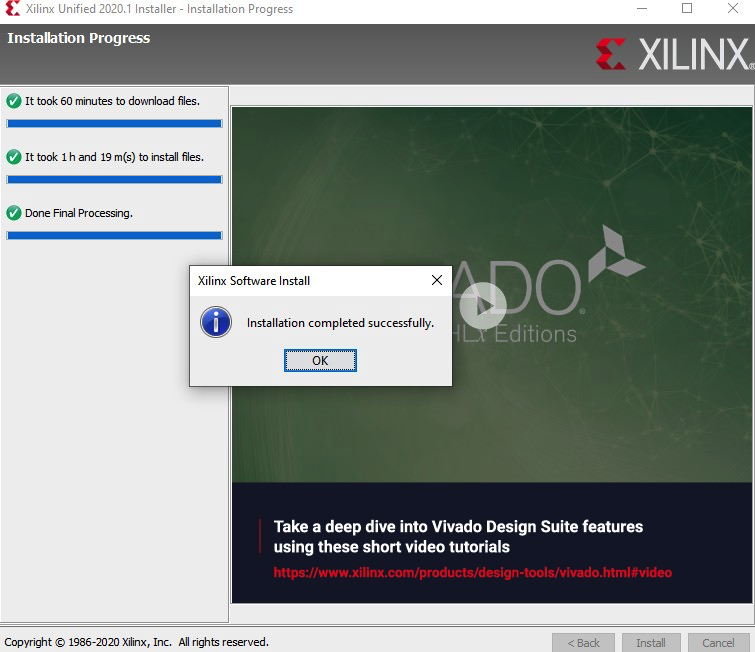

그림 4.6 – 설치 완료 대화 상자

설치가 완료되면 다음으로 첫 번째 프로젝트를 생성합니다.

프로젝트 만들기

Arty A7 보드용 4비트 바이너리 가산기 프로젝트를 만들고 빌드하려면 다음 단계를 따르세요.

<올>

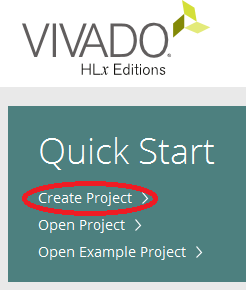

그림 4.7 – Vivado 빠른 시작 대화 상자

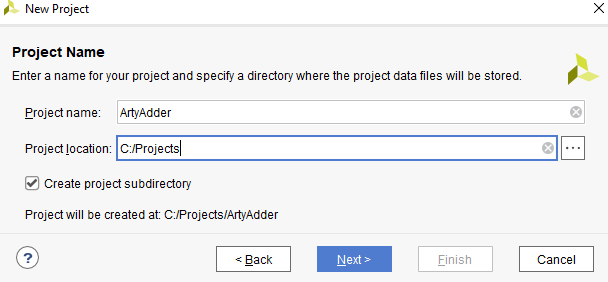

그림 4.8 – 프로젝트 이름 대화 상자

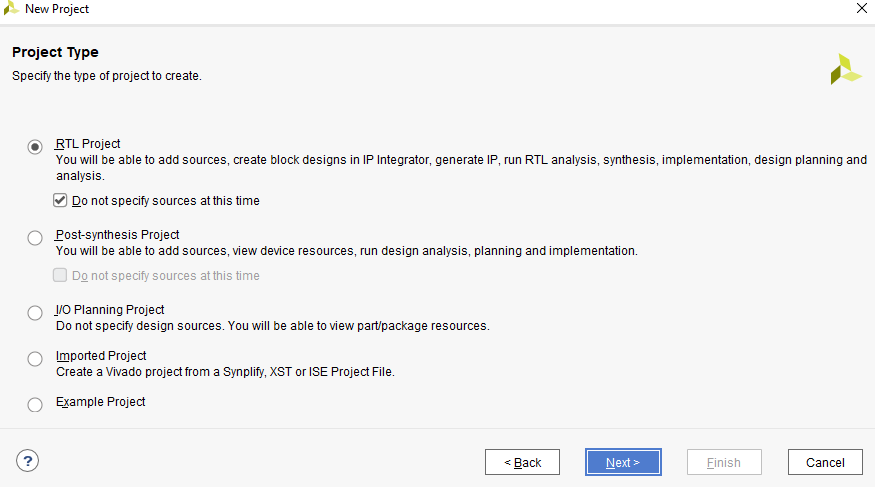

그림 4.9 – 프로젝트 유형 대화 상자

그림 4.10 – 기본 부품 대화 상자

이제 빈 프로젝트를 만들었습니다. 다음 섹션에서는 이 프로젝트에 대한 논리 회로 설계를 포함하는 VHDL 소스 파일을 생성합니다.

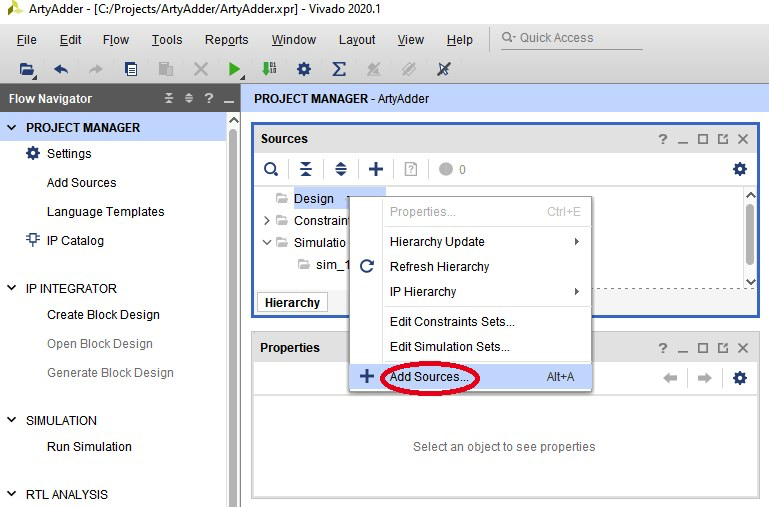

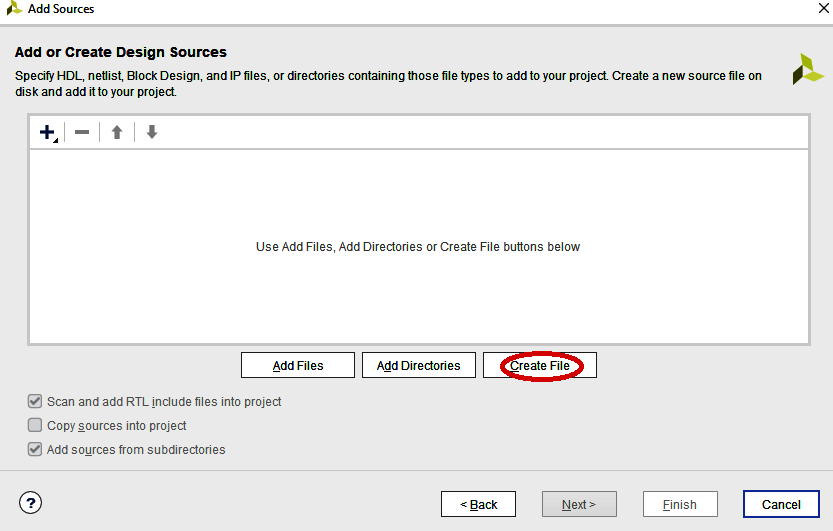

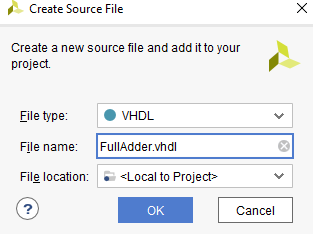

VHDL 소스 파일 만들기

다음 단계는 VHDL 소스 파일 생성, 소스 코드 입력, FPGA 디자인 컴파일 과정을 설명합니다.

<올>

그림 4.11 – 소스 추가… 메뉴 선택

그림 4.12 – 디자인 소스 추가 또는 만들기 대화 상자

그림 4.13 – 소스 파일 만들기 대화 상자

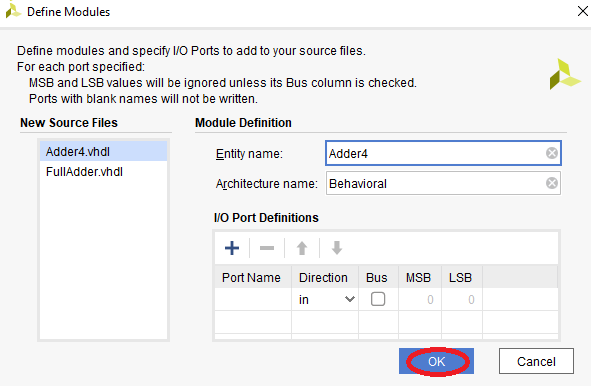

그림 4.14 – 모듈 정의 대화 상자

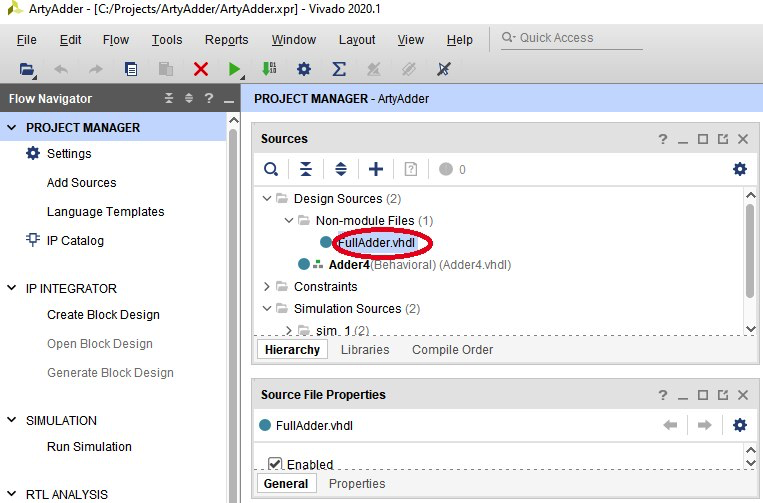

그림 4.15 – 새로 생성된 소스 파일

-- IEEE 표준 라이브러리 라이브러리를 로드합니다. IEEE.STD_LOGIC_1164.ALL 사용;-- 전체 가산기 입력 및 출력 엔티티 정의 FULL_ADDER는 포트( A:std_logic, B:std_logic, C_IN:std_logic, S:std_logic, C_OUT:std_logic _FULL 출력), 엔터티 종료 -- FULL_ADDER isbegin S <=(A XOR B) XOR C_IN의 전체 추가 아키텍처 BEHAVIORAL의 동작을 정의합니다. C_OUT <=(A AND B) OR ((A XOR B) AND C_IN);종료 아키텍처 BEHAVIORAL;

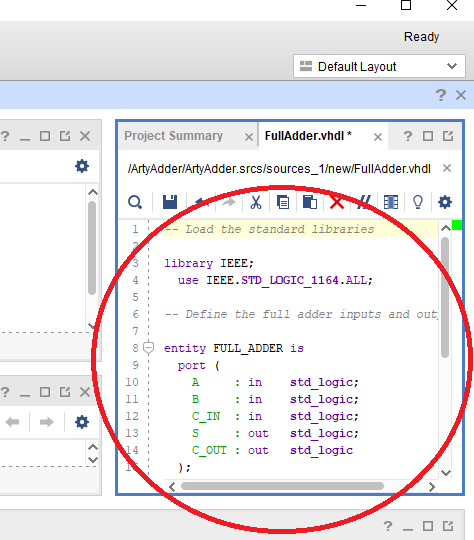

이것은 하드웨어 디자인 언어 에서 조사한 것과 동일한 단일 비트 전가산기 코드입니다. 1장, 고성능 임베디드 시스템 설계 섹션 . 그림 4.16 Vivado 편집기 창에 코드 표시:

그림 4.16 – FullAdder.vhdl 소스 코드

-- IEEE 표준 라이브러리 라이브러리를 로드합니다. IEEE.STD_LOGIC_1164.ALL 사용;-- 4비트 가산기 입력 및 출력 항목 정의 ADDER4는 포트입니다( A4:in std_logic_vector(3 downto 0); B4:in std_logic_vector(3 downto 0); SUM4:out std_logic_vector(3 downto0). ); C_OUT4:out std_logic );end entity ADDER4;-- ADDER4의 BEHAVIORAL 4비트 가산기 아키텍처의 동작 정의 -- 전체 가산기 구성 요소의 이전 정의 참조 FULL_ADDER는 포트( A:std_logic, B:in std_logic, C_IN:std_logic에서, S:std_logic에서, C_OUT:std_logic에서 ); 최종 구성 요소; -- 4비트 가산기 신호에서 내부적으로 사용되는 신호 정의 c0, c1, c2 :std_logic;begin -- 첫 번째 가산기에 대한 캐리 입력이 0으로 설정됨 FULL_ADDER0 :FULL_ADDER 포트 맵( A => A4(0), B => B4(0), C_IN => '0', S => SUM4(0), C_OUT => c0 ); FULL_ADDER1 :FULL_ADDER 포트 맵 ( A => A4(1), B => B4(1), C_IN => c0, S => SUM4(1), C_OUT => c1 ); FULL_ADDER2 :FULL_ADDER 포트 맵 ( A => A4(2), B => B4(2), C_IN => c1, S => SUM4(2), C_OUT => c2 ); FULL_ADDER3 :FULL_ADDER 포트 맵 ( A => A4(3), B => B4(3), C_IN => c2, S => SUM4(3), C_OUT => C_OUT4 ); 아키텍처 종료 BEHAVIORAL;

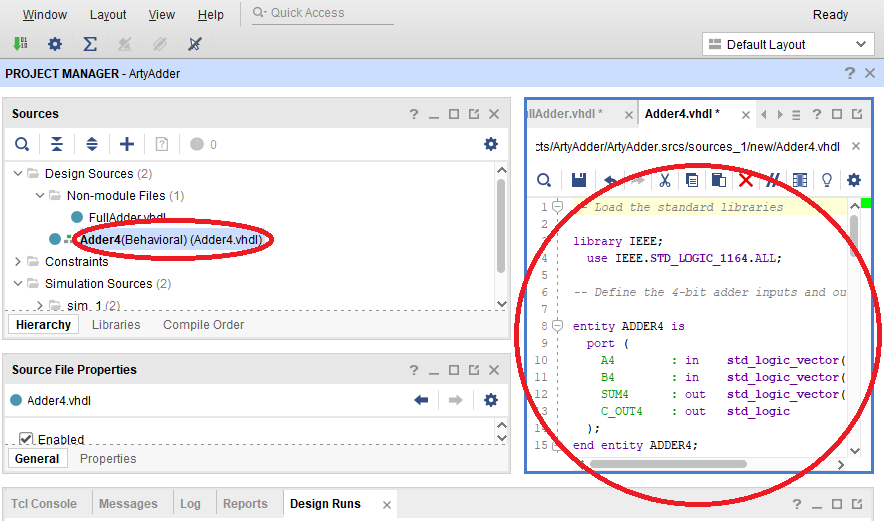

이 코드는 단일 비트 전가산기의 복사본 4개를 인스턴스화합니다. 최하위 가산기로의 캐리는 0으로 설정되고 각 가산기의 캐리는 다음 최상위 가산기로 파급됩니다. 두 개의 4비트 숫자를 더한 결과는 4비트 결과와 단일 비트 캐리가 됩니다.

그림 4.17 – Adder4.vhdl 소스 코드

다음 기사에서는 디자인을 테스트하고 Arty 보드에 대한 디자인을 구현하는 방법을 보여줍니다.

Packt Publishing의 허가를 받아 재인쇄했습니다. 저작권 © 2021 팩트 퍼블리싱

짐 레딘 Ledin Engineering, Inc.의 CEO입니다. Jim은 임베디드 소프트웨어 및 하드웨어 설계, 개발 및 테스트 전문가입니다. 그는 또한 임베디드 시스템 사이버 보안 평가 및 침투 테스트를 수행합니다. 그는 학사 학위가 있습니다. Iowa State University에서 항공우주 공학 학위 및 M.S. Georgia Institute of Technology에서 전기 및 컴퓨터 공학 학위를 취득했습니다. Jim은 캘리포니아에 등록된 전문 전기 엔지니어이자 CISSP(공인 정보 시스템 보안 전문가), CEH(공인 윤리 해커) 및 CPT(공인 침투 테스터)입니다.

짐 레딘 Ledin Engineering, Inc.의 CEO입니다. Jim은 임베디드 소프트웨어 및 하드웨어 설계, 개발 및 테스트 전문가입니다. 그는 또한 임베디드 시스템 사이버 보안 평가 및 침투 테스트를 수행합니다. 그는 학사 학위가 있습니다. Iowa State University에서 항공우주 공학 학위 및 M.S. Georgia Institute of Technology에서 전기 및 컴퓨터 공학 학위를 취득했습니다. Jim은 캘리포니아에 등록된 전문 전기 엔지니어이자 CISSP(공인 정보 시스템 보안 전문가), CEH(공인 윤리 해커) 및 CPT(공인 침투 테스터)입니다. 관련 콘텐츠:

더 많은 Embedded를 보려면 Embedded의 주간 이메일 뉴스레터를 구독하세요.

임베디드

OrCAD는 회로 시뮬레이션 및 PCB 설계 솔루션을 제공하는 가장 인기 있는 프리미엄 설계 소프트웨어 중 하나입니다. 그러나 이 문서에서는 DC 회로 설계에 사용되는 소프트웨어인 OrCAD를 소개합니다. 이는 세 가지 일반적인 응용 프로그램으로 구성됩니다. 먼저 화면에 코스를 그리는 데 사용하는 캡처가 있습니다. Capture는 표준 종이 및 연필 드로잉과 비교할 때 많은 유연성을 제공합니다. 둘째, PSpice는 캡처된 회로를 시뮬레이션하고 마지막으로 PCB Editor를 시뮬레이션하여 작동합니다. PCB Editor는 PCB

워키토키나 오디오 앰프를 사용해 본 적이 있습니까? 아니면 FM/AM 대역에서 다른 대역으로 전환하여 취미로 라디오 청취를 하고 있습니까? 예를 들어, 일부 일반적인 애플리케이션은 AM 수신기 회로를 사용합니다. 또한 일반적으로 무선 시스템의 필수 구성 요소입니다. 그래서 오늘은 간단한 AM 라디오 수신기 회로를 구성하는 방법과 방법을 소개합니다. 1. AM 수신기란 무엇입니까? 먼저 AM은 진폭 변조를 나타냅니다. 데이터 전송에 사용되는 전자 통신 전략입니다. 종종 가장 많이 사용되는 전송 매체는 무선 반송파입니다. 그러나