산업기술

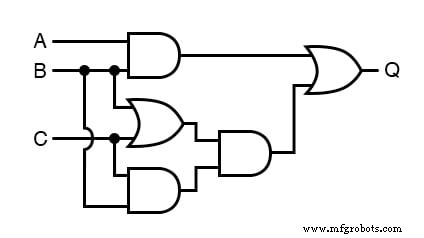

단순화가 필요한 반도체 게이트 회로부터 시작하겠습니다.

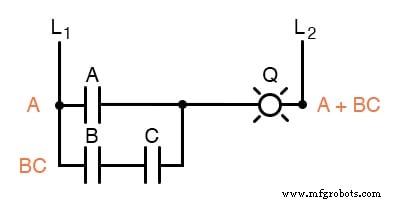

"A", "B" 및 "C" 입력 신호는 스위치, 센서 또는 기타 게이트 회로에서 제공되는 것으로 가정합니다.

이러한 신호가 발생하는 위치는 게이트 감소 작업에서 문제가 되지 않습니다.

단순화의 첫 번째 단계는 이 회로에 대한 부울 표현식을 작성하는 것입니다.

이 작업은 각 게이트의 각 입력 신호에 해당하는 각 게이트의 출력에 하위 표현식을 작성하는 것으로 시작하면 단계별로 쉽게 수행됩니다.

OR 게이트는 부울 덧셈과 같고 AND 게이트는 부울 곱셈과 같습니다.

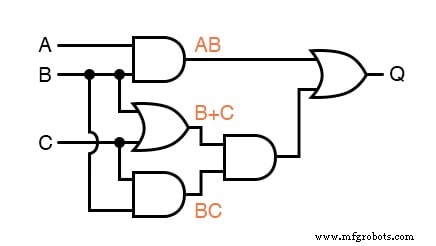

예를 들어, 처음 세 게이트의 출력에 하위 표현식을 작성하겠습니다.

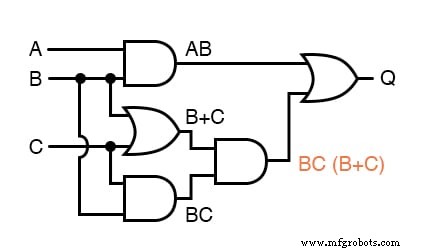

. . . 다음 게이트에 대한 또 다른 하위 표현:

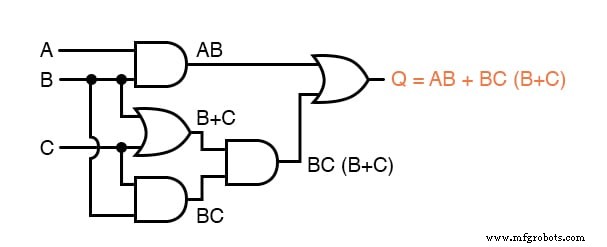

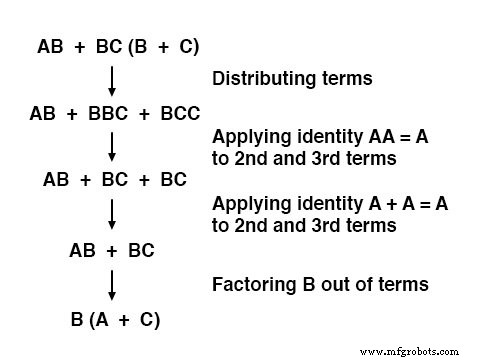

마지막으로 출력("Q")은 AB + BC(B + C) 표현식과 같은 것으로 보입니다.

이제 작업할 부울 표현식이 있으므로 부울 대수 규칙을 적용하여 표현식을 가장 단순한 형태로 줄여야 합니다.

최종 표현식인 B(A + C)는 원래보다 훨씬 간단하지만 동일한 기능을 수행합니다.

이것을 확인하려면 두 식에 대한 진리표를 생성하고 두 회로에 대해 A, B, C의 8가지 논리 상태 조합 모두에 대한 Q의 상태(회로의 출력)를 결정할 수 있습니다. 두 진리표는 동일해야 합니다.

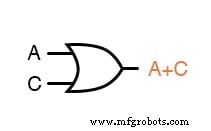

이제 이 부울 표현식에서 도식 다이어그램을 생성해야 합니다.

이렇게 하려면 적절한 수학적 연산 순서(덧셈 전에 곱하기, 다른 것보다 먼저 괄호 안에 연산)에 따라 표현식을 평가하고 각 단계에 대한 게이트를 그립니다.

OR 게이트는 부울 더하기와 같고 AND 게이트는 부울 곱하기와 같습니다.

이 경우 OR 게이트인 하위 표현식 "A + C"로 시작합니다.

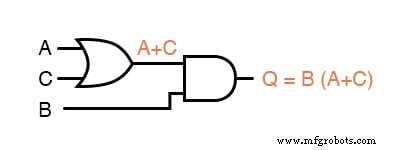

"B(A + C)" 식을 평가하는 다음 단계는 신호 B를 이전 게이트(A + C)의 출력으로 곱하는 것입니다(AND 게이트).

분명히 이 회로는 5개가 아닌 2개의 논리 게이트만 있는 원본보다 훨씬 간단합니다.

이러한 부품 감소는 더 높은 작동 속도(입력 신호 전환에서 출력 신호 전환까지의 지연 시간 감소), 더 적은 전력 소비, 더 적은 비용 및 더 높은 신뢰성을 초래합니다.

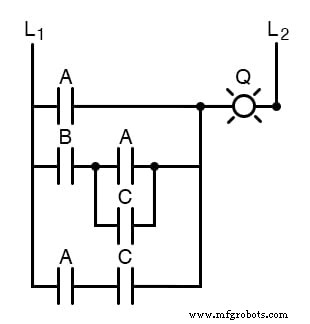

일반적으로 속도가 느리고 작동에 더 많은 전력을 소비하고 비용이 더 많이 들고 평균 수명이 짧은 전자 기계 릴레이 회로는 부울 단순화의 이점을 크게 얻습니다. 회로의 예를 살펴보겠습니다.

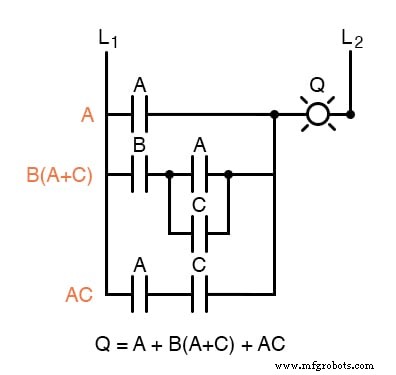

이전과 마찬가지로 이 회로를 가장 단순한 형태로 줄이는 첫 번째 단계는 회로도에서 부울 표현식을 개발하는 것입니다.

이를 수행하는 가장 쉬운 방법은 직렬 병렬 저항 네트워크를 단일 전체 저항으로 줄이기 위해 일반적으로 수행하는 것과 동일한 단계를 따르는 것입니다.

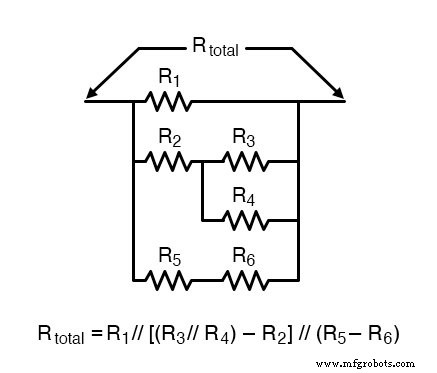

예를 들어, 이전 회로의 릴레이 접점과 동일한 연결 패턴으로 배열된 저항과 해당하는 총 저항 공식을 사용하여 다음 저항 네트워크를 조사합니다.

위 그림에서 긴 대시 기호(-)는 저항의 직렬 연결을 나타냅니다.

병렬 접점은 부울 덧셈과 같고 직렬 접점은 부울 곱셈과 같습니다.

직렬 병렬 저항 네트워크를 전체 저항으로 줄이는 것과 동일한 우선 순위에 따라 이 릴레이 접점 회로에 대한 부울 식을 작성하십시오.

표현식 작성을 구성하는 데 도움이 되도록 각 래더 "렁"의 왼쪽에 부울 하위 표현식을 작성하는 것이 도움이 될 수 있습니다.

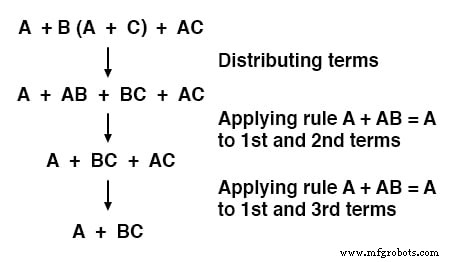

이제 작업할 부울 표현식이 있으므로 부울 대수 규칙을 적용하여 표현식을 가장 단순한 형태로 줄여야 합니다(가장 간단한 것은 구현하는 데 가장 적은 릴레이 접점이 필요한 것으로 정의됨).

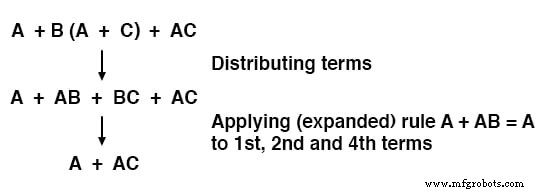

수학적으로 더 많은 경향이 있는 사람은 "A + AB =A" 규칙을 사용하는 두 단계가 단일 단계로 결합될 수 있고 규칙은 "A + AB + AC + AD +"로 확장될 수 있음을 알 수 있어야 합니다. . . =아”

보시다시피 축소된 회로는 원본보다 훨씬 간단하지만 동일한 논리 기능을 수행합니다.

검토:

<울>

관련 워크시트:

<울>산업기술

비정현파, 반복 파형이 서로 다른 주파수의 일련의 사인파와 동일하다는 원리는 일반적으로 파동의 기본 속성이며 AC 회로 연구에서 실용적으로 매우 중요합니다. 이는 완벽한 사인파 모양이 아닌 파형이 있을 때마다 문제의 회로가 마치 동시에 여러 주파수 전압 배열이 적용된 것처럼 반응한다는 것을 의미합니다. AC 회로가 혼합된 주파수로 구성된 소스 전압을 받을 때 해당 회로의 구성 요소는 각 구성 주파수에 다른 방식으로 응답합니다. 커패시터 또는 인덕터와 같은 반응성 구성요소는 회로에 존재하는 각각의 모든 주파수에 고유한 임피던스 양

차단기 크기를 계산하는 방법은 무엇입니까? 해결된 예가 있는 차단기 크기 계산기 NEC에 따라 (National Electric Code), IEC (International Electrotechnical Commission) 및 IEEE (Institute of Electrical and Electronics Engineers), 감전, 위험한 화재 및 연결된 전기 장비 및 가전 제품의 보호를 방지하기 위해 주거용 배선 및 산업 또는 상업용 설치와 같은 모든 전기 회로에 적절한 크기의 회로 차단기가 있어야 합니다. 전기 기계의 최