verilog

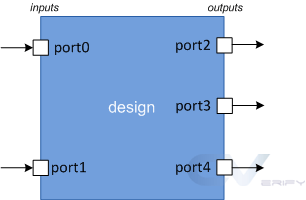

포트는 특정 모듈에 대한 입력 및 출력 역할을 하는 신호 세트이며 모듈과 통신하는 기본 방법입니다. 모듈을 PCB에 배치된 가공된 칩으로 생각하면 칩과 통신하는 유일한 방법은 핀을 통해서라는 것이 매우 분명해집니다. 포트는 핀과 같으며 설계에서 외부 세계와 신호를 주고받는 데 사용됩니다.

<노스크립트>

| 포트 | 설명 |

|---|---|

| 입력 | 디자인 모듈은 input을 사용하여 외부에서만 값을 받을 수 있습니다. 포트 |

| 출력 | 디자인 모듈은 output을 사용하여 외부로 값을 보낼 수만 있습니다. 포트 |

| 인아웃 | 디자인 모듈은 inout를 사용하여 값을 보내거나 받을 수 있습니다. 포트 |

포트는 기본적으로 wire 유형의 네트로 간주됩니다. .

inout로 선언된 포트 입력 및 출력 모두로 작동할 수 있습니다.

input [net_type] [range] list_of_names; // Input port

inout [net_type] [range] list_of_names; // Input & Output port

output [net_type] [range] list_of_names; // Output port driven by a wire

output [var_type] [range] list_of_names; // Output port driven by a variable

아래 표시된 코드에는 세 개의 input가 있습니다. 포트, 하나의 output 포트 및 하나의 inout 포트.

module my_design ( input wire clk,

input en,

input rw,

inout [15:0] data,

output int );

// Design behavior as Verilog code

endmodule

동일한 이름을 사용하는 것은 불법입니다. 다중 포트용.

input aport; // First declaration - valid

input aport; // Error - already declared

output aport; // Error - already declared

signed 속성은 포트 선언이나 net/reg 선언 또는 둘 다에 첨부될 수 있습니다. 암시적 네트는 기본적으로 서명되지 않음입니다. .

module ( input a,

b,

output c);

// ports a, b, and c are by default unsigned

endmodule

net/reg 선언에 signed이 있는 경우 속성이면 다른 쪽도 서명된 것으로 간주됩니다.

module ( input signed a, b,

output c);

wire a, b; // a, b are signed from port declaration

reg signed c; // c is signed from reg declaration

endmodule

Verilog는 몇 번의 수정을 거쳤고 1995년의 원래 IEEE 버전은 다음과 같은 포트 선언 방식을 가지고 있었습니다. 여기서 모듈 선언은 먼저 대괄호 안에 포트 이름을 나열한 다음 나중에 모듈 본문 내에서 정의된 해당 포트의 방향을 나열해야 했습니다.

module test (a, b, c);

input [7:0] a; // inputs "a" and "b" are wires

input [7:0] b;

output [7:0] c; // output "c" by default is a wire

// Still, you can declare them again as wires to avoid confusion

wire [7:0] a;

wire [7:0] b;

wire [7:0] c;

endmodule

module test (a, b, c);

input [7:0] a, b;

output [7:0] c; // By default c is of type wire

// port "c" is changed to a reg type

reg [7:0] c;

endmodule

ANSI-C 스타일의 포트 이름 지정은 2001년에 도입되었으며 포트 목록 내에서 유형을 지정할 수 있게 되었습니다.

module test ( input [7:0] a,

b, // "b" is considered an 8-bit input

output [7:0] c);

// Design content

endmodule

module test ( input wire [7:0] a,

input wire [7:0] b,

output reg [7:0] c);

// Design content

endmodule

포트 선언에 네트 또는 변수 유형이 포함된 경우 해당 포트는 완전히 선언된 것으로 간주됩니다. net 또는 변수 유형 선언에서 동일한 포트를 다시 선언하는 것은 불법입니다.

module test ( input [7:0] a, // a, e are implicitly declared of type wire

output reg [7:0] e );

wire signed [7:0] a; // illegal - declaration of a is already complete -> simulator dependent

wire [7:0] e; // illegal - declaration of e is already complete

// Rest of the design code

endmodule

포트 선언에 net 또는 변수 형식이 포함되지 않은 경우 net 또는 변수 형식 선언에서 다시 포트를 선언할 수 있습니다.

module test ( input [7:0] a,

output [7:0] e);

reg [7:0] e; // Okay - net_type was not declared before

// Rest of the design code

endmodule

verilog

먹스 또는 멀티플렉서란 무엇입니까? 멀티플렉서 또는 mux 요컨대 선택 신호를 기반으로 N 입력 중 하나에서 출력으로 데이터를 전송하는 디지털 요소입니다. 아래에 표시된 경우는 N이 4인 경우입니다. 예를 들어, 4비트 멀티플렉서는 선택 신호를 사용하여 각 입력을 출력으로 전송할 수 있는 4비트 각각의 N 입력을 갖습니다. sel은 2비트 입력이며 4개의 값을 가질 수 있습니다. 선택 라인의 각 값은 입력 중 하나를 출력 핀 아웃으로 보낼 수 있도록 합니다. sel a b c d out

디자인 module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe ); reg [