verilog

for 루프는 소프트웨어에서 가장 널리 사용되는 루프이지만 주로 복제하는 데 사용됩니다. Verilog의 하드웨어 로직. for 뒤에 숨겨진 아이디어 루프는 주어진 조건이 참인 한 루프 내에서 주어진 명령문 세트를 반복하는 것입니다. 이것은 while와 매우 유사합니다. 루프이지만 반복자를 사용할 수 있고 조건이 이 반복자의 값에 따라 달라지는 컨텍스트에서 더 많이 사용됩니다.

for (<initial_condition>; <condition>; <step_assignment>) begin

// Statements

end

키워드 for 이 유형의 루프를 지정하는 데 사용되며 세 부분으로 구성됩니다.

초기 조건 및 제어 변수에 대한 업데이트는 for에 포함됩니다. 루프이며 while와 달리 별도로 지정할 필요가 없습니다. 고리. while 루프는 보다 일반적인 목적으로 주어진 조건만큼 주어진 명령문이 반복되어야 하는 경우에만 주로 사용됩니다. 그러나 for 루프는 일반적으로 단계 변수에 의해 제어되는 명확한 시작과 끝을 가지고 있습니다.

다음은 for 루프의 사용법을 보여주는 간단한 예입니다.

module my_design;

integer i;

initial begin

// Note that ++ operator does not exist in Verilog !

for (i = 0; i < 10; i = i + 1) begin

$display ("Current loop#%0d ", i);

end

end

endmodule

시뮬레이션 로그 ncsim> run Current loop#0 Current loop#1 Current loop#2 Current loop#3 Current loop#4 Current loop#5 Current loop#6 Current loop#7 Current loop#8 Current loop#9 ncsim: *W,RNQUIE: Simulation is complete.

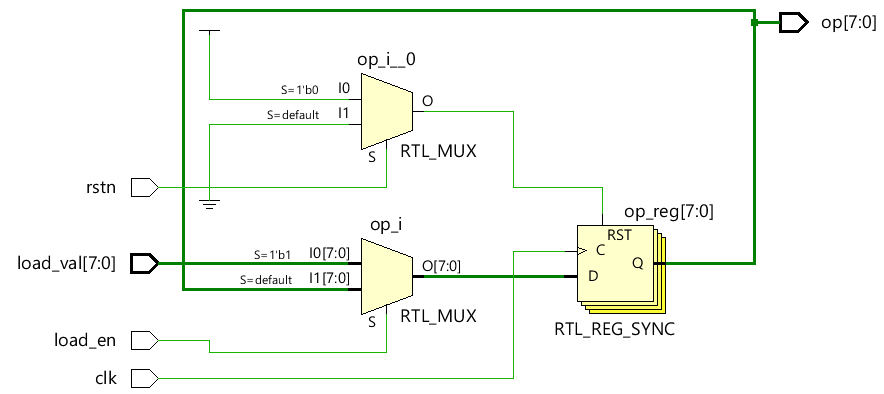

for 없이 Verilog에서 8비트 왼쪽 시프트 레지스터를 구현하는 방법을 살펴보겠습니다. 루프를 만든 다음 for을 사용하여 코드와 비교합니다. 루프 구조의 유용성을 높이 평가하기 위한 루프입니다.

module lshift_reg (input clk, // Clock input

input rstn, // Active low reset input

input [7:0] load_val, // Load value

input load_en, // Load enable

output reg [7:0] op); // Output register value

// At posedge of clock, if reset is low set output to 0

// If reset is high, load new value to op if load_en=1

// If reset is high, and load_en=0 shift register to left

always @ (posedge clk) begin

if (!rstn) begin

op <= 0;

end else begin

if (load_en) begin

op <= load_val;

end else begin

op[0] <= op[7];

op[1] <= op[0];

op[2] <= op[1];

op[3] <= op[2];

op[4] <= op[3];

op[5] <= op[4];

op[6] <= op[5];

op[7] <= op[6];

end

end

end

endmodule

for를 사용하여 동일한 동작을 구현할 수 있습니다. 코드를 줄이고 다양한 레지스터 너비에 맞게 확장할 수 있는 루프입니다. 레지스터의 너비를 Verilog 매개변수로 하면 디자인 모듈이 확장 가능해지고 for 내부에서 동일한 매개변수를 사용할 수 있습니다. 루프.

module lshift_reg (input clk, // Clock input

input rstn, // Active low reset input

input [7:0] load_val, // Load value

input load_en, // Load enable

output reg [7:0] op); // Output register value

integer i;

// At posedge of clock, if reset is low set output to 0

// If reset is high, load new value to op if load_en=1

// If reset is high, and load_en=0 shift register to left

always @ (posedge clk) begin

if (!rstn) begin

op <= 0;

end else begin

// If load_en is 1, load the value to op

// else keep shifting for every clock

if (load_en) begin

op <= load_val;

end else begin

for (i = 0; i < 8; i = i + 1) begin

op[i+1] <= op[i];

end

op[0] <= op[7];

end

end

end

endmodule

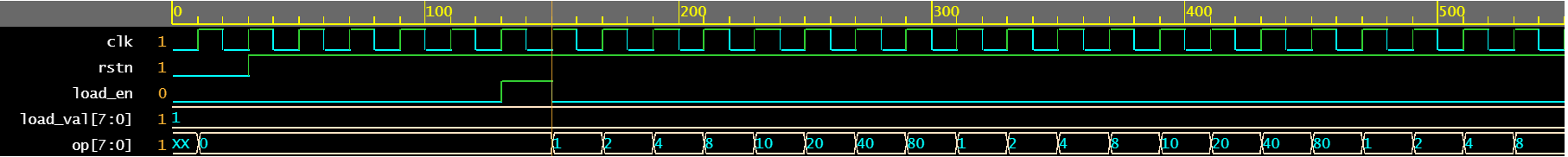

테스트벤치 코드는 아래와 같으며 디자인을 인스턴스화합니다.

module tb;

reg clk;

reg rstn;

reg [7:0] load_val;

reg load_en;

wire [7:0] op;

// Setup DUT clock

always #10 clk = ~clk;

// Instantiate the design

lshift_reg u0 ( .clk(clk),

.rstn (rstn),

.load_val (load_val),

.load_en (load_en),

.op (op));

initial begin

// 1. Initialize testbench variables

clk <= 0;

rstn <= 0;

load_val <= 8'h01;

load_en <= 0;

// 2. Apply reset to the design

repeat (2) @ (posedge clk);

rstn <= 1;

repeat (5) @ (posedge clk);

// 3. Set load_en for 1 clk so that load_val is loaded

load_en <= 1;

repeat(1) @ (posedge clk);

load_en <= 0;

// 4. Let design run for 20 clocks and then finish

repeat (20) @ (posedge clk);

$finish;

end

endmodule

<노스크립트>  <노스크립트>

<노스크립트>

verilog

매개변수는 다른 사양으로 모듈을 재사용할 수 있도록 하는 Verilog 구성입니다. 예를 들어, 4비트 가산기는 비트 수에 대한 값을 허용하도록 매개변수화될 수 있으며 모듈 인스턴스화 중에 새 매개변수 값이 전달될 수 있습니다. 따라서 N비트 가산기는 4비트, 8비트 또는 16비트 가산기가 될 수 있습니다. 함수 호출 중에 전달되는 함수에 대한 인수와 같습니다. parameter MSB = 7; // MSB is a parameter with a constant value 7 paramet

Verilog는 하드웨어 설명 언어이며 설계자가 RTL 설계를 시뮬레이션하여 논리 게이트로 변환할 필요가 없습니다. 시뮬레이션이 필요한 이유는 무엇입니까? 시뮬레이션은 RTL 코드가 의도한 대로 동작하는지 확인하기 위해 다른 시간에 다른 입력 자극을 설계에 적용하는 기술입니다. 기본적으로 시뮬레이션은 설계의 견고성을 검증하기 위해 잘 따라야 하는 기술입니다. 또한 가공된 칩이 실제 세계에서 사용되는 방식과 다양한 입력에 반응하는 방식과 유사합니다. 예를 들어, 위의 디자인은 출력 pe 보여진 바와 같이. 시뮬레이션을 통해